64-Kbit (8 K  $\times$  8) Serial (I<sup>2</sup>C) nvSRAM

# Features

- 64-Kbit nonvolatile static random access memory (nvSRAM)

□ Internally organized as 8 K × 8

- STORE to QuantumTrap nonvolatile elements initiated automatically on power-down (AutoStore) or by using I<sup>2</sup>C command (Software STORE)

- □ RECALL to SRAM initiated on power-up (Power-Up RECALL) or by I<sup>2</sup>C command (Software RECALL)

- Automatic STORE on power-down with a small capacitor (except for CY14MX064J1A)

- High reliability

- □ Infinite read, write, and RECALL cycles

- □ 1 million STORE cycles to QuantumTrap

- □ Data retention: 20 years at 85 °C

- High speed I<sup>2</sup>C interface<sup>[1]</sup>

- □ Industry standard 100 kHz and 400 kHz speed

- Fast-mode Plus: 1 MHz speed

- High speed: 3.4 MHz

- Zero cycle delay reads and writes

- Write protection

- □ Hardware protection using Write Protect (WP) pin □ Software block protection for 1/4, 1/2, or entire array

- I<sup>2</sup>C access to special functions

- Nonvolatile STORE/RECALL

- □ 8 byte serial number

- Manufacturer ID and Product ID

- Sleep mode

- Low power consumption

- □ Average active current of 1 mA at 3.4-MHz operation

- Average standby mode current of 120 µA

- $\square$  Sleep mode current of 8  $\mu A$

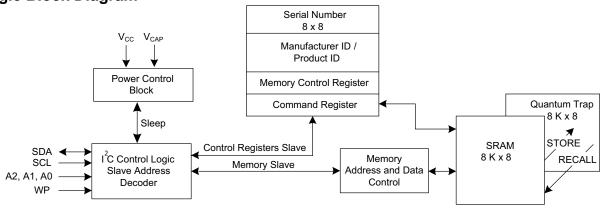

# Logic Block Diagram

- Industry standard configurations

- Operating voltages:

- CY14MB064J:  $V_{CC}$  = 2.7 V to 3.6 V

- CY14ME064J:  $V_{CC}$  = 4.5 V to 5.5 V

- Industrial temperature

- □ 8-pin small outline integrated circuit (SOIC) package

- □ Restriction of hazardous substances (RoHS) compliant

# Overview

The Cypress CY14MX064J combines a 64-Kbit nvSRAM<sup>[2]</sup> with a nonvolatile element in each memory cell. The memory is organized as 8 K words of 8 bits each. The embedded nonvolatile elements incorporate the QuantumTrap technology, creating the world's most reliable nonvolatile memory. The SRAM provides infinite read and write cycles, while the QuantumTrap cells provide highly reliable nonvolatile storage of data. Data transfers from SRAM to the nonvolatile elements (STORE operation) takes place automatically at power-down (except for CY14MX064J1A). On power-up, data is restored to the SRAM from the nonvolatile memory (RECALL operation). The STORE and RECALL operations can also be initiated by the user through I<sup>2</sup>C commands.

# Configuration

| Feature            | CY14MX064J1A | CY14MX064J2A |

|--------------------|--------------|--------------|

| AutoStore          | No           | Yes          |

| Software STORE     | Yes          | Yes          |

| Slave Address pins | A2, A1, A0   | A2, A1       |

#### Notes

- The I<sup>2</sup>C nvSRAM is a single solution which is usable for all four speed modes of operation. As a result, some I/O parameters are slightly different than those on chips which support only one mode of operation. Refer to AN87209 for more details.

- Serial (I<sup>2</sup>C) nvSRAM is referred to as nvSRAM throughout the datasheet.

Cypress Semiconductor Corporation Document Number: 001-70393 Rev. \*I 198 Champion Court

San Jose, CA 95134-1709

# Contents

| Pinout                                      | 3  |

|---------------------------------------------|----|

| Pin Definitions                             | 3  |

| I2C Interface                               | 4  |

| Protocol Overview                           | 4  |

| I2C Protocol – Data Transfer                | 4  |

| Data Validity                               | 5  |

| START Condition (S)                         |    |

| STOP Condition (P)                          | 5  |

| Repeated START (Sr)                         | 5  |

| Byte Format                                 | 5  |

| Acknowledge / No-acknowledge                | 5  |

| High Speed Mode (Hs-mode)                   | 6  |

| Slave Device Address                        | 6  |

| Write Protection (WP)                       | 9  |

| AutoStore Operation                         | 9  |

| Write Operation                             | 9  |

| Read Operation                              | 10 |

| Memory Slave Access                         | 10 |

| Control Registers Slave                     | 14 |

| Serial Number                               | 16 |

| Serial Number Write                         | 16 |

| Serial Number Lock                          | 16 |

| Serial Number Read                          | 16 |

| Device ID                                   | 17 |

| Executing Commands Using Command Register . | 17 |

|                                             |    |

| Maximum Ratings                         |    |

|-----------------------------------------|----|

| Operating Range                         |    |

| DC Electrical Characteristics           |    |

| Data Retention and Endurance            |    |

| Thermal Resistance                      | 19 |

| AC Test Loads and Waveforms             | 20 |

| AC Test Conditions                      | 20 |

| AC Switching Characteristics            |    |

| Switching Waveforms                     |    |

| nvSRAM Specifications                   |    |

| Switching Waveforms                     |    |

| Software Controlled STORE/RECALL Cycles |    |

| Switching Waveforms                     |    |

| Ordering Information                    | 24 |

| Ordering Code Definitions               |    |

| Package Diagrams                        |    |

| Acronyms                                |    |

| Document Conventions                    |    |

| Units of Measure                        |    |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      |    |

| Products                                |    |

| PSoC Solutions                          |    |

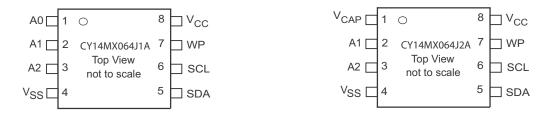

# Pinout

Figure 1. 8-pin SOIC pinout

# **Pin Definitions**

| Pin Name             | I/O Type     | Description                                                                                                                                                                                                                                 |

|----------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL                  | Input        | Clock. Runs at speeds up to a maximum of f <sub>SCL</sub> .                                                                                                                                                                                 |

| SDA                  | Input/Output | <ul> <li>I/O. Input/Output of data through I<sup>2</sup>C interface.</li> <li>Output: Is open-drain and requires an external pull-up resistor.</li> </ul>                                                                                   |

| WP                   |              | Write Protect. Protects the memory from all writes. This pin is internally pulled LOW and hence can be left open if not connected.                                                                                                          |

| A2-A0 <sup>[3]</sup> |              | Slave Address. Defines the slave address for I <sup>2</sup> C. This pin is internally pulled LOW and hence can be left open if not connected.                                                                                               |

| V <sub>CAP</sub>     |              | AutoStore Capacitor. Supplies power to the nvSRAM during power loss to STORE data from the SRAM to nonvolatile elements. If not required, AutoStore must be disabled and this pin left as no connect. It must never be connected to ground. |

| NC                   | No connect   | No Connect. This pin is not connected to the die.                                                                                                                                                                                           |

| V <sub>SS</sub>      | Power supply | Ground                                                                                                                                                                                                                                      |

| V <sub>CC</sub>      | Power supply | Power supply                                                                                                                                                                                                                                |

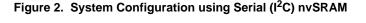

# I<sup>2</sup>C Interface

$I^2C$  bus consists of two lines – serial clock line (SCL) and serial data line (SDA) that carry information between multiple devices on the bus.  $I^2C$  supports multi-master and multi-slave configurations. The data is sent from the transmitter to the receiver on the SDA line and is synchronized with the clock SCL generated by the master.

The SCL and SDA lines are open-drain lines and are pulled up to V<sub>CC</sub> using resistors. The choice of pull-up resistor on the system depends on the bus capacitance and the intended speed of operation. The master generates the clock and all the data I/Os are transmitted in synchronization with this clock. The CY14MX064J supports up to 3.4-MHz clock speed on the SCL line.

### **Protocol Overview**

This device supports only a 7-bit addressable scheme. The master generates a START condition to initiate the communication followed by broadcasting a slave select byte. The slave select byte consists of a seven bit address of the <u>slave</u> that the master intends to communicate with and R/W bit indicating a read or a write operation. The selected slave responds to this with an acknowledgement (ACK). After a slave is selected, the remaining part of the communication takes place between the master and the selected slave device. The other devices on the bus ignore the signals on the SDA line until a STOP or Repeated START condition is detected. The data is transferred between the master and the selected slave device through the SDA pin synchronized with the SCL clock generated by the master.

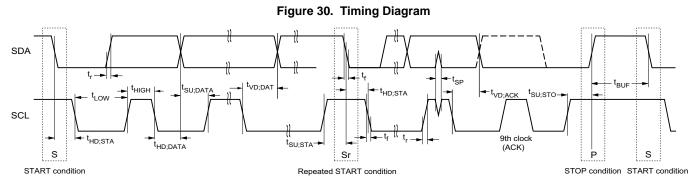

### I<sup>2</sup>C Protocol – Data Transfer

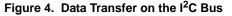

Each transaction in  $I^2C$  protocol starts with the master generating a START condition on the bus, followed by a seven-bit slave address and eighth bit (R/W) indicating a read (1)

or a write (0) operation. All signals are transmitted on the open-drain SDA line and are synchronized with the clock on SCL line. Each byte of data transmitted on the I<sup>2</sup>C bus is acknowledged by the receiver by holding the SDA line LOW on the ninth clock pulse. The request for write by the master is followed by the memory address and data bytes on the SDA line. The writes can be performed in burst-mode by sending multiple bytes of data. The memory address increments automatically after receiving/transmitting each byte on the falling edge of ninth clock cycle. The new address is latched just prior to sending/receiving the acknowledgment bit. This allows the next sequential byte to be accessed with no additional addressing. On reaching the last memory location, the address rolls back to 0x0000 and writes continue. The slave responds to each byte sent by the master during a write operation with an ACK. A write sequence can be terminated by the master generating a STOP or Repeated START condition.

A read request is performed at the current address location (address next to the last location accessed for read or write). The memory slave device responds to a read request by transmitting the data on the current address location to the master. A random address read may also be performed by first sending a write request with the intended address of read. The master must abort the write immediately after the last address byte and issue a Repeated START or STOP signal to prevent any write operation. The following read operation starts from this address. The master acknowledges the receipt of one byte of data by holding the SDA pin LOW for the ninth clock pulse. The reads can be terminated by the master sending a no-acknowledge (NACK) signal on the SDA line after the last data byte. The no-acknowledge signal causes the CY14MX064J to release the SDA line and the master can then generate a STOP or a Repeated START condition to initiate a new operation.

## **Data Validity**

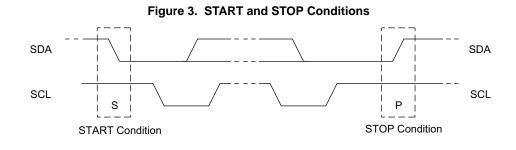

The data on the SDA line must be stable during the HIGH period of the clock. The state of the data line can only change when the clock on the SCL line is LOW for the data to be valid. There are only two conditions under which the SDA line may change state with the SCL line held HIGH, that is, START and STOP condition. The START and STOP conditions are generated by the master to signal the beginning and end of a communication sequence on the  $I^2C$  bus.

## START Condition (S)

A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition. Every transaction in  $I^2C$  begins with the master generating a START condition.

## **STOP Condition (P)**

A LOW to HIGH transition on the SDA line while SCL is HIGH indicates a STOP condition. This condition indicates the end of the ongoing transaction.

START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again after the STOP condition.

### Repeated START (Sr)

If an Repeated START condition is generated instead of a STOP condition the bus continues to be busy. The ongoing transaction on the  $I^2C$  lines is stopped and the bus waits for the master to send a slave ID for communication to restart.

### **Byte Format**

Each operation in  $l^2$ C is done using 8-bit words. The bits are sent in MSB first format on the SDA line and each byte is followed by an ACK signal by the receiver.

An operation continues until a NACK is sent by the receiver or STOP or Repeated START condition is generated by the master The SDA line must remain stable when the clock (SCL) is HIGH except for a START or STOP condition.

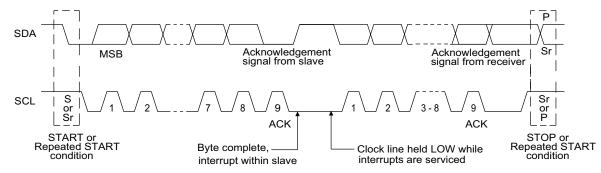

### Acknowledge / No-acknowledge

After transmitting one byte of data or address, the transmitter releases the SDA line. The receiver pulls the SDA line LOW to acknowledge the receipt of the byte. Every byte of data transferred on the I<sup>2</sup>C bus needs to be responded with an ACK signal by the receiver to continue the operation. Failing to do so is considered as a NACK state. NACK is the state where the

receiver does not acknowledge the receipt of data and the operation is aborted.

The master can generate NACK during a READ operation in the following cases:

- The master did not receive valid data due to noise

- The master generates a NACK to abort the READ sequence. After a NACK is issued by the master, the nvSRAM slave releases control of the SDA pin and the master is free to generate a Repeated START or STOP condition.

The nvSRAM slave can generate NACK during a WRITE operation in the following cases:

- nvSRAM did not receive valid data due to noise.

- The master tries to access write-protected locations on the nvSRAM. The master must restart the communication by generating a STOP or Repeated START condition.

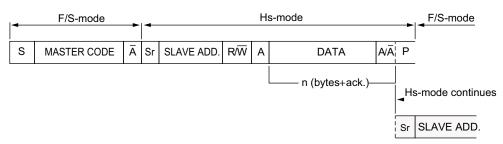

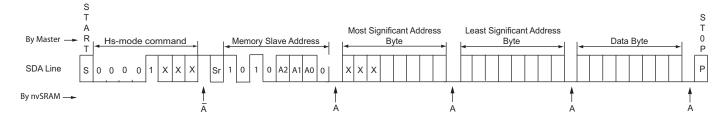

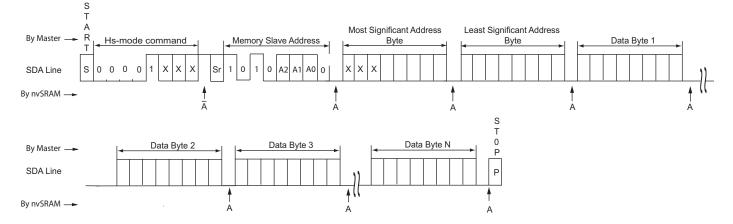

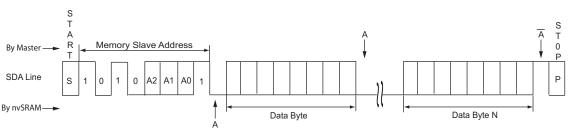

### High Speed Mode (Hs-mode)

In Hs-mode, nvSRAM can transfer data at bit rates of up to 3.4 Mbit/s. A master code (0000 1XXXb) must be issued to place the device in high-speed mode. This enables master/slave communication for a speed of up to 3.4 MHz. A stop condition exits Hs-mode.

#### Serial Data Format in Hs-mode

Serial data transfer format in Hs-mode meets the standard-mode I<sup>2</sup>C-bus specification. Hs-mode can only commence after the following conditions (all of which are in F/S-modes):

- 1. START condition (S)

- 2. 8-bit master code (0000 1XXXb)

- 3. No-acknowledge bit  $(\overline{A})$

#### Figure 6. Data transfer format in Hs-mode

Single and multiple-byte reads and writes are supported. After the device enters Hs-mode, data transfer continues in Hs-mode until the stop condition is sent by the master device. The slave switches back to F/S-mode after a STOP condition (P). To continue data transfer in Hs-mode, the master sends Repeated START (Sr).

See Figure 12 on page 11 and Figure 15 on page 12 for Hs-mode timings for read and write operation.

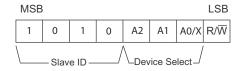

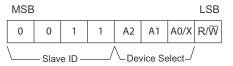

#### Slave Device Address

Every slave device on an  $I^2C$  bus has a device select address. The first byte after START condition contains the slave device address with which the master intends to communicate. The seven MSBs are the device address and the LSB (R/W bit) is used for indicating Read or Write operation. The CY14MX064J reserves two sets of upper 4 MSBs [7:4] in the slave device address field for accessing Memory and Control Registers. The accessing mechanism is described in Memory Slave Device on page 7.

The nvSRAM product provides two functionalities: Memory and Control Registers functions (such as serial number and product ID). The two functions of the device are accessed through different slave device addresses. The first four most significant bits [7:4] in the device address register are used to select between the nvSRAM functions.

Table 1. Slave device Addressing

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0 | nvSRAM Function<br>Select    | CY14MX064J Slave Devices                                                                                                           |

|-------|-------|-------|-------|-------|---------|-------|-------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1     | 0     | 1     | 0     | Devi  | ce Sele | ct ID | R/W   | Selects Memory               | Memory, 8 K × 8                                                                                                                    |

| 0     | 0     | 1     | 1     | Devi  | ce Sele | ct ID | R/W   | Selects Control<br>Registers | Control Registers<br>- Memory Control Register, 1 × 8<br>- Serial Number, 8 × 8<br>- Device ID, 4 × 8<br>- Command Register, 1 × 8 |

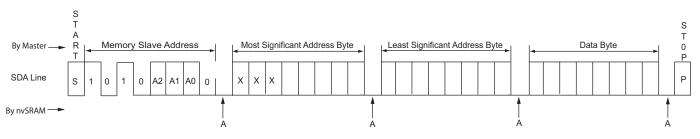

### Memory Slave Device

The nvSRAM device is selected for Read/Write if the master issues the slave address as 1010b followed by two/three bits of device select. For CY14MX064J1A, the device select is 3 bits and for CY14MX064J2A, it is two bits with the third bit set to don't care. If the slave address sent by the master matches the Memory Slave device address, then depending on the R/W bit of the slave address, data is either read from (R/W = '1') or written to (R/W = '0') the nvSRAM.

The address length for CY14MX064J is 13 bits and, therefore, it requires two address bytes to map the entire memory address location. The two dedicated address bytes represent bit A0 to A12. However, since the address is only 13 bits, it implies that the device ignores the first three MSB bits that are fed in. Although these bits are 'don't care', Cypress recommends that this bit is treated as 0 to enable seamless transition to higher memory densities.

### Figure 7. Memory Slave Device Address

### Control Registers Slave Device

The Control Registers Slave device includes the Serial Number, Product ID, Memory Control, and Command Register.

The nvSRAM Control Register Slave device is selected for Read/Write if the master issues the Slave address as 0011b followed by two/three bits of device select. For CY14MX064J1A, device select is 3 bits and for CY14MX064J2A, it is two bits with the third bit set to don't care. If the slave address sent by the master matches the Memory Slave device address, then depending on the R/W bit of the slave address, data is either read from (R/W = '1') or written to (R/W = '0') the nvSRAM.

#### Figure 8. Control Registers Slave Device Address

#### Table 2. Control Registers map

| Address | Description                   | Read/Write             | Details                                                                             |

|---------|-------------------------------|------------------------|-------------------------------------------------------------------------------------|

| 0x00    | Memory<br>Control<br>Register | Read/Write             | Contains Block Protect<br>Bits and Serial Number<br>Lock bit                        |

| 0x01    | Serial                        | Read/Write             | Programmable Serial                                                                 |

| 0x02    | Number 8                      | (Read only when SNL is | Number. Locked by                                                                   |

| 0x03    | Bytes                         | set)                   | setting the Serial<br>Number lock bit in the                                        |

| 0x04    |                               |                        | Memory Control                                                                      |

| 0x05    |                               |                        | Register to '1'.                                                                    |

| 0x06    |                               |                        |                                                                                     |

| 0x07    |                               |                        |                                                                                     |

| 0x08    |                               |                        |                                                                                     |

| 0x09    | Device ID                     | Read only              | Device ID is factory                                                                |

| 0x0A    |                               | programme              | programmed                                                                          |

| 0x0B    |                               |                        |                                                                                     |

| 0x0C    |                               |                        |                                                                                     |

| 0x0D    | Reserved                      | Reserved               | Reserved                                                                            |

| 0xAA    | Command<br>Register           | Write only             | Allows commands for<br>STORE, RECALL,<br>AutoStore<br>Enable/Disable, SLEEP<br>Mode |

#### Memory Control Register

The Memory Control Register contains the following bits:

#### Table 3. Memory Control Register Bits

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | SNL   | 0     | 0     | BP1   | BP0   | 0     | 0     |

|       | (0)   |       |       | (0)   | (0)   |       |       |

■ BP1:BP0: Block Protect bits are used to protect 1/4, 1/2, or full memory array. These bits can be written through a write instruction to the 0x00 location of the Control Register Slave device. However, any STORE cycle causes transfer of SRAM data to a nonvolatile cell, regardless of whether or not the block is protected. The default value shipped from the factory for BP0 and BP1 is '0'.

#### Table 4. Block Protection

| Level | BP1:BP0 | Block Protection |

|-------|---------|------------------|

| 0     | 00      | None             |

| 1/4   | 01      | 0x1800–0x1FFF    |

| 1/2   | 10      | 0x1000–0x1FFF    |

| 1     | 11      | 0x0000–0x1FFF    |

**SNL (S/N Lock) Bit**: Serial Number Lock bit (SNL) is used to lock the serial number. After the bit is set to '1', the serial number registers are locked and no modification is allowed. This bit cannot be cleared to '0'. The serial number is secured on the next STORE operation (Software STORE or AutoStore). If AutoStore is not enabled, the user must perform the Software STORE operation to secure the lock bit status. If a STORE was not performed, the serial number lock bit will not survive the power cycle. The default value shipped from the factory for SNL is '0'.

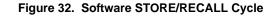

#### Command Register

The Command Register resides at address "AA" of the Control Registers Slave device. This is a write only register. The byte written to this register initiates a STORE, RECALL, AutoStore Enable, AutoStore Disable, and sleep mode operation as listed in Table 5. Refer to Serial Number on page 16 for details on how to execute a command register byte.

| Table 5. | Command | Register | bytes |

|----------|---------|----------|-------|

|----------|---------|----------|-------|

| Data Byte<br>[7:0] | Command | Description                                    |

|--------------------|---------|------------------------------------------------|

| 0011 1100          | STORE   | STORE SRAM data to nonvolatile memory          |

| 0110 0000          | RECALL  | RECALL data from nonvolatile<br>memory to SRAM |

| 0101 1001          | ASENB   | Enable AutoStore                               |

| 0001 1001          | ASDISB  | Disable AutoStore                              |

| 1011 1001          | SLEEP   | Enter Sleep Mode for low power consumption     |

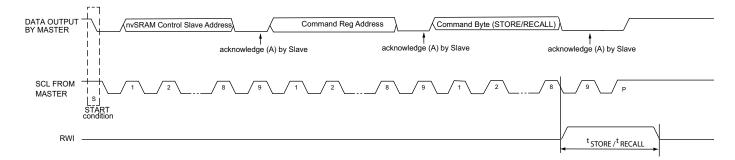

- STORE: Initiates nvSRAM Software STORE. The nvSRAM cannot be accessed for t<sub>STORE</sub> time after this instruction is executed. When initiated, the device performs a STORE operation, regardless of whether a write has been performed since the last NV operation. After the t<sub>STORE</sub> cycle time is completed, the SRAM is activated again for read/write operations.

- RECALL: Initiates nvSRAM Software RECALL. The nvSRAM cannot be accessed for t<sub>RECALL</sub> time after this instruction has been executed. The RECALL operation does not alter the data in the nonvolatile elements. A RECALL may be initiated in two ways: Hardware RECALL, initiated on power-up; and Software RECALL, initiated by a I<sup>2</sup>C RECALL instruction.

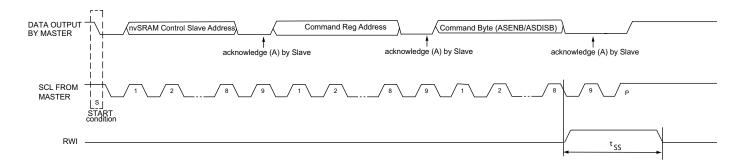

- ASENB: Enables nvSRAM AutoStore. The nvSRAM cannot be accessed for t<sub>SS</sub> time after this instruction has been executed. This setting is not nonvolatile and needs to be followed by a manual STORE sequence if this is desired to survive power cycle. The part comes from the factory with 'AutoStore Enabled' and '0x00' written in all cells.

- ASDISB: Disables nvSRAM AutoStore. The nvSRAM cannot be accessed for t<sub>SS</sub> time after this instruction has been executed. This setting is not nonvolatile and needs to be followed by a manual STORE sequence if this is desired to survive the power cycle.

**Note** If AutoStore is disabled and V<sub>CAP</sub> is not required, it is required that the V<sub>CAP</sub> pin is left open. The V<sub>CAP</sub> pin must never be connected to ground. Power-Up RECALL operation cannot be disabled in any case.

■ SLEEP: SLEEP instruction puts the nvSRAM in sleep mode. When the SLEEP instruction is registered, the nvSRAM takes t<sub>SS</sub> time to process the SLEEP request. After the SLEEP command is successfully registered and processed, the nvSRAM performs a STORE operation to secure the data to nonvolatile memory and then enters SLEEP mode. Whenever nvSRAM enters SLEEP mode, it initiates a nonvolatile STORE cycle, which results in losing an endurance cycle for every sleep command execution. A STORE cycle starts only if a write to the SRAM has been performed since the last STORE or RECALL cycle.

The nvSRAM enters sleep mode as follows:

- 1. The Master sends a START command

- The Master sends Control Registers Slave device ID with I<sup>2</sup>C Write bit set (R/W = '0')

- 3. The Slave (nvSRAM) sends an ACK back to the Master

- 4. The Master sends the Command Register address (0xAA)

- 5. The Slave (nvSRAM) sends an ACK back to the Master

- 6. The Master sends the Command Register byte for entering into Sleep mode

- 7. The Slave (nvSRAM) sends an ACK back to the Master

- 8. The Master generates a STOP condition.

Once in Sleep mode, the device starts consuming  $I_{ZZ}$  current  $t_{SLEEP}$  time after SLEEP instruction is registered. The device is not accessible for normal operations until it is out of sleep mode. The nvSRAM wakes up after  $t_{WAKE}$  duration after the device slave address is transmitted by the master.

Transmitting any of the two slave addresses wakes the nvSRAM from Sleep mode. The nvSRAM device is not accessible during  $t_{\text{SLEEP}}$  and  $t_{\text{WAKE}}$  interval, and any attempt to access the nvSRAM device by the master is ignored and nvSRAM sends NACK to the master. As an alternative method of determining when the device is ready, the master can send read or write commands and look for an ACK.

## Write Protection (WP)

The WP pin is an active high pin and protects entire memory and all registers from write operations. To inhibit all the write operations, this pin must be held high. When this pin is high, all memory and register writes are prohibited and the address counter is not incremented. This pin is internally pulled LOW and hence can be left open if not used.

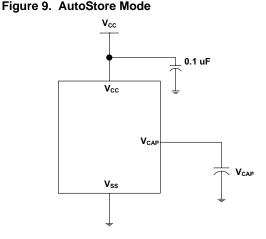

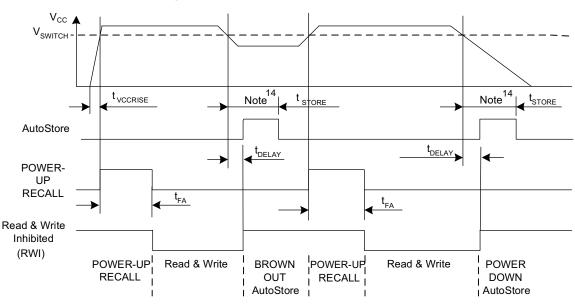

### AutoStore Operation

The AutoStore operation is a unique feature of nvSRAM, which automatically stores the SRAM data to QuantumTrap cells during power-down. This STORE uses an external capacitor ( $V_{CAP}$ ) and enables the device to safely STORE the data in the nonvolatile memory when power goes down.

During normal operation, the device draws current from V<sub>CC</sub> to charge the capacitor connected to the V<sub>CAP</sub> pin. When the voltage on the V<sub>CC</sub> pin drops below V<sub>SWITCH</sub> during power-down, the device inhibits all memory accesses to nvSRAM and automatically performs a conditional STORE operation using the charge from the V<sub>CAP</sub> capacitor. The AutoStore operation is not initiated if no write cycle has been performed since the last STORE or RECALL.

**Note** If a capacitor is not connected to the V<sub>CAP</sub> pin, AutoStore must be disabled by issuing the AutoStore Disable instruction specified in Command Register on page 8. If AutoStore is enabled without a capacitor on V<sub>CAP</sub> pin, the device attempts an AutoStore operation without sufficient charge to complete the Store. This corrupts the data stored in nvSRAM as well as the serial number and it unlocks the SNL bit.

Figure 9 shows the proper connection of the storage capacitor ( $V_{CAP}$ ) for AutoStore operation. Refer to DC Electrical Characteristics on page 18 for the size of the  $V_{CAP}$ .

Hardware RECALL (Power-Up)

During power-up, when  $V_{CC}$  crosses  $V_{SWITCH}$ , an automatic RECALL sequence is initiated, which transfers the content of nonvolatile memory to the SRAM. The data would previously have been stored in the nonvolatile memory through a STORE sequence.

A Power-Up RECALL cycle takes  $t_{FA}$  time to complete and the memory access is disabled during this time.

## Write Operation

The last bit of the slave device address indicates a read or a write operation. In case of a write operation, the slave device address is followed by the memory or register address and data. A write operation continues as long as a STOP or Repeated START condition is generated by the master or if a NACK is issued by the nvSRAM.

A NACK is issued from the nvSRAM under the following conditions:

- 1. A valid Device ID is not received.

- 2. A write (burst write) access to a protected memory block address returns a NACK from nvSRAM after the data byte is received. However, the address counter is set to this address and the following current read operation starts from this address.

- 3. A write/random read access to an invalid or out-of-bound memory address returns a NACK from the nvSRAM after the address is received. The address counter remains unchanged in such a case.

After a NACK is sent out from the nvSRAM, the write operation is terminated and any data on the SDA line is ignored until a STOP or a Repeated START condition is generated by the master.

For example, consider a case where the burst write access is performed on Control Register Slave address 0x01 for writing the serial number and continued to the address 0x09, which is a read only register. The device returns a NACK and address counter will not be incremented. A following read operation will be started from the address 0x09. Further, the nvSRAM responds to any write operation, which starts from a write-protected address (say, 0x09), with a NACK after the data byte is sent and set the

address counter to this address. A following read operation will start from the address 0x09 in this case also.

**Note** If the user tries to read/write access an address that does not exist (for example 0x0D in Control Register Slave), nvSRAM responds with a NACK immediately after the out-of-bound address is transmitted. The address counter remains unchanged and holds the previous successful read or write operation address.

A write operation is performed internally with no delay after the eighth bit of data is transmitted. If a write operation is not intended, the master must terminate the write operation before the eighth clock cycle by generating a STOP or Repeated START condition.

More details on write instruction are provided in the section, Memory Slave Access on page 10

### **Read Operation**

If the last bit of the slave device address is '1', a read operation is assumed and the nvSRAM takes control of the SDA line immediately after the slave device address byte is sent out by the master. The read operation starts from the current address location (the location following the previous successful write or read operation). When the last address is reached, the address counter loops back to the first address.

In case of the Control Register Slave, when a burst read is performed such that it flows to a non-existent address, the reads operation will loop back to 0x00. This is applicable, in particular for the Command Register.

There are the following ways to end a read operation:

- 1. The Master issues a NACK on the 9th clock cycle followed by a STOP or a Repeated START condition on the 10th clock cycle.

- 2. Master generates a STOP or Repeated START condition on the 9th clock cycle.

More details on write instruction are provided in Section Memory Slave Access on page 10.

#### **Memory Slave Access**

The following sections describe the data transfer sequence required to perform Read or Write operations from nvSRAM.

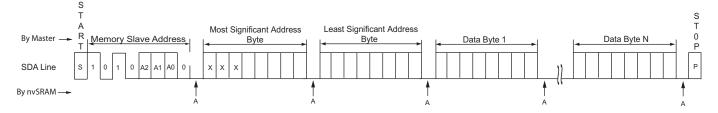

#### Write nvSRAM

Each write operation consists of a slave address being transmitted after the start condition. The last bit of slave address must be set as '0' to indicate a Write operation. The master may write one byte of data or continue writing multiple consecutive address locations while the internal address counter keeps incrementing automatically. The address register is reset to 0x0000 after the last address in memory is accessed. The write operation continues till a STOP or Repeated START condition is generated by the master or a NACK is issued by the nvSRAM.

A write operation is executed only after all the 8 data bits have been received by the nvSRAM. The nvSRAM sends an ACK signal after a successful write operation. A write operation may be terminated by the master by generating a STOP condition or a Repeated START operation. If the master desires to abort the current write operation without altering the memory contents, this should be done using a START/STOP condition prior to the 8th data bit.

If the master tries to access a write protected memory address on the nvSRAM, a NACK is returned after the data byte intended to write the protected address is transmitted and address counter will not be incremented. Similarly, in a burst mode write operation, a NACK is returned when the data byte that attempts to write a protected memory location and address counter will not be incremented.

Figure 10. Single-Byte Write into nvSRAM (except Hs-mode)

## Figure 12. Single-Byte Write into nvSRAM (Hs-mode)

Figure 13. Multi-Byte Write into nvSRAM (Hs-mode)

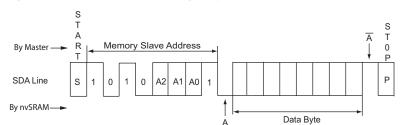

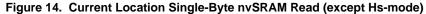

#### Current nvSRAM Read

Each read operation starts with the master transmitting the nvSRAM slave address with the LSB set to '1' to indicate "Read". The reads start from the address on the address counter. The address counter is set to the address location next to the last accessed with a "Write" or "Read" operation. The master may terminate a read operation after reading 1 byte or continue reading addresses sequentially until the last address in the memory after which the address counter rolls back to the address 0x0000. The valid methods of terminating read access are described in the section Read Operation on page 10.

A

Figure 15. Current Location Multi-Byte nvSRAM Read (except Hs-mode)

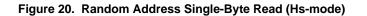

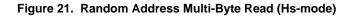

Figure 16. Current Location Single-Byte nvSRAM Read (Hs-mode)

Figure 17. Current Location Multi-Byte nvSRAM Read (Hs-mode)

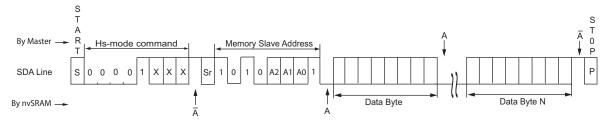

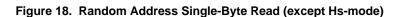

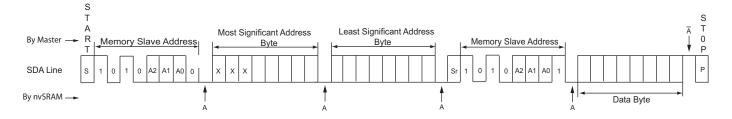

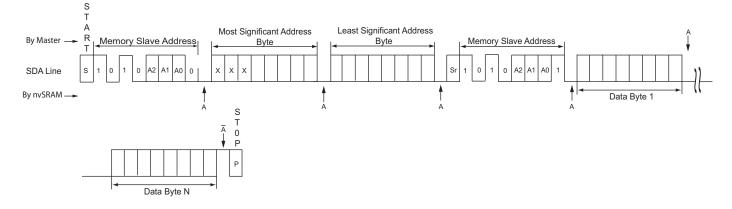

#### Random Address Read

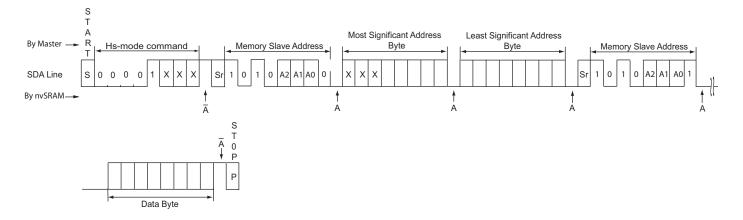

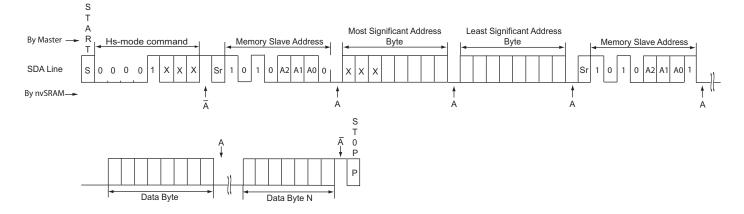

A random address read is performed by first initiating a write operation and generating a Repeated START immediately after the last address byte is acknowledged. The address counter is set to this address and the next read access to this slave initiates a read operation from here. The master may terminate a read operation after reading 1 byte or continue reading addresses sequentially until the last address in the memory after which the address counter rolls back to the start address 0x0000.

## Figure 19. Random Address Multi-Byte Read (except Hs-mode)

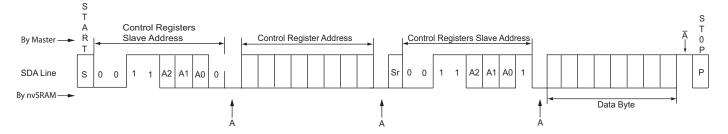

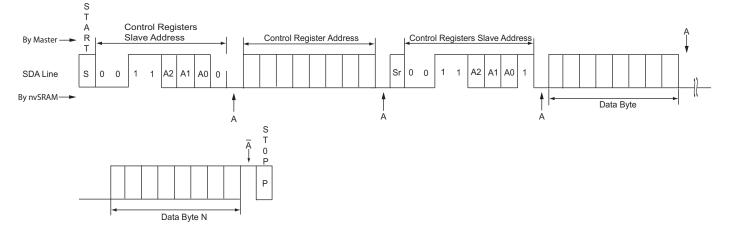

### **Control Registers Slave**

The following sections describe the data transfer sequence required to perform read or write operations from the Control Registers Slave.

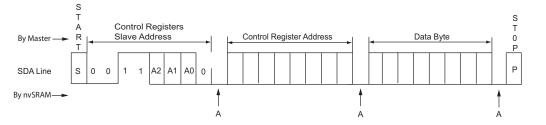

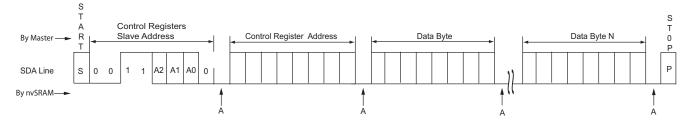

#### Write Control Registers

To write the Control Registers Slave, the master transmits the Control Registers Slave address after generating the START condition. The write sequence continues from the address location specified by the master until the master generates a STOP condition or the last writable address location.

If a non writable address location is accessed for write operation during a normal write or a burst, the slave generates a NACK after the data byte is sent and the write sequence terminates. Any following data bytes are ignored and the address counter is not incremented.

If a write operation is performed on the Command Register (0xAA), the following current read operation also begins from the

first address (0x00), and the current address is an out-of-bound address. The address is not incremented and the next current read operation begins from this address location. If a write operation is attempted on an out-of-bound address location, the nvSRAM sends a NACK immediately after the address byte is sent.

Further, if the serial number is locked, only two addresses (0xAA or Command Register, and 0x00 or Memory Control Register) are writable in the Control Registers Slave. On a write operation to any other address location, the device will acknowledge command byte and address bytes but it returns a NACK from the Control Registers Slave for data bytes. In this case, the address will not be incremented and a current read will happen from the last acknowledged address.

The nvSRAM Control Registers Slave sends a NACK when an out of bound memory address is accessed for write operation, by the master. In such a case, a following current read operation begins from the last acknowledged address.

### Figure 22. Single-Byte Write into Control Registers

Figure 23. Multi-Byte Write into Control Registers

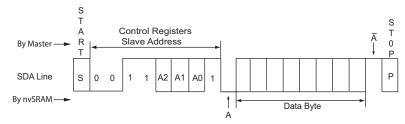

#### Current Control Registers Read

A read of the Control Registers Slave is started with the master sending the Control Registers Slave address after the START condition with the LSB set to '1'. The reads begin from the current address which is the next address to the last accessed location. The reads to Control Registers Slave continue until the last readable address location and loop back to the first location (0x00). Note that the Command Register is a write only register and is not accessible through the sequential read operations. If a burst read operation begins from the Command Register (0xAA), the address counter wraps around to the first address in the register map (0x00).

### Figure 25. Current Control Registers Multi-Byte Read

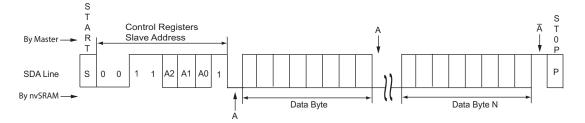

### Random Control Registers Read

A read of random address may be performed by initiating a write operation to the intended location of read and immediately following with a Repeated START operation. The reads to the Control Registers Slave continue until the last readable address location and loop back to the first location (0x00). Note that the Command Register is a write only register and is not accessible through the sequential read operations. A random read starting at the Command Register (0xAA) loops back to the first address in the Control Registers map (0x00). If a random read operation is initiated from an out-of-bound memory address, the nvSRAM sends a NACK after the address byte is sent.

Figure 26. Random Control Registers Single-Byte Read

Figure 27. Random Control Registers Multi-Byte Read

# **Serial Number**

The serial number is an 8-byte memory space provided to the user to uniquely identify this device. It typically consists of a two-byte customer ID, followed by five bytes of a unique serial number and one byte of CRC check. However, nvSRAM does not calculate the CRC and it is up to the user to use the eight-byte memory space in the desired format. The default values for the eight-byte locations are set to '0x00'.

### Serial Number Write

The serial number can be accessed through the Control Registers Slave Device. To write the serial number, the master transmits the Control Registers Slave address after the START condition and writes to the address location from 0x01 to 0x08. The content of Serial Number registers is secured to nonvolatile memory on the next STORE operation. If AutoStore is enabled, nvSRAM automatically stores the Serial number in the nonvolatile memory on power-down. However, if AutoStore is disabled, the user must perform a STORE operation to secure the contents of Serial Number registers.

**Note** If the serial number lock (SNL) bit is not set, the serial number registers can be re-written regardless of whether or not a STORE has happened. After the serial number lock bit is set, no writes to the serial number registers are allowed. If the master tries to perform a write operation to the serial number registers when the lock bit is set, a NACK is returned and write will not be performed.

### Serial Number Lock

After writes to Serial Number registers is complete, the master is responsible for locking the serial number by setting the serial number lock bit to '1' in the Memory Control Register (0x00). The content of the Memory Control Register and serial number are secured on the next STORE operation (STORE or AutoStore). If AutoStore is not enabled, the user must perform a STORE operation to secure the lock bit status.

If a STORE was not performed, the serial number lock bit will not survive the power cycle. The serial number lock bit and 8-byte serial number is set by default to '0' at power-up.

### Serial Number Read

The serial number can be read back by a read operation of the intended address of the Control Registers Slave. The Control Registers Device loops back from the last address (excluding the Command Register) to the 0x00 address location while performing a burst read operation. The serial number resides in the locations from 0x01 to 0x08. Even if the serial number is not locked, a serial number read operation returns the current values written to the serial number registers. The master may perform a serial number read operation to confirm if the correct serial number is written to the registers before setting the lock bit.

# **Device ID**

The device ID is a 4-byte code consisting of a JEDEC assigned manufacturer ID, product ID, density ID, and die revision. These registers are set in factory and are read-only registers for the user.

### Table 6. Device ID

|              |                        | Device ID Description |                   |                 |                 |  |  |

|--------------|------------------------|-----------------------|-------------------|-----------------|-----------------|--|--|

| Device       | Device ID<br>(4 bytes) | 31–21<br>(11 bits)    | 20–7<br>(14 bits) | 6–3<br>(4 bits) | 2–0<br>(3 bits) |  |  |

|              |                        | Manufacturer ID       | Product ID        | Density ID      | Die Rev         |  |  |

| CY14MB064J1A | 0x06812889             | 00000110100           | 00001001010001    | 0001            | 001             |  |  |

| CY14MB064J2A | 0x0681A889             | 00000110100           | 00001101010001    | 0001            | 001             |  |  |

| CY14ME064J1A | 0x06813089             | 00000110100           | 00001001100001    | 0001            | 001             |  |  |

| CY14ME064J2A | 0x0681B089             | 00000110100           | 00001101100001    | 0001            | 001             |  |  |

The device ID is divided into four parts as shown in Table 6:

1. Manufacturer ID (11 bits)

This is the JEDEC assigned manufacturer ID for Cypress. JEDEC assigns the manufacturer ID in different banks. The first three bits of the manufacturer ID represent the bank in which the ID is assigned. The next eight bits represent the manufacturer ID.

The Cypress manufacturer ID is 0x34 in bank 0. Therefore, the manufacturer ID for all Cypress nvSRAM products is given as:

Cypress ID - 000\_0011\_0100

2. Product ID (14 bits)

Table 6 lists the product ID for the device.

3. Density ID (4 bits)

The 4-bit density ID is used, as shown in Table 6, for indicating the 64-Kb density of the product.

4. Die Rev (3 bits)

This is used to represent any major change in the design of the product.

Table 6 lists the Die Rev for device.

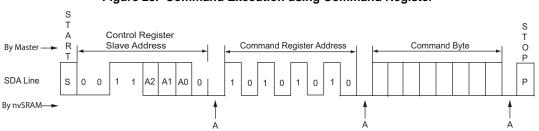

## **Executing Commands Using Command Register**

The Control Registers Slave allows different commands to be executed by writing the specific command byte in the Command Register (0xAA). The command byte codes for each command are specified in Table 5 on page 8. During the execution of these commands the device is not accessible and returns a NACK if any of the three slave devices is selected. If an invalid command is sent by the master, the nvSRAM responds with an ACK indicating that the command has been acknowledged with NOP (No Operation). The address rolls over to the 0x00 location.

### Figure 28. Command Execution using Command Register

# **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. These user guidelines are not tested.

| Storage temperature65 °C to +150 °C                                                       |

|-------------------------------------------------------------------------------------------|

| Maximum accumulated storage time                                                          |

| At 150 °C ambient temperature 1000 h                                                      |

| At 85 °C ambient temperature 20 Years                                                     |

| Maximum junction temperature 150 °C                                                       |

| Supply voltage on $V_{CC}$ relative to $V_{SS}$                                           |

| CY14MB064J:0.5 V to +4.1 V                                                                |

| CY14ME064J:0.5 V to +7.0 V                                                                |

| DC voltage applied to outputs                                                             |

| in High Z state                                                                           |

| Input voltage–0.5 V to V <sub>CC</sub> + 0.5 V                                            |

| Transient voltage (< 20 ns) on any pin to ground potential–2.0 V to V $_{\rm CC}$ + 2.0 V |

| Package power dissipation capability ( $T_A = 25 \text{ °C}$ ) 1.0 W |  |

|----------------------------------------------------------------------|--|

| Surface mount lead soldering<br>temperature (3 seconds)+260 °C       |  |

| DC output current<br>(1 output at a time, 1 s duration)15 mA         |  |

| Static discharge voltage<br>(per MIL-STD-883, Method 3015)> 2001 V   |  |

| Latch up current> 140 mA                                             |  |

# **Operating Range**

| Product    | Range      | Ambient<br>Temperature | V <sub>cc</sub> |

|------------|------------|------------------------|-----------------|

| CY14MB064J | Industrial | –40 °C to +85 °C       | 2.7 V to 3.6 V  |

| CY14ME064J |            |                        | 4.5 V to 5.5 V  |

# **DC Electrical Characteristics**

## Over the Operating Range

| Parameter                      | Description                                                | Test Condit                                                                                                                                                                                                                                          | Test Conditions                                                        |     |     | Max | Unit |

|--------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>                | Power supply                                               |                                                                                                                                                                                                                                                      | CY14MB064J                                                             | 2.7 | 3.0 | 3.6 | V    |

|                                |                                                            |                                                                                                                                                                                                                                                      | CY14ME064J                                                             | 4.5 | 5.0 | 5.5 | V    |

| I <sub>CC1</sub>               | Average V <sub>CC</sub> current                            | $f_{SCL} = 3.4 \text{ MHz};$<br>Values obtained withou<br>( $I_{OUT} = 0 \text{ mA}$ )                                                                                                                                                               | t output loads                                                         | -   | -   | 1   | mA   |

|                                |                                                            | f <sub>SCL</sub> = 1 MHz;<br>Values obtained withou<br>(I <sub>OUT</sub> = 0 mA)                                                                                                                                                                     | t output loads                                                         | -   | -   | 400 | μΑ   |

| I <sub>CC2</sub>               | Average V <sub>CC</sub> current during STORE               | All inputs don't care, Vo<br>Average current for dur                                                                                                                                                                                                 | <sub>CC</sub> = Max<br>ation t <sub>STORE</sub>                        | _   | -   | 3   | mA   |

| I <sub>CC4</sub>               | Average V <sub>CAP</sub> current during<br>AutoStore cycle | All inputs don't care. Av for duration t <sub>STORE</sub>                                                                                                                                                                                            | All inputs don't care. Average current for duration t <sub>STORE</sub> |     | -   | 3   | mA   |

| I <sub>SB</sub>                | V <sub>CC</sub> standby current                            | $SCL \ge (V_{CC} - 0.2 \text{ V}).$                                                                                                                                                                                                                  | CY14MB064J                                                             | -   | -   | 120 | μA   |

|                                |                                                            | $ \begin{array}{l} V_{IN} \leq 0.2 \ V \ \text{or} \\ V_{IN} \geq (V_{CC} - 0.2 \ V). \\ \text{Standby current level} \\ \text{after nonvolatile cycle} \\ \text{is complete. Inputs are} \\ \text{static. } f_{SCL} = 0 \ \text{MHz}. \end{array} $ | CY14ME064J                                                             | -   | _   | 150 | μΑ   |

| I <sub>ZZ</sub>                | Sleep mode current                                         | t <sub>SLEEP</sub> time after SLEEP Instruction is<br>Issued. All inputs are static and<br>configured at CMOS logic level.                                                                                                                           |                                                                        | _   | -   | 8   | μΑ   |

| I <sub>IX</sub> <sup>[5]</sup> | Input current in each I/O pin                              | 0.1 V <sub>CC</sub> < V <sub>i</sub> < 0.9 V <sub>CC</sub> max                                                                                                                                                                                       |                                                                        | -1  | _   | +1  | μA   |

| I <sub>OZ</sub>                | Output leakage current                                     |                                                                                                                                                                                                                                                      |                                                                        | -1  | -   | +1  | μA   |

| C <sub>i</sub>                 | Capacitance for each I/O pin                               | Capacitance measured and output signal pin a                                                                                                                                                                                                         |                                                                        | _   | -   | 7   | pF   |

#### Notes

4. Typical values are at 25 °C,  $V_{CC} = V_{CC(Typ)}$ . Not 100% tested. 5. Not applicable to WP, A2, A1, and A0 pins.

# DC Electrical Characteristics (continued)

### Over the Operating Range

| Parameter                           | Description                          | Test Condit                                 | ions            | Min                  | Тур <sup>[4]</sup> | Max                   | Unit |

|-------------------------------------|--------------------------------------|---------------------------------------------|-----------------|----------------------|--------------------|-----------------------|------|

| V <sub>IH</sub>                     | Input HIGH voltage                   |                                             |                 | $0.7 \times V_{CC}$  | _                  | V <sub>CC</sub> + 0.5 | V    |

| V <sub>IL</sub>                     | Input LOW voltage                    |                                             |                 | - 0.5                | _                  | 0.3 × Vcc             | V    |

| V <sub>OL</sub>                     | Output LOW voltage                   | I <sub>OL</sub> = 3 mA                      |                 | 0                    | _                  | 0.4                   | V    |

|                                     |                                      | I <sub>OL</sub> = 6 mA                      |                 | 0                    | _                  | 0.6                   | V    |

| R <sub>in</sub> <sup>[6]</sup>      |                                      | For V <sub>IN</sub> = V <sub>IL (Max)</sub> |                 | 50                   | _                  | -                     | KΩ   |

|                                     | A0)                                  | For $V_{IN} = V_{IH (Min)}$                 |                 | 1                    | _                  | -                     | MΩ   |

| V <sub>hys</sub>                    | Hysteresis of Schmitt trigger inputs |                                             |                 | $0.05 \times V_{CC}$ | _                  | -                     | V    |

| V <sub>CAP</sub> <sup>[7]</sup>     | Storage capacitor                    | Between V <sub>CAP</sub> pin and            | V <sub>SS</sub> | 42                   | 47                 | 180                   | μF   |

| V <sub>VCAP</sub> <sup>[8, 9]</sup> | Maximum voltage driven on            | V <sub>CC</sub> = Max                       | CY14MB064J      | —                    | _                  | V <sub>CC</sub>       | V    |

|                                     | V <sub>CAP</sub> pin by the device   |                                             | CY14ME064J      | -                    | _                  | V <sub>CC</sub> - 0.5 |      |

# **Data Retention and Endurance**

### Over the Operating Range

| Parameter         | Description                  | Min   | Unit  |

|-------------------|------------------------------|-------|-------|

| DATA <sub>R</sub> | Data retention               | 20    | Years |

| NV <sub>C</sub>   | Nonvolatile STORE operations | 1,000 | К     |

# **Thermal Resistance**

| Parameter <sup>[9]</sup> | Description                                 | Test Conditions                                                                                        | 8-pin SOIC | Unit |

|--------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------|------------|------|

| $\Theta_{JA}$            | Thermal resistance<br>(junction to ambient) | Test conditions follow standard test methods and procedures for measuring thermal impedance, per EIA / |            | °C/W |

| $\Theta^{JC}$            | Thermal resistance<br>(junction to case)    | JESD51.                                                                                                | 37.86      | °C/W |

Notes

- 6. The input pull-down circuit is stronger (50 KΩ) when the input voltage is below  $V_{IL}$  and weak (1 MΩ) when the input voltage is above  $V_{IH}$ . 7. Min  $V_{CAP}$  value guarantees that there is a sufficient charge available to complete a successful AutoStore operation. Max  $V_{CAP}$  value guarantees that the capacitor on  $V_{CAP}$  is charged to a minimum voltage during a Power-Up RECALL cycle so that an immediate power-down cycle can complete a successful AutoStore. Therefore it is always recommended to use a capacitor within the specified min and max limits. Refer application note AN43593 for more details on  $V_{CAP}$  options.

- Maximum voltage on V<sub>CAP</sub> pin (V<sub>VCAP</sub>) is provided for guidance when choosing the V<sub>CAP</sub> capacitor. The voltage rating of the V<sub>CAP</sub> capacitor across the operating temperature range should be higher than the V<sub>VCAP</sub> voltage.

These parameters are guaranteed by design and are not tested.

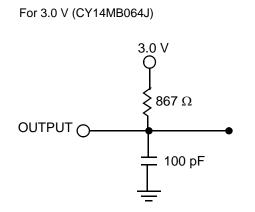

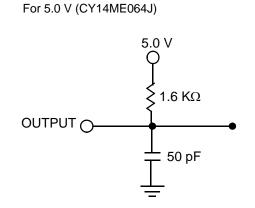

# AC Test Loads and Waveforms

Figure 29. AC Test Loads and Waveforms

# AC Test Conditions

| Description                              | CY14MB064J | CY14ME064J |

|------------------------------------------|------------|------------|

| Input pulse levels                       | 0 V to 3 V | 0 V to 5 V |

| Input rise and fall times (10%–90%)      | 10 ns      | 10 ns      |

| Input and output timing reference levels | 1.5 V      | 2.5 V      |

# **AC Switching Characteristics**

Over the Operating Range

| Parameter                       | Description                                                   | 3.4 M | Hz <sup>[11]</sup> | 1 MF | <b>lz</b> <sup>[11]</sup> | 400 k | Hz <sup>[11]</sup> | Unit |

|---------------------------------|---------------------------------------------------------------|-------|--------------------|------|---------------------------|-------|--------------------|------|

| [10]                            | Description                                                   | Min   | Max                | Min  | Max                       | Min   | Max                | Unit |

| f <sub>SCL</sub>                | Clock frequency, SCL                                          | _     | 3400               | -    | 1000                      | -     | 400                | kHz  |

| t <sub>SU; STA</sub>            | Setup time for Repeated START condition                       | 160   | -                  | 250  | -                         | 600   | -                  | ns   |

| t <sub>HD;STA</sub>             | Hold time for START condition                                 | 160   | -                  | 250  | -                         | 600   | -                  | ns   |

| t <sub>LOW</sub>                | LOW period of the SCL                                         | 160   | -                  | 500  | -                         | 1300  | -                  | ns   |

| t <sub>HIGH</sub>               | HIGH period of the SCL                                        | 60    | -                  | 260  | -                         | 600   | -                  | ns   |

| t <sub>SU;DATA</sub>            | Data in setup time                                            | 10    | -                  | 100  | -                         | 100   | -                  | ns   |

| t <sub>HD;DATA</sub>            | Data hold time (In/Out)                                       | 0     | -                  | 0    | -                         | 0     | -                  | ns   |

| t <sub>DH</sub>                 | Data out hold time                                            | 0     | -                  | 0    | -                         | 0     | -                  | ns   |

| t <sub>r</sub> <sup>[12]</sup>  | Rise time of SDA and SCL                                      | _     | 80                 | -    | 120                       | -     | 300                | ns   |

| t <sub>f</sub> [12]             | Fall time of SDA and SCL                                      | _     | 80                 | -    | 120                       | -     | 300                | ns   |

| t <sub>SU;STO</sub>             | Setup time for STOP condition                                 | 160   | -                  | 250  | -                         | 600   | -                  | ns   |

| t <sub>VD;DATA</sub>            | Data output valid time                                        | _     | 130                | -    | 400                       | -     | 900                | ns   |

| t <sub>VD;ACK</sub>             | ACK output valid time                                         | _     | 130                | -    | 400                       | -     | 900                | ns   |

| t <sub>OF</sub> <sup>[12]</sup> | Output fall time from $V_{IH(min)}$ to $V_{IL(max)}$          | -     | 80                 | -    | 120                       | -     | 250                | ns   |

| t <sub>BUF</sub>                | Bus free time between STOP and next START condition           | 0.3   | -                  | 0.5  | -                         | 1.3   | -                  | us   |

| t <sub>SP</sub>                 | Pulse width of spikes that must be suppressed by input filter | -     | 10                 | -    | 50                        | -     | 50                 | ns   |

# **Switching Waveforms**

#### Notes

- 10. Test conditions assume signal transition time of 10 ns or less, timing reference levels of  $V_{CC}/2$ , input pulse levels of 0 to  $V_{CC(typ)}$ , and output loading of the specified  $I_{OL}$  and load capacitance shown in Figure 29. 11. Bus Load (Cb) considerations; Cb < 500 pF for I<sup>2</sup>C clock frequency (SCL) 100/400 KHz; Cb < 550 pF for SCL at 1000 kHz; Cb < 100 pF for SCL at 3.4 MHz.

12. These parameters are guaranteed by design and are not tested.

# **nvSRAM Specifications**

## Over the Operating Range

| Parameter                            | Description                                                  |           | Min | Max  | Unit |

|--------------------------------------|--------------------------------------------------------------|-----------|-----|------|------|

| t <sub>FA</sub> <sup>[13]</sup>      | Power-Up RECALL duration                                     |           | -   | 20   | ms   |

| t <sub>STORE</sub> <sup>[14]</sup>   | STORE cycle duration                                         |           | -   | 8    | ms   |

| t <sub>DELAY</sub> [15, 16]          | Time allowed to complete SRAM write cycle                    |           |     | 25   | ns   |

| t <sub>VCCRISE</sub> <sup>[16]</sup> | V <sub>CC</sub> rise time                                    |           |     | -    | μs   |

| V <sub>SWITCH</sub>                  | Low voltage trigger level CY14MB064J                         |           | -   | 2.65 | V    |

|                                      | C                                                            | Y14ME064J | -   | 4.40 | V    |

| t <sub>WAKE</sub>                    | Time for nvSRAM to wake up from SLEEP mode                   |           |     | 20   | ms   |

| t <sub>SLEEP</sub>                   | Time to enter low power mode after issuing SLEEP instruction |           |     | 8    | ms   |

| t <sub>SB</sub> <sup>[16]</sup>      | Time to enter into standby mode after issuing STOP condition |           | _   | 100  | μs   |

# **Switching Waveforms**

Figure 31. AutoStore or Power-Up RECALL <sup>[17]</sup>

#### Notes

- 13.  $t_{FA}$  starts from the time V<sub>CC</sub> rises above V<sub>SWITCH</sub>. 14. If an SRAM write has not taken place since the last nonvolatile cycle, no AutoStore takes place.

- 15. On a AutoStore initiation, SRAM write operation continues to be enabled for time t<sub>DELAY</sub>

- 16. These parameters are guaranteed by design and are not tested.

- 17. Read and Write cycles are ignored during STORE, RECALL, and while V<sub>CC</sub> is below V<sub>SWITCH</sub>.

# Software Controlled STORE/RECALL Cycles

Over the Operating Range

| Parameter                           | Description                       |     | CY14MX064J |      |  |

|-------------------------------------|-----------------------------------|-----|------------|------|--|

| Falailletei                         | Description                       | Min | Max        | Unit |  |

| t <sub>RECALL</sub>                 | RECALL duration                   | _   | 600        | μs   |  |

| t <sub>SS</sub> <sup>[18, 19]</sup> | Software sequence processing time |     | 500        | μs   |  |

# Switching Waveforms

### Figure 33. AutoStore Enable/Disable Cycle

#### Notes

This is the amount of time it takes to take action on a soft sequence command. V<sub>CC</sub> power must remain HIGH to effectively register command.

Commands such as STORE and RECALL lock out I/O until operation is complete which further increases this time. See the specific command.

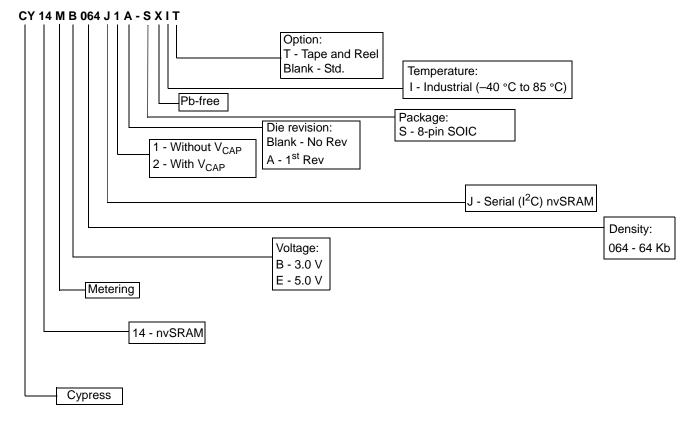

# **Ordering Information**

| Ordering Code     | Package<br>Diagram | Package Type                           | Operating<br>Range |

|-------------------|--------------------|----------------------------------------|--------------------|

| CY14MB064J2A-SXI  | 51-85066           | 8-pin SOIC (with V <sub>CAP</sub> )    | Industrial         |

| CY14MB064J2A-SXIT |                    | 8-pin SOIC (with V <sub>CAP</sub> )    |                    |

| CY14ME064J1A-SXI  |                    | 8-pin SOIC (without V <sub>CAP</sub> ) |                    |

| CY14ME064J1A-SXIT |                    | 8-pin SOIC (without V <sub>CAP</sub> ) | 1                  |

The above parts are Pb-free. This table contains final information. Contact your local Cypress sales representative for availability of these parts.

# **Ordering Code Definitions**

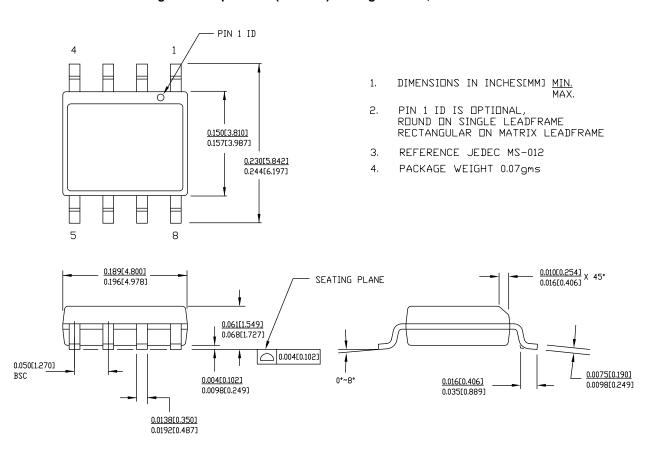

# **Package Diagrams**

Figure 34. 8-pin SOIC (150 mils) Package Outline, 51-85066

51-85066 \*F

# Acronyms

| Acronym          | Description                                |

|------------------|--------------------------------------------|

| ACK              | Acknowledge                                |

| CMOS             | Complementary Metal Oxide Semiconductor    |

| CRC              | Cyclic Redundancy Check                    |

| EIA              | Electronic Industries Alliance             |

| I <sup>2</sup> C | Inter-Integrated Circuit                   |

| I/O              | Input/Output                               |

| JEDEC            | Joint Electron Devices Engineering Council |

| LSB              | Least Significant Bit                      |

| MSB              | Most Significant Bit                       |

| nvSRAM           | non-volatile Static Random Access Memory   |

| NACK             | No Acknowledge                             |

| RoHS             | Restriction of Hazardous Substances        |

| R/W              | Read/Write                                 |

| RWI              | Read and Write Inhibit                     |

| SCL              | Serial Clock Line                          |

| SDA              | Serial Data Access                         |

| SNL              | Serial Number Lock                         |

| SOIC             | Small Outline Integrated Circuit           |

| SRAM             | Static Random access memory                |

| WP               | Write Protect                              |

# **Document Conventions**

## **Units of Measure**

| Symbol | Unit of Measure |  |  |  |

|--------|-----------------|--|--|--|

| °C     | degree Celsius  |  |  |  |

| Hz     | hertz           |  |  |  |

| kHz    | kilohertz       |  |  |  |

| kΩ     | kilohm          |  |  |  |

| Mbit   | megabit         |  |  |  |

| MHz    | megahertz       |  |  |  |

| MΩ     | megaohm         |  |  |  |

| μΑ     | microampere     |  |  |  |

| μF     | microfarad      |  |  |  |

| μS     | microsecond     |  |  |  |

| mA     | milliampere     |  |  |  |

| ms     | millisecond     |  |  |  |

| ns     | nanosecond      |  |  |  |

| Ω      | ohm             |  |  |  |

| %      | percent         |  |  |  |

| pF     | picofarad       |  |  |  |

| V      | volt            |  |  |  |

| W      | watt            |  |  |  |

# **Document History Page**

| Rev. | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                        |

|------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 3291153 | GVCH               | 06/23/2011         | New data sheet                                                                                                                                                                                                                                                                                                                                                                               |

| *A   | 3403128 | GVCH               | 10/12/2011         | Updated I2C Interface (SLEEP description on page 8).<br>Updated Executing Commands Using Command Register (description).<br>Updated DC Electrical Characteristics (Removed $I_{CC3}$ parameter).<br>Updated AC Switching Characteristics (Updated the maximum value of $t_{SP}$ parameter from 5 ns to 10 ns for 3.4 MHz).<br>Updated Switching Waveforms (Updated Figure 32 and Figure 33). |

| *В   | 3515468 | GVCH               | 02/02/2012         | Removed Best Practices.<br>Updated Ordering Information (Added CY14MB064J2A-SXIT,<br>CY14MB064J1A-SXIT, CY14ME064J2A-SXIT and CY14ME064J1A-SXIT).                                                                                                                                                                                                                                            |

| *C   | 3539393 | GVCH               | 03/16/2012         | Updated nvSRAM Specifications (No other change, only referred Note 16 in $t_{SB}$ parameter).                                                                                                                                                                                                                                                                                                |

| *D   | 3605955 | GVCH               | 05/02/2012         | No technical updates.                                                                                                                                                                                                                                                                                                                                                                        |

| *E   | 3702613 | GVCH               | 08/03/2012         | Updated DC Electrical Characteristics (Added $V_{VCAP}$ parameter and its details, added Note 8 and referred the same note in $V_{VCAP}$ parameter, also referred Note 9 in $V_{VCAP}$ parameter).                                                                                                                                                                                           |

| *F   | 3759535 | GVCH               | 09/28/2012         | Updated Maximum Ratings (Removed "Ambient temperature with power applied" and included "Maximum junction temperature").                                                                                                                                                                                                                                                                      |

| *G   | 3823702 | GVCH               | 11/28/2012         | Changed status from "Preliminary" to "Final".<br>Updated Ordering Information (Updated part numbers).                                                                                                                                                                                                                                                                                        |

| *H   | 3983091 | GVCH               | 04/26/2013         | Updated Features:<br>Added Note 1 (To clarify non-compliance with the NXP I <sup>2</sup> C specification).                                                                                                                                                                                                                                                                                   |

|      |         |                    |                    | Updated DC Electrical Characteristics:<br>Added one more condition " $I_{OL} = 6$ mA" for $V_{OL}$ parameter and added<br>respective values.                                                                                                                                                                                                                                                 |

|      |         |                    |                    | Updated AC Switching Characteristics:<br>Updated Note 11.                                                                                                                                                                                                                                                                                                                                    |