# SO-8、12ビット、400ksps ADCシャットダウン機能付き

### 特長

- SO-8パッケージの完全12ビットADC

- 単一5Vまたは±5V電源動作

- サンプル・レート: 400ksps

- 消費電力:75mW(標準)

- ナイキスト入力周波数にてS/(N+D)72dBおよびTHD 80dB

- 全温度範囲にてミッシング・コードなし

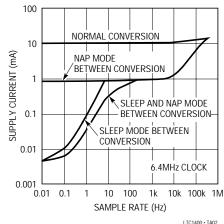

- 即時ウェイクアップ可能なナップ・モード時の消費電力:6mW

- スリープ・モード時の消費電力:30uW

- ハイ・インピーダンス・アナログ入力

- 入力範囲(1mV/LSB): 0V~4.096Vまたは±2.048V

- 内部リファレンスを外部からオーバドライブ可能

- DSPおよびプロセッサへの3線式インタフェース (SPIおよびMICROWIRE<sup>TM</sup>に対応)

## アプリケーション

- 高速データ収集

- デジタル信号処理

- 多チャネル・データ収集システム

- オーディオおよびテレコム処理

- デジタル無線

- スペクトラム分析

- 低消費電力およびバッテリ駆動システム

- ハンドヘルドまたはポータブル機器

### 概要

LTC®1400は400kspsの完全な12ビットA/Dコンバータで、単一 5Vまたは±5V電源で動作し消費電力はわずか75mWです。こ れらのデバイスは使いやすく、200nsのサンプル・ホールド、高 精度リファレンスを内蔵しています。また、ユニポーラおよ びバイポーラ変換モードを備え、柔軟性が向上しています。 LTC1400には、ナップ・モードとスリープ・モードの2つの省電 カモードがあります。ナップ・モードの消費電流はわずか 6mWで、即時にウェイクアップし変換を行うことができま す。スリープ·モードでは、消費電力は標準で30μWです。ス リープ・モードからの起動時に、シリアル・データ・ワードの リファレンス・レディ(REFRDY)信号を使用して、リファレン スが安定しチップが変換可能な状態にあることを示します。

LTC1400は、単一5V電源からの0V~4.096Vのユニポーラ入力、 および±5V電源からの±2.048Vバイポーラ入力を変換しま す。DCスペックの最大値には、全温度範囲での±1LSBのINL、 ±1LSBのDNL、および45ppm/ ドリフトが含まれます。また、 保証AC性能には、全温度範囲にわたる入力周波数100kHzでの 70dBのS(N+D)および - 76dBのTHDが含まれています。

3線式シリアル・ポートにより、さまざまなマイクロプ ロセッサ、マイクロコントローラ、およびDSPにコンパ クトで効率的なデータ転送が可能です。

∠ブ、LTC、LTはリニアテクノロジー社の登録商標です。

MICROWIREは、ナショナル・セミコンダクター社の商標です。

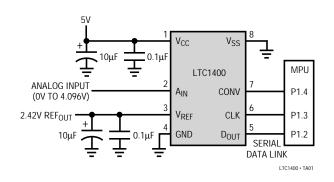

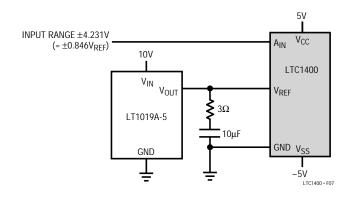

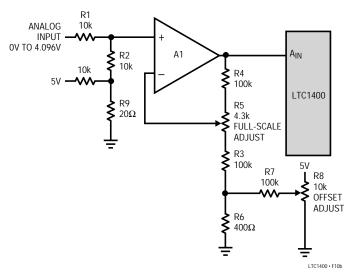

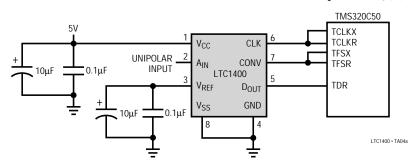

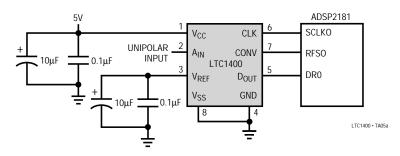

## 標準的応用例

単一5V電源、400kHz、12ビット・サンプリングA/Dコンバータ

#### 消費電源とサンプリング・レート

### 絶対最大定格

| (Notes 1, 2)                                                 |

|--------------------------------------------------------------|

| 電源電圧(V <sub>CC</sub> )7V                                     |

| 負電源電圧(V <sub>SS</sub> ) 6V~GND                               |

| 全電源電圧(V <sub>CC</sub> ~V <sub>SS</sub> )                     |

| バイポーラ動作専用12V                                                 |

| アナログ入力電圧( Note 3 )                                           |

| ユニポーラ動作 0.3V ~( V <sub>CC</sub> + 0.3V )                     |

| バイポーラ動作(V <sub>SS</sub> - 0.3V )~(V <sub>CC</sub> + 0.3V )   |

| デジタル入力電圧(Note 4)                                             |

| ユニポーラ動作 0.3V ~ 12V                                           |

| バイポーラ動作( V <sub>SS</sub> - 0.3V )~ 12V                       |

| デジタル出力電圧                                                     |

|                                                              |

| ユニポーラ動作 0.3V ~( V <sub>CC</sub> + 0.3V )                     |

| バイポーラ動作( V <sub>SS</sub> - 0.3V )~( V <sub>CC</sub> + 0.3V ) |

| 消費電力 500mW                                                   |

| 動作温度範囲                                                       |

| LTC1400C 0 ~ 70                                              |

| LTC1400I 40 ~ 85                                             |

| 保存温度範囲 65 ~ 150                                              |

| リード温度(半田付け、10秒)300                                           |

|                                                              |

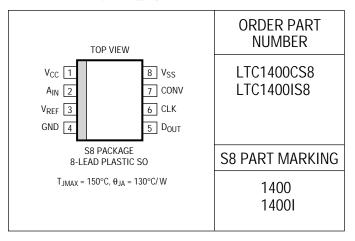

# パッケージ/発注情報

PDIPパッケージおよびミリタリ・グレード・デバイスに関してはお問い合わせください。

# **電源要求条件** (Note 5)

| SYMBOL          | PARAMETER                        | CONDITIONS                           |   | MIN   | TYP | MAX   | UNITS |

|-----------------|----------------------------------|--------------------------------------|---|-------|-----|-------|-------|

| $V_{CC}$        | Positive Supply Voltage (Note 6) | Unipolar                             |   | 4.75  |     | 5.25  | V     |

|                 |                                  | Bipolar                              |   | 4.75  |     | 5.25  | V     |

| $V_{SS}$        | Negative Supply Voltage (Note 6) | Bipolar Only                         |   | -2.45 |     | -5.25 | V     |

| I <sub>CC</sub> | Positive Supply Current          | f <sub>SAMPLE</sub> = 400ksps        | • |       | 15  | 30    | mA    |

|                 |                                  | Nap Mode                             | • |       | 1.0 | 3.0   | mA    |

|                 |                                  | Sleep Mode                           | • |       | 5.0 | 20.0  | μΑ    |

| I <sub>SS</sub> | Negative Supply Current          | $f_{SAMPLE} = 400ksps, V_{SS} = -5V$ | • |       | 0.3 | 0.6   | mA    |

|                 |                                  | Nap Mode                             | • |       | 0.2 | 0.5   | mA    |

|                 |                                  | Sleep Mode                           | • |       | 1   | 5     | μΑ    |

| $P_{D}$         | Power Dissipation                | f <sub>SAMPLE</sub> = 400ksps        | • |       | 75  | 160   | mW    |

|                 |                                  | Nap Mode                             | • |       | 6   | 20    | mW    |

|                 |                                  | Sleep Mode                           | • |       | 30  | 125   | μW    |

# アナロ**グ**入力 (Note 5)

| SYMBOL          | PARAMETER                    | CONDITIONS                                                                                                         |     | MIN T | ΥP            | MAX | UNITS    |

|-----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-------|---------------|-----|----------|

| V <sub>IN</sub> | Analog Input Range (Note 7)  | $4.75V \le V_{CC} \le 5.25V$ (Unipolar)<br>$4.75V \le V_{CC} \le 5.25V$ , $-5.25V \le V_{SS} \le -2.45V$ (Bipolar) | • • |       | 4.096<br>.048 |     | V        |

| I <sub>IN</sub> | Analog Input Leakage Current | During Conversions (Hold Mode)                                                                                     | •   |       |               | ±1  | μΑ       |

| C <sub>IN</sub> | Analog Input Capacitance     | Between Conversions (Sample Mode)<br>During Conversions (Hold Mode)                                                |     | 4     | 15<br>5       | ·   | pF<br>pF |

# コンパータ特性 内部リファレンス使用(Notes 5、8)

| PARAMETER                     | CONDITIONS                |   | MIN | TYP | MAX | UNITS  |

|-------------------------------|---------------------------|---|-----|-----|-----|--------|

| Resolution (No Missing Codes) |                           | • | 12  |     |     | Bits   |

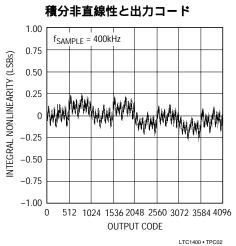

| Integral Linearity Error      | (Note 9)                  | • |     |     | ±1  | LSB    |

| Differential Linearity Error  |                           | • |     |     | ±1  | LSB    |

| Offset Error                  | (Note 10)                 |   |     |     | ±6  | LSB    |

|                               |                           | • |     |     | ±8  | LSB    |

| Full-Scale Error              |                           |   |     |     | ±15 | LSB    |

| Full-Scale Tempco             | I <sub>OUT(REF)</sub> = 0 | • |     | ±10 | ±45 | ppm/°C |

# ダイナミック精度 V<sub>CC</sub>=5V、V<sub>SS</sub>=-5V、f<sub>SAMPLE</sub>=400kHz

| SYMBOL    | PARAMETER                                       | CONDITIONS                                                                                                              |   | MIN      | TYP        | MAX | UNITS    |

|-----------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---|----------|------------|-----|----------|

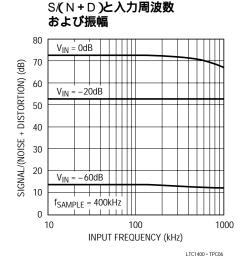

| S/(N + D) | Signal-to-Noise<br>Plus Distortion Ratio        | 100kHz Input Signal Commercial Industrial                                                                               | • | 70<br>69 | 72         |     | dB<br>dB |

|           |                                                 | 200kHz Input Signal                                                                                                     |   |          | 72         |     | dB       |

| THD       | Total Harmonic Distortion<br>Up to 5th Harmonic | 100kHz Input Signal<br>200kHz Input Signal                                                                              | • |          | -82<br>-80 | -76 | dB<br>dB |

|           | Peak Harmonic or<br>Spurious Noise              | 100kHz Input Signal<br>200kHz Input Signal                                                                              | • |          | -84<br>-82 | -76 | dB<br>dB |

| IMD       | Intermodulation Distortion                      | f <sub>IN1</sub> = 99.51kHz, f <sub>IN2</sub> = 102.44kHz<br>f <sub>IN1</sub> = 199.12kHz, f <sub>IN2</sub> = 202.05kHz |   |          | -82<br>-70 |     | dB<br>dB |

|           | Full Power Bandwidth                            |                                                                                                                         |   |          | 4          |     | MHz      |

|           | Full Linear Bandwidth (S/(N + D) ≥ 68dB)        |                                                                                                                         |   |          | 900        |     | kHz      |

# 内部リファレンス特性 (Note 5)

| PARAMETER                                              | CONDITIONS                                                 |   | MIN   | TYP          | MAX   | UNITS          |

|--------------------------------------------------------|------------------------------------------------------------|---|-------|--------------|-------|----------------|

| V <sub>REF</sub> Output Voltage                        | I <sub>OUT</sub> = 0                                       |   | 2.400 | 2.420        | 2.440 | V              |

| V <sub>REF</sub> Output Tempco                         | I <sub>OUT</sub> = 0                                       | • |       | ±10          | ±45   | ppm/°C         |

| V <sub>REF</sub> Line Regulation                       | $4.75V \le V_{CC} \le 5.25V$<br>$-5.25V \le V_{SS} \le 0V$ |   |       | 0.01<br>0.01 |       | LSB/V<br>LSB/V |

| V <sub>REF</sub> Load Regulation                       | $0 \le  I_{OUT}  \le 1mA$                                  |   |       | 2            |       | LSB/mA         |

| V <sub>REF</sub> Wake-Up Time from Sleep Mode (Note 7) | $C_{VREF} = 10\mu F$                                       |   |       | 4            |       | ms             |

# デジタル入力および出力 (Note 5)

| SYMBOL          | PARAMETER                 | CONDITIONS                                                                  |   | MIN | TYP          | MAX | UNITS |

|-----------------|---------------------------|-----------------------------------------------------------------------------|---|-----|--------------|-----|-------|

| V <sub>IH</sub> | High Level Input Voltage  | V <sub>CC</sub> = 5.25V                                                     | • | 2.0 |              |     | V     |

| V <sub>IL</sub> | Low Level Input Voltage   | V <sub>CC</sub> = 4.75V                                                     | • |     |              | 0.8 | V     |

| I <sub>IN</sub> | Digital Input Current     | V <sub>IN</sub> = 0V to V <sub>CC</sub>                                     | • |     |              | ±10 | μA    |

| C <sub>IN</sub> | Digital Input Capacitance |                                                                             |   |     | 5            |     | pF    |

| V <sub>OH</sub> | High Level Output Voltage | $V_{CC} = 4.75V$ , $I_0 = -10\mu A$<br>$V_{CC} = 4.75V$ , $I_0 = -200\mu A$ | • | 4.0 | 4.7          |     | V     |

| V <sub>OL</sub> | Low Level Output Voltage  | $V_{CC} = 4.75V$ , $I_{O} = 160\mu A$<br>$V_{CC} = 4.75V$ , $I_{O} = 1.6mA$ | • |     | 0.05<br>0.10 | 0.4 | V     |

# デジタル入力および出力 (Note 5)

| SYMBOL              | PARAMETER                                         | CONDITIONS                        |   | MIN | TYP | MAX | UNITS |

|---------------------|---------------------------------------------------|-----------------------------------|---|-----|-----|-----|-------|

| I <sub>OZ</sub>     | Hi-Z Output Leakage D <sub>OUT</sub>              | $V_{OUT} = OV \text{ to } V_{CC}$ | • |     |     | ±10 | μΑ    |

| C <sub>OZ</sub>     | Hi-Z Output Capacitance D <sub>OUT</sub> (Note 7) |                                   |   |     | 15  |     | pF    |

| I <sub>SOURCE</sub> | Output Source Current                             | V <sub>OUT</sub> = 0              |   |     | -10 |     | mA    |

| I <sub>SINK</sub>   | Output Sink Current                               | $V_{OUT} = V_{CC}$                |   |     | 10  |     | mA    |

### タイミング特性 (Note 5)

| SYMBOL                   | PARAMETER                                                                                                                             | CONDITIONS                |   | MIN | TYP        | MAX        | UNITS    |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---|-----|------------|------------|----------|

| f <sub>SAMPLE(MAX)</sub> | Maximum Sampling Frequency                                                                                                            | (Note 6)                  | • | 400 |            |            | kHz      |

| t <sub>CONV</sub>        | Conversion Time                                                                                                                       | f <sub>CLK</sub> = 6.4MHz | • |     |            | 2.1        | μs       |

| t <sub>ACQ</sub>         | Acquisition Time (Unipolar Mode)<br>(Bipolar Mode V <sub>SS</sub> = -5V)                                                              | (Note 7)                  | • |     | 230<br>200 | 300<br>270 | ns<br>ns |

| f <sub>CLK</sub>         | CLK Frequency                                                                                                                         |                           | • | 0.1 |            | 6.4        | MHz      |

| t <sub>CLK</sub>         | CLK Pulse Width                                                                                                                       | (Note 7)                  | • | 50  |            |            | ns       |

| t <sub>WK(NAP)</sub>     | Time to Wake Up from Nap Mode                                                                                                         | (Note 7)                  |   |     | 350        |            | ns       |

| t <sub>1</sub>           | CLK Pulse Width to Return to Active Mode                                                                                              |                           | • | 50  |            |            | ns       |

| t <sub>2</sub>           | CONV↑ to CLK↑ Setup Time                                                                                                              |                           | • | 80  |            |            | ns       |

| t <sub>3</sub>           | CONV↑ After Leading CLK↑                                                                                                              |                           | • | 0   |            |            | ns       |

| $t_4$                    | CONV Pulse Width                                                                                                                      | (Note 11)                 | • | 50  |            |            | ns       |

| t <sub>5</sub>           | Time from CLK↑ to Sample Mode                                                                                                         | (Note 7)                  |   |     | 80         |            | ns       |

| t <sub>6</sub>           | Aperture Delay of Sample-and-Hold                                                                                                     | Jitter < 50ps (Note 7)    | • |     | 45         | 65         | ns       |

| t <sub>7</sub>           | $\begin{array}{c} \mbox{Minimum Delay Between Conversion} & \mbox{(Unipolar Mode)} \\ \mbox{(Bipolar Mode V_{SS} = -5V)} \end{array}$ |                           | • |     | 265<br>235 | 385<br>355 | ns<br>ns |

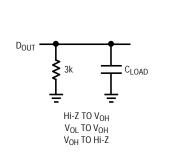

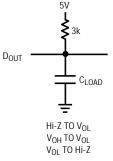

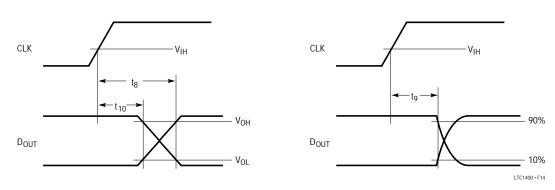

| t <sub>8</sub>           | Delay Time, CLK↑ to D <sub>OUT</sub> Valid                                                                                            | C <sub>LOAD</sub> = 20pF  | • |     | 40         | 80         | ns       |

| t <sub>9</sub>           | Delay Time, CLK↑ to D <sub>OUT</sub> Hi-Z                                                                                             | C <sub>LOAD</sub> = 20pF  | • |     | 40         | 80         | ns       |

| t <sub>10</sub>          | Time from Previous Data Remains Valid After CLK↑                                                                                      | C <sub>LOAD</sub> = 20pF  | • | 14  | 25         |            | ns       |

は全動作温度範囲の規格値を意味する。他のすべてのリミット値と標準値は T<sub>A</sub>=25 の値である。

Note 1:絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2: すべての電圧値はGNDを基準とする。 Note 3: これらのビン電圧を $V_{SG}$  ユニポーラ・モードのグランド)より低くするか、 $V_{CC}$ より高くすると、内部ダイオードによってクランプされる。この製品は $V_{SG}$  ユニポーラ・モードのグランド)より低い、または $V_{CC}$ より高い電圧を $I_{CC}$  を加えてもラッチアップを起こさずに $I_{CC}$  のの外間ではない。

Note 4: これらのピン電圧を $V_{SG}$ (ユニポーラ・モードのグランド)より低くすると、内部ダイオードでクランプされる。この製品は $V_{SG}$ (ユニポーラ・モードのグランド)より低い電圧を加えても、ラッチアップを起こさずに $40mA以上の入力電流を処理することができる。これらのピンは<math>V_{CC}$ にクランプされない。Note 5: 注記がない限り、 $V_{CC}$ =5 $V_{CC}$ 5 $V_{CC}$ 6 $V_{CC}$ 7 $V_{CC}$ 8 $V_{CC}$ 9 $V_{C$

Note 6: 推奨動作条件。

Note 7:設計で保証されているが、テストされていない。 Note 8:直線性、オフセット、およびフルスケール仕様は、ユニポーラ・モードとバイポーラ・モードに適用される。

Note 9: 積分非直線性は伝達曲線の実際のエンドポイントを通過する直線からのコードの偏差として定義される。偏差は量子化幅の中心から測定される。 Note 10: バイボーラ・オフセットは、出力コードが0000 0000 0000と1111 1111 1111の間で変化するときに、 - 0.5LSBから測定したオフセット電圧。 Note 11:CONVの立上りエッジで変換を開始する。ピット決定点でCONVが "L"に戻る場合は、小さな誤差が生じる可能性がある。最高の性能を得るため に、CONVが変換開始(すなわち、最初のビット決定前)または14クロック・サイクルから120ns以内に、"L"に戻るようにする(図13のタイミング図)。

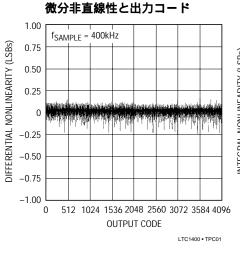

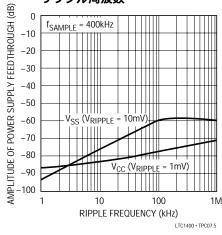

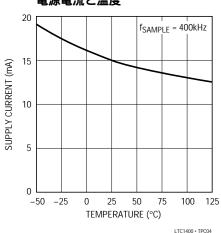

### 標準的性能特性

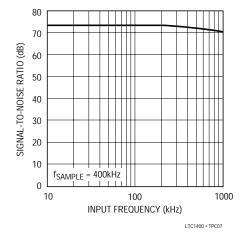

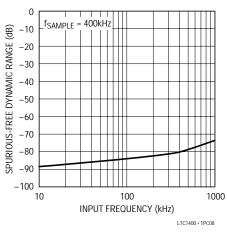

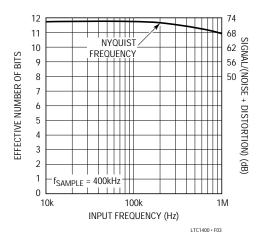

#### SN**比(高調波なし)** と入力周波数

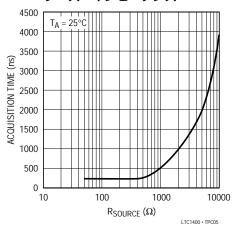

アクイジション・タイムと ソース・インピーダンス

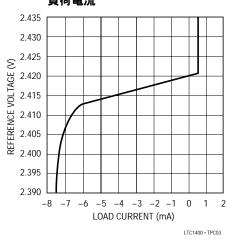

リファレンス電圧と 負荷電流

電源電流と温度

### ピン機能

$V_{CC}$ (ピン1):正電源、5V。GNDにバイパスします (10 $\mu$ Fタンタルと0.1 $\mu$ Fセラミックを並列に接続)。

A<sub>IN</sub>(ピン2): アナログ入力。0V~4.096V(ユニポーラ)、±2.048V(バイポーラ)。

$V_{REF}$ (ピン3): 2.42Vリファレンス出力。GNDにバイパスします(10 $\mu$ Fタンタルと0.1 $\mu$ Fセラミックを並列に接続)。

GND(ピン4): グランド。GNDはアナログ・グランド・プレーンに直接接続しなければなりません。

$D_{OUT}($ ピン5): このピンからA/D変換結果がシフトアウトされます。

CLK(ピン6): クロック。このクロックはシリアル・データ 転送を同期します。50nsの最小CLKパルスによって、ADCは ナップまたはスリープ・モードからウェイクアップします。

CONV(ピン7): 変換開始信号。このアクテイプ"H"信号は、立上りエッジで変換を開始します。CLKを"L"にしたまま、CONVに2回/4回パルスを印加すると、ADCはナップまたはスリープ・モードに入ります。

$V_{SS}($  ピン8): 負電源。- 5Vでバイポーラ動作を選択します。  $0.1\mu$ Fのセラミック・コンデンサでGNDにバイパスしてください。 $V_{SS}$ をGNDに接続すると、ユニポーラ動作が選択されます。

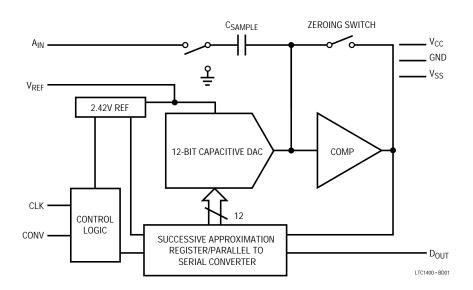

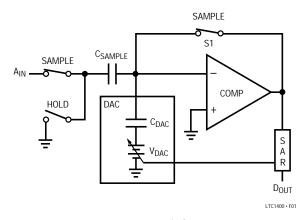

### 機能ブロック図

# テスト回路

LTC1400 • TC01

#### 変換の詳細説明

LTC1400は、逐次比較アルゴリズムと内部サンプル・ホールド回路を使用し、高精度内部リファレンスに基づいて、アナログ信号を12ビットのシリアル出力に変換します。コントロール・ロジックにより、3本の伝送線を接続して、簡単にマイクロプロセッサやDSPにインタフェースすることができます。

CONV入力の立上りエッジで変換を開始します。変換がスタートすると、逐次比較レジスタ(SAR)がリセットされます。一度変換サイクルが始まると、再スタートすることはできません。

変換中は、内部の12ビット容量性DAC出力が最上位ビッ ト(MSB)から最下位ビット(LSB)にSARでシーケンスさ れます。図1を参照すると、AIN入力はアクイジション・ フェーズ中に、サンプル・ホールド・コンデンサに接続さ れ、コンパレータ・オフセットはフィードバック・スイッチ によってゼロになります。このアクイジション・フェーズ では、サンプル・ホールド・コンデンサがアナログ入力を収 集するのに標準200nsを要します。変換フェーズでは、コン パレータのフィードバック・スイッチがオープンして、コ ンパレータを比較モードにします。入力スイッチは CSAMPLEをグランドに切り替えて、アナログ入力電荷をコ ンパレータの加算点に送ります。この入力電荷は、容量性 DACから供給されるバイナリ・ウェイト電荷と逐次比較 されます。ビットの決定は高速コンパレータで行われま す。変換が終わると、DAC出力はAIN入力電荷と平衡しま す。入力信号を表すSAR成分(12ビット・データ・ワード)が シリアル・ピンDOUTを通して出力されます。

**図**1. A<sub>IN</sub>入力

#### ダイナミック特性

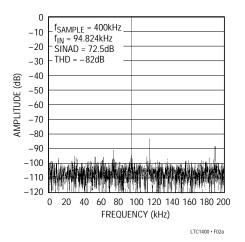

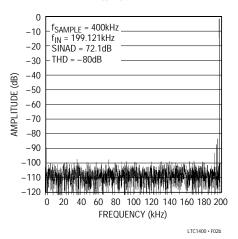

LTC1400は非常に高速なサンプリング能力を備えています。ADCの定格スループットにおける周波数応答、歪み、およびノイズの特性をテストするために、FFT(高速フーリェ変換)テスト・テクニックを使用しています。低歪み正弦波を加え、FFTアルゴリズムを用いてデジタル出力を分析することにより、基本成分外の周波数に対するADCのスペクトル成分を調べることができます。図2aに標準LTC1400 FFTのプロットを示します。

#### SNtt

SN+歪み比[S(N+D)]は、A/D出力における基本入力 周波数のRMS振幅と他のすべての周波数成分のRMS振幅との比率です。出力はDCからサンプリング周波数の 1/2の周波数帯域に限定されます。図2aに400kHzのサン プリング・レートと100kHz入力での標準スペクトル成 分を示します。図2bに示すとおり、ダイナミック特性は 入力周波数が200kHzのナイキスト限界まで良好です。

図2a. LTC1400のバイポーラ・モードにおける100kHz 入力周波数での非平均化4096ポイントFFTプロット

#### 有効ビット数

有効ビット数(ENOB)はADCの実効分解能の尺度であり、次式のとおりS(N+D)に直接関係します。

$$N = \frac{S/(N+D) - 1.76}{6.02}$$

図2b. LTC1400のバイポーラ・モードにおける200kHz 入力周波数での非平均化4096ポイントFFTプロット

ここで、Nは分解能の有効ビット数であり、S(N+D)はdBで表されます。400kHzの最大サンプリング・レートで、LTC1400は200kHzのナイキスト入力周波数まで、非常に良好なENOBを維持します(図3を参照)。

図3. バイポーラ・モードでの有効ビット数 およびSN+歪みと入力周波数

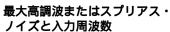

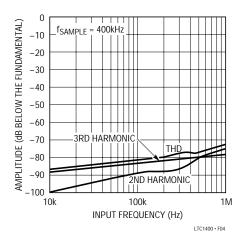

#### 全高調波歪み

全高調波歪み(THD)は、入力信号のすべての高調波のRMSの合計と基本波との比率です。帯域外高調波はDCとサンプリング周波数の1/2の周波数帯域に限定されます。THDは次式で表されます。

THD =

$$20\log \frac{\sqrt{V2^2 + V3^2 + V4^2 + ... Vn^2}}{V1}$$

ここで、V1は基本周波数のRMS振幅であり、V2からVN は第2高調波から第N高調波の振幅です。THDと入力周波数の関係を図4に示します。LTC1400はナイキストおよびそれを超える周波数まで良好な歪み特性を有しています。

図4. バイポーラ・モードでの歪みと入力周波数

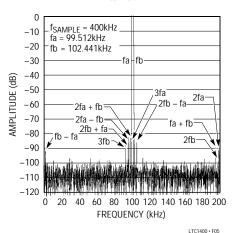

#### 混変調歪み

ADC入力信号が2つ以上のスペクトル成分からなるときには、ADC伝達関数の非直線性によって、THDに加えて混変調(IMD)が発生する可能性があります。IMDは別の異なる周波数の正弦波入力が現れたときに、ある正弦波入力に起こる変化です。

ADC入力にfaとfbの2つの周波数の純粋な正弦波が供給されると、ADC伝達関数の非直線性によって、和および差の周波数mfa±nfbに歪み成分が形成されます。ただし、mおよびn=0、1、2、3、...です。たとえば、2次IMDの項は(fa+fb)、(fa-fb)、3次IMDの項は(2fa+fb)、(2fa-fb)、(fa-2fb)です。2つの入力正弦波の振幅が等しい場合、2次IMD積の値(dB)は次式で表すことができます。

図5. バイポーラ・モードでの混変調歪みプロット

図5に100kHz入力におけるIMD性能を示します。

#### 最大高調波またはスプリアス・ノイズ

最大高調波つまり最大スプリアス・ノイズは、入力信号 とDCを除く最大スペクトル成分です。この値はフルス ケール入力信号のRMS値に対するdBで表されます。

#### フルパワーおよび最大直線帯域幅

フルパワー帯域幅はフルスケール入力信号を供給したときに、再生される基本成分の振幅が3dBだけ低下する入力周波数です。

最大直線帯域幅は、S(N+D)が68dB(有効ビット11ビット)に低下する入力周波数です。LTC1400は入力帯域幅が最大になるように設計されており、ADCは入力信号をコンバータのナイキスト周波数より高い周波数でアンダーサンプルすることができます。ノイズ・フロアは高周波数でも非常に低く、ナイキスト周波数よりはるかに高い周波数では、S(N+D)では歪みが大きな部分を占めます。

#### アナログ入力のドライブ

LTC1400のアナログ入力は簡単にドライブできます。入力電流は、変換終了時にサンプル・ホールド・コンデンサを充電する間に1つだけ小さな電流スパイクを発生します。変換中、アナログ入力にはわずかなリーク電流しか流れません。必要な条件は、アナログ入力をドライブするアンプが、小さな電流スパイクが発生した後、次の変換がスタートする前に安定しなければならないことだけです。200ns以内に小さな負荷過渡電流に安定するオペアンプであれば、最大速度での動作が可能です。低速オペアンプを使用する場合、変換

と変換の間の時間を長くすれば、セトリングのための時間を長くとることができます。このADCのA<sub>IN</sub>入力のドライブには、LT®1360およびLT1363のオペアンプが適しています。

LTC1400はユニポーラ/バイポーラ検出回路を内蔵しています。V<sub>SS</sub>電位を強制的にGNDより低くすると、内部回路が自動的にバイポーラ・モードに切り替わります。

以下のリストはLTC1400をドライブするのに適したオペアンプをまとめたものです。より詳細な情報は、リニアテクノロジーのデータブックおよびLinearView<sup>TM</sup> CD-ROMで提供されます。

LT1215/LT1216: デュアルおよびクワッド、23MHz、50V/μs単一電源オペアンプ。単一5V~±15V電源、6.6mA 仕様、0.5LSBへのセトリング・タイム90nsのセトリング。

LT1223: 100MHzビデオ電流帰還アンプ。 ±5V~ ±15V 電源、6mAの電源電流。400kHzまでおよびそれ以上で低歪み。低ノイズ。ACアプリケーションに適する。

LT1227: 140MHzビデオ電流帰還アンプ。 ±5V~±15V 電源、消費電流10mA。400kHz以上の周波数で歪みが最 小。低ノイズ。ACアプリケーションに最適。

LT1229/LT1230: デュアルおよびクワッド100MHz電流 帰還アンプ。 ± 2V ~ ± 15V電源、各アンプの消費電流 6mA。低ノイズ。良好なACスペック。

LT1360:37MHz電圧帰還アンプ。±5V~±15V電源。 消費電流3.8mA。良好なACおよびDCスペック。0.5LSB へのセトリング・タイム70ns。

LT1363:50MHz、450V/ $\mu$ sオペアンプ。 $\pm$ 5V ~  $\pm$ 15V電源。消費電流6.3mA。良好なACおよびDCスペック。0.5LSBへのセトリング・タイム60ns。

LT1364/LT1365: デュアルおよびクワッド50MHz、 $450V/\mu$ sオペアンプ。  $\pm 5V \sim \pm 15V$ 電源、1アンプ当たり消費電流6.3mA。0.5LSBへのセトリング・タイム60ns。

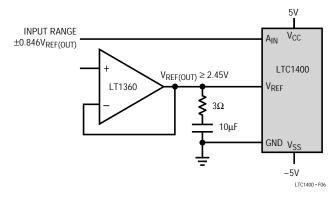

#### 内部リファレンス

LTC1400は、温度補償および曲線補正されたバンドギャップ・リファレンスを内蔵しており、このリファレンスは製造時に2.42Vに調整されています。このリファレンスは内部で

DACに接続され、ピン3から外部に引き出されており、外部負 荷に1mAまでの電流を供給可能です。コード・トランジショ ン・ノイズを最小限に抑えるために、リファレンス出力はコ ンデンサでデカップリングし、リファレンスから広帯域ノイ ズをフィルタしなければなりません( 0.1μFのセラミック・コ ンデンサと並列に10uFのタンタル・コンデンサを接続 b.バイ ポーラ・モードでは、DACまたは他の方法でVRFFピンをドラ イブして、入力スパン調整を行うことができます。VRFFピン は内部リファレンスとの衝突を避けるために、最低でも 2.45V以上にドライブしなければなりません。リファレンス は5V以上にドライブしてはなりません。図6にリファレン ス・ピンをLT1360オペアンプでドライブする回路を示しま す。また、図7に標準的なリファレンスLT1019A-5をLTC1400 に接続した回路を示します。これにより、ドリフトが改善さ れ(LT1019A-5の最大5ppm/ に等しくなる) ± 4.231Vのフル スケールになります。VRFFを2.42V以下に強制した場合、シリ アル・データ出力のREFRDYビットは'L'になります。

図6. V<sub>REF</sub>をLT1360オペアンプでドライブ

図7. LT1019A-5でLTC1400に5Vリファレンス電圧を供給

#### ユニポーラ/バイポーラ動作と調整

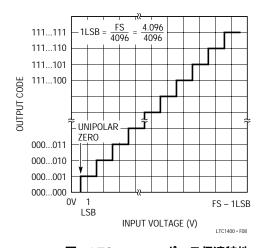

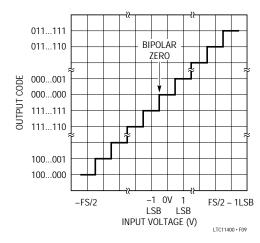

図8にLTC1400の理想的な入出力特性を示します。コード・トランジションは、連続する整数のLSB値の間の中間(すなわち、0.5LSB、1.5LSB、2.5LSB、...FS - 1.5LSB)に現れます。出力コードは、1LSB = 4.096/4096 = 1mVの自然バイナリです。図9に、2の補数形式で表したバイポーラ・モードでの入出力伝達特性を示します。

**図**8. LTC1400ユニポーラ伝達特性

**図**9. LTC1400**バイポーラ伝達特性**

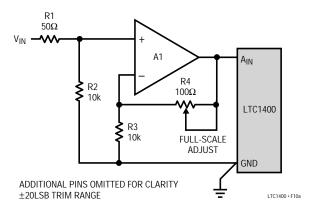

ユニポーラ・オフセットとフルスケール誤差調整 絶対精度が重要なアプリケーションの場合、オフセット とフルスケール誤差をゼロに調整できます。図10aにフ ルスケール誤差調整に必要な追加部品を示します。図

**図**10a. LTC1400フルスケール調整回路

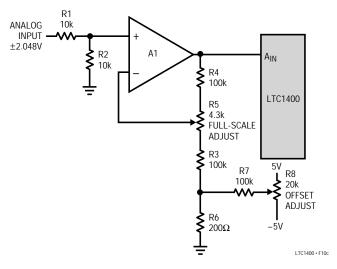

図10b. LTC1400オフセットおよびフルスケール調整回路

図10c. LTC1400バイポーラ・オフセットおよび フルスケール調整回路

10bにオフセットおよびフルスケール調整を示します。フルスケール誤差を調整する前に、オフセット誤差を調整しなければなりません。オフセット誤差をゼロにするには、0.5mV(すなわち、0.5LSB)を入力に印加し、LTC1400の出力コードが0000 0000 0000 00000 0000 0001 の間で変化するまで、オフセット・トリム抵抗を調整します。また、フルスケール誤差をゼロにするには、4.0945Vのアナログ入力(すなわち、FS - 1.5LSBまたは最後のコード・トランジション)を入力に印加し、LTC1400の出力コードが1111 1111 1111 の間で変化するまで、抵抗R5を調整します。

#### バイポーラ・オフセットとフルスケール誤差調整

バイポーラ・オフセットおよびフルスケール誤差は、ユニポーラの場合と同様に調整されます。バイポーラ・オフセット誤差調整は、 - 0.5mV( - 0.5LSB)の入力電圧を図10cの入力に印加し、ADCの出力コードが0000 0000 0000と1111 1111 1111の間で変化するまでオペアンプを調整して行います。フルスケール調整を行うには、2.0465Vの入力電圧(FS - 1.5LSB)を入力に印加し、出力コードが0111 1111 1110と0111 1111 1111の間で変化するまでR5を調整します。

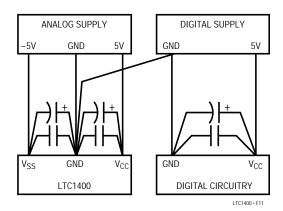

#### ボード・レイアウトとバイパス

LTC1400から最適な性能を引き出すには、PCボードが必要です。PCボードのレイアウトでは、デジタルおよびアナログ信号ラインができるだけ離れていなければなりません。特にADCの下やアナログ信号トラックに沿ってデジタル・トラックを走らせないよう注意してください。アナログ入力はGNDで遮蔽しなければなりません。

$V_{CC}$ および $V_{REF}$ ピンには、本データシートの最初のページにある標準的応用例に示すように、高品質のタンタルおよびセラミック・バイパス・コンデンサを使用してください。バイポーラ・モードの場合、 $0.1\mu$ Fのセラミック・コンデンサで $V_{SS}$ ピンへの十分なバイパスが得られます。最適な性能を得るには、 $V_{CC}$ ピンと $V_{REF}$ ピンに10 $\mu$ F表面実装AVXコンデンサと $0.1\mu$ Fセラミック・コンデンサを接続してください。これらのコンデンサはできる限りピンの近くに配置する必要があります。ピンおる限り短く、また幅を広くとってください。ユニポーラ・モード動作では、 $V_{SS}$ をノイズ発生源から分離してから、GNDピンに短絡しなければなりません。

A<sub>IN</sub>の入力信号リードおよびGND(ピン4)からの信号リターン・リードは、できるだけ短くして、入力ノイズの結合を最小にします。これができないアプリケーションの場合には、ソースとADCの間にシールド・ケーブルを使ってください。また、信号ソースとADC間のグランドの電位差は入力信号と直列に誤差電圧として現れるため、できるだけグランド回路のインピーダンスが低くなるよう配慮が必要です。

図11. 電源接続

図11に推奨されるシステム・グランド接続を示します。すべてのアナログ回路グランドは、LTC1400のGNDピンで終端する必要があります。LTC1400のピン4から電源へのグ

ランド・リターンは、ノイズのない動作を実現するために低インピーダンスでなければなりません。デジタル回路のグランドは、デジタル電源コモンに接続してください。

ADCのデータ出力と制御信号が常時アクティブであるマイクロプロセッサ・バスに接続されるアプリケーションでは、変換結果に誤差が生じることがあります。これらの誤差は、マイクロプロセッサから逐次比較コンパレータへのフィードスルーによるものです。この問題は、変換中にマイクロプロセッサをWaitステートにするか、またはスリーステート・バッファを使ってADCのデータ・バスを分離すれば解決できます。

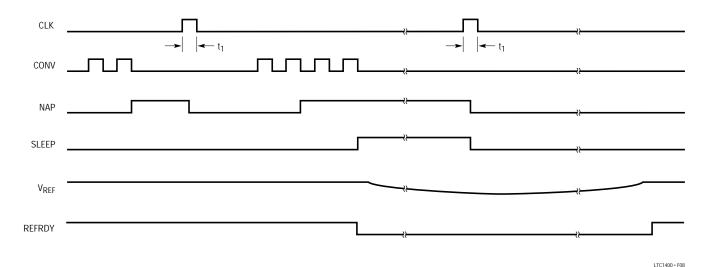

#### パワーダウン・モード

パワーアップ時に、LTC1400はアクテイブ状態に初期化され、変換を行う準備が整います。しかし、このチップはCLK およびCONV信号の所定の組合せによって、簡単にナップ・モードまたはスリープ・モードにすることができます。ナップ・モードでは、内部リファレンスを除くすべての電源がオフになります。内部リファレンスはアクティブのままで、他の回路に2.42Vの出力電圧を供給します。このモードでは、ADCは75mWではなく6mWを消費します(消費電力を抑えるには、ロジック入力が電源レールの500mV以内になければなりません)、ナップ・モードからアクテイブ・モードへのウェイクアップ時間は350nsです。スリープ・モードでは、リ

NOTE: NAP AND SLEEP ARE INTERNAL SIGNALS. REFRDY APPEARS AS A BIT IN THE DOLLT WORD.

図12. ナップ・モードおよびスリープ・モード波形

ファレンスを含むすべての内部回路への電源をオフにし、 消費電力が最小限に低減されます。図12にLTC1400をパワー ダウンする方法を示します。チップはCLK信号を'L'にした ままでCONV信号を2回送れば、ナップ・モードに入ること ができます。スリープ・モード動作にするには、CLKを'L'に したままで、CONV信号を4回送らなければなりません。

LTC1400は簡単にアクテイブ・モードに戻すことができます。CLKの立上りエッジでLTC1400がウェイクアップします。スリープ・モードからアクテイブ・モード移行時のV<sub>REF</sub>電圧のランプアップ時間は、負荷条件によって決まります。10μFのバイパス・コンデンサを接続した場合、スリープ・モードからのウェイクアップ時間は標準で4msです。リファレンスが安定し、A/D変換を実行できる状態になると、REFRDY信号がアクティブになります。このREFRDYビットがD<sub>OUT</sub>ピンに出力されてから、残りのA/D変換コードが出力されます。

デジタル・インタフェース

デジタル・インタフェースには、3本のデジタル・ラインしか必要ありません。CLKとCONVは両方とも入力で、DOUT出力は変換結果をシリアル形式で供給します。

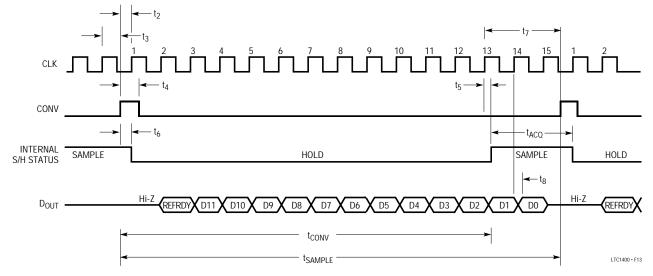

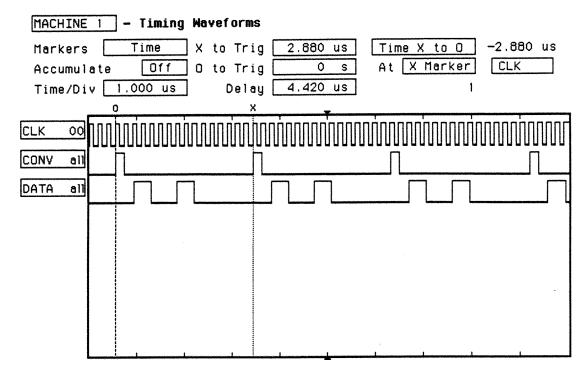

図13にA/D変換中のLTC1400のデジタル・タイミング図を示します。CONVの立上リエッジで変換が開始されます。一度変換を開始すると、変換が完了するまで再スタートすることはできません。CONV信号からCLKの立上リエッジまでの時間が $t_2$ 以下の場合、デジタル出力は1クロック・サイクルだけ遅れます。

デジタル出力データは、CLKラインの立上りエッジで更新されます。D<sub>OUT</sub>データもCLKの立上りエッジで受信システムが取り込まなければなりません。D<sub>OUT</sub>ラインのデータは、取り込みができるようにCLKの立上りエッジから最小時間t<sub>10</sub>の間は有効になっています。

図13. ADCデジタル・タイミング図

図14. CLKからD<sub>OUT</sub>の遅延

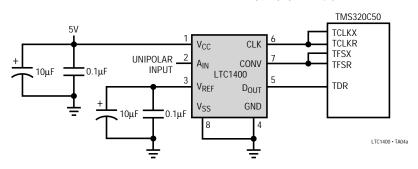

TMS320C50のTDMシリアル・ポートへのハードウェア・インタフェース(フレーム同期はTFSXから生成)

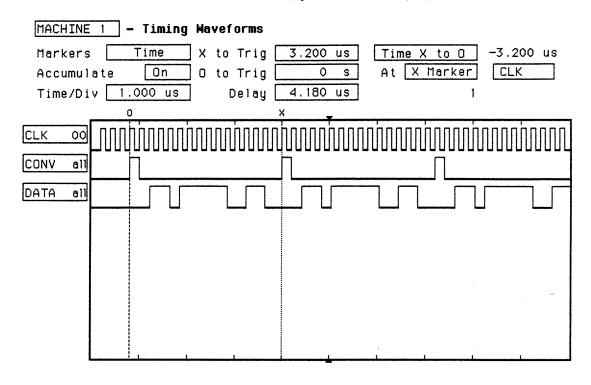

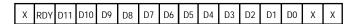

3.2μsスループット・レートを示すロジック・アナライザ波形(入力電圧=3.046V、出力コード=1011 1110 0110=3046<sub>10</sub>)

TMS320C50のTRCVレジスタにロードされたLTC1400からのデータ

TMS320C50のメモリに格納されたデータ(右寄せフォーマット)

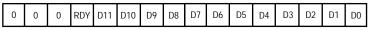

| 0 | 0 | 0 | RDY | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

|---|---|---|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|--|

|---|---|---|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|--|

#### 回路用のTMS320C50コード

| THIS PF     | ROGRAM D             | EMONSTRA     | TES LTC1400 INTERFACE TO TMS320C50        | *Start Se       | rial Communicati    | on*                                              |

|-------------|----------------------|--------------|-------------------------------------------|-----------------|---------------------|--------------------------------------------------|

|             | FRAME                | SYNC PULS    | SE IS GENERATED FROM TFSX                 | SACL            | TDXR                | ; Generate frame sync pulse                      |

| *Initializa | ation*               |              |                                           | SPLK            | #040h, IMR          | ; Turn on TRNT receiver interrupt                |

| mm.         |                      |              | ; Defines global symbolic names           |                 | INTM                | ; Enable interrupt                               |

|             |                      | nemory to ze |                                           | CLRC            | SXM                 | ; For Unipolar input, set for right shift        |

| , IIIIIa    | .ds                  | 0F00h        | ; Initialize data to zero                 |                 |                     | ; with no sign extension                         |

| DATA0       | .us<br>.word         | 0            | ; Begin sample data location              | MAR             | *AR7                | ; Load the auxiliary register pointer with seven |

|             |                      |              | , begin sample data location              | LAR             | AR7, #0F00h         | ; Load the auxiliary register seven with #0F00h  |

| DATA1       | .word                | 0            | ,                                         |                 |                     | ; as the begin address for data storage          |

| DATA2       | .word                | 0            | ; Location of data                        | WAIT:           | NOP                 | ; Wait for a receive interrupt                   |

| DATA3       | .word                | 0            | <i>i</i> •                                |                 | NOP                 | · '                                              |

| DATA4       | .word                | 0            | ; .<br>                                   |                 | NOP                 | :                                                |

| DATA5       | .word                | 0            | ; End sample data location                | SACI            | TDXR                | ; !! regenerate the frame sync pulse             |

| ; Set u     | p the ISR v          |              |                                           | В               | WAIT                | · · · · · · · · · · · · · · · · · · ·            |

|             | .ps                  | 080Ah        | ; Serial ports interrupts                 |                 |                     | ogram ;                                          |

| rint :      | B                    | RECEIVE      | ; OA;                                     | -               |                     |                                                  |

| xint :      | В                    | TRANSMI      |                                           |                 | r Interrupt Service | e Routine*                                       |

| trnt :      | В                    | TREC         | ; 0E;                                     | TREC:           |                     |                                                  |

| txnt :      | В                    | TTRANX       | ; 10;                                     | LAM             | ЛTRCV               | ; Load the data received from LTC1400            |

| ; Setup     | the reset \          | /ector       |                                           | SFR             |                     | ; Shift right two times                          |

| .ps 0       | A00h                 |              |                                           | SFR             |                     | · /                                              |

| .entry      | 1                    |              |                                           | AND             | #1FFFh, 0           | ; ANDed with #1FFFh                              |

| START:      |                      |              |                                           |                 |                     | ; For converting the data to right               |

| *TMC22      | C050 Initial         | ization*     |                                           |                 |                     | ; justified format                               |

|             |                      |              | mnorarily disable all interrupts          |                 |                     |                                                  |

|             | : INTM               |              | mporarily disable all interrupts          | SACL            | *+, 0               | ; Write to data memory pointed by AR7 and        |

| LDP         |                      |              | t data page pointer to zero               |                 |                     | ; increase the memory address by one             |

|             |                      | PIVIST ; Se  | t up the PMST status and control register | LACC            | AR7                 |                                                  |

| LACC        |                      |              |                                           |                 | #0F05h,0            | ; Compare to end sample address #0F05h           |

|             | MCWSR                | ; Se         | t software wait state to 0                |                 |                     | ; If the end sample address has exceeded jump    |

| SAIVII      | MPDWSR               | ;            |                                           | 20.12           | 2.1301, 024         | to END_TRCV                                      |

| *Configu    | re Serial Po         | ort*         |                                           |                 |                     | ·                                                |

|             | #0038h,              |              | t TDM Serial Port                         | SDI K           | #040h, IMR          | ; Else Re-enable the TRNT receive interrupt      |

|             | ,                    |              | M = 0 Stand Alone mode                    | RETE            |                     | ; Return to main program and enable interrupt    |

|             |                      |              | B=0 Not loop back                         |                 |                     |                                                  |

|             |                      |              | =0 16 Bits                                |                 |                     | om LTC1400, Program Jump to END_TRCV*            |

|             |                      |              | M=1 Burst Mode                            | END_TR          |                     |                                                  |

|             |                      |              | CM=1 CLKX is generated internally         |                 | #002h, IMR          | ; Enable INT2 for program to halt                |

|             |                      |              | M=1 FSX as output pin                     |                 | INTM                |                                                  |

|             |                      |              | t serial port into reset                  | SUCCESS         | S:                  |                                                  |

|             |                      |              | RST=RRST=0)                               | В               | SUCCESS             |                                                  |

| CDI N       | #00F8h, <sup>-</sup> |              | ke Serial Port out of reset               | *Fill tho !     | Inused Interrupt    | with RETE, to avoid program get "lost"*          |

| JI LI       | $\pi$ 001011,        |              | RST=RRST=1)                               | TTRANX:         |                     | with KETE, to avoid program get lost             |

| יו ומ       | #0EEEE               |              |                                           |                 |                     |                                                  |

| - SPLK      | #0FFFFh,             | IFK ; CIE    | ear all the pending interrupts            | RETE<br>RECEIVE |                     |                                                  |

|             |                      |              |                                           |                 | •                   |                                                  |

|             |                      |              |                                           | RETE            | IT                  |                                                  |

TRANSMIT: RETE INT2: B halt

; Halts the running CPU

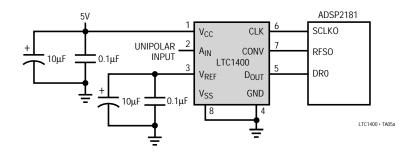

LTC1400とADSP2181のSPORT0へのインタフェース(RFS0からフレーム同期を生成)

2.88µsスループット・レートを示すロジック・アナライザ波形(入力電圧=2.240V、出力コード=1000 1100 0000=2240<sub>10</sub>)

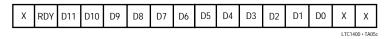

LTC1400からのデータ(ノーマル・モード)

ADSP2181のメモリに格納されたデータ(ノーマル・モード、SLEN = D)

LTC1400 • TA

#### 回路用のADSP2181コード

# THIS PROGRAM DEMONSTRATES LTC1400 INTERFACE TO ADSP-2181 FRAME SYNC PULSE IS GENERATED FROM RFS0

```

/*Section 1: Initialization*/

.module/ram/abs = 0 adspltc; /*define the program module*/

jump start;

/*jump over interrupt vectors*/

nop; nop; nop;

/*code vectors here upon IRQ2 int*/

rti; rti; rti; rti;

rti: rti: rti: rti:

/*code vectors here upon IRQL1 int*/

/*code vectors here upon IRQL0 int*/

rti; rti; rti; rti;

rti; rti; rti; rti;

/*code vectors here upon SPORT0 TX int*/

/*Section 5*/

ax0 = rx0;

dm (0x2000) = ax0; /*begin of SPORT0 receive interrupt*/

/* */

rti:

/* */

/*end of SPORT0 receive interrupt*/

rti; rti; rti; rti;

/*code vectors here upon /IRQE int*/

rti; rti; rti; rti;

/*code vectors here upon BDMA interrupt*/

/*code vectors here upon SPORT1 TX (IRQ1) int*/

rti: rti: rti: rti:

rti: rti: rti: rti:

/*code vectors here upon SPORT1 RX (IRQ0) int*/

/*code vectors here upon TIMER int*/

rti; rti; rti; rti;

/*code vectors here upon POWER DOWN int*/

rti; rti; rti; rti;

/*Section 2: Configure SPORTO*/

/*to configure SPORT0 control reg*/

/*SPORTO address = 0X3FF6*/

/*RFS is used for frame sync generation*/

/*RFS0 is internal, TFS is not use*/

/*bit 0-3 = Slen*/

/*F = 15 = 1111*/

/*E = 14 = 1110*/

/*D = 13 = 1101*/

/*bit 4,5 data type right justified zero filled MSB*/

/*bit 6 INVRFS = 0*/

/*bit 7 INVTFS = 0*/

/*bit 8 IRFS=1 receive internal frame sync*/

/*bit 9,10,11 are for TFS (don't care)*/

/*bit 12 TFSW=1 receive is Normal mode*/

/*bit 13 RTFS=1 receive is framed mode*/

/*bit 14 ISCLK internal = 1*/

/*bit 15 multichannel mode = 0*/

ax0 = 0x6B0D;

/*normal mode, bit12=0*/

/*if alternate mode bit12=1, ax0=0x7F0E*/

dm (0x3FF6) = ax0;

```

```

/*Section 3: configure CLKDIV and RFSDIV, setup interrupts*/

/*to configure CLKDIV reg*/

ax0 = 2;

dm(0x3FF5) = ax0;

/*set the serial clock divide modulus reg

SCLKDIV*/

/*the input clock frequency = 16.67MHz*/

/*CLKOUT frequency = 2x = 33MHz*/

/*SCLK= 1/2*CLKOUT*1/(SCLKDIV+1)*/

/*for SCLKDIV = 2, SCLK = 33/6 = 5.5MHz*/

/*to Configure RFSDIV*/

ax0 = 15;

/*set the RFSDIV reg = 15*/

/*=> the frame sync pulse for every 16 SCLK*/

/*if frame sync pulse in every 15 SCLK, ax0=14*/

dm(0x3FF4) = ax0;

/*to setup interrupt*/

ifc= 0x0066;

/*clear any extraneous SPORT interrupts*/

/*IRQXB = level sensitivity*/

icntl= 0;

/*disable nesting interrupt*/

imask= 0x0020:

/*bit 0 = timer int = 0*/

/*bit 1 = SPORT1 or IRO0B int = 0*/

/*bit 2 = SPORT1 or IRQ1B int = 0*/

/*bit 3 = BDMA int = 0*/

/*bit 4 = IRQEB int = 0*/

/*bit 5 = SPORT0 receive int = 1*/

/*bit 6 = SPORT0 transmit int = 0*/

/*bit 7 = IRQ2B int = 0*/

/*enable SPORT0 receive interrupt*/

/*Section 4: Configure System Control Register and Start Communication*/

/*to configure system control reg*/

ax0 = dm(0x3FFF);

/*read the system control reg*/

ay0 = 0xFFF0;

ar = ax0 AND ay0;

/*set wait state to zero*/

ay0 = 0x1000;

ar = ar OR ay0;

/*bit12 = 1, enable SPORTO*/

dm(0x3FFF) = ar;

/*frame sync pulse regenerated automatically*/

cntr = 5000;

do waitloop until ce;

nop;

nop;

nop;

nop;

nop;

nop;

waitloop: nop;

rts:

.endmod

```

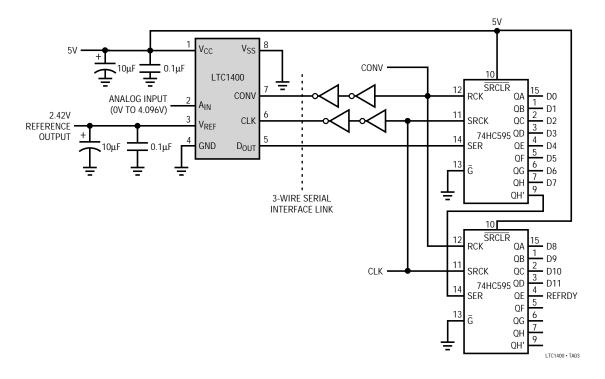

データをパラレル・フォーマットに変換するためのクイック・ルック回路

#### LTC1400とTMS320C50とのインタフェース

#### LTC1400とADSP2181とのインタフェース

# 関連製品

12ピット・パラレル出力ADC

| PART NUMBER             | SAMPLE RATE | POWER DISSIPATION | DESCRIPTION                            |

|-------------------------|-------------|-------------------|----------------------------------------|

| LTC1272                 | 250ksps     | 75mW              | Single 5V, 7572 Upgrade                |

| LTC1273/LTC1275/LTC1276 | 300ksps     | 75mW              | With Clock and Reference               |

| LTC1274/LTC1277         | 100ksps     | 10mW              | Low Power ADCs with 1µA Shutdown       |

| LTC1278/LTC1279         | 500/600ksps | 75mW              | 70dB at Nyquist, Low Power, Single 5V  |

| LTC1282                 | 140ksps     | 12mW              | 3V or ±3V ADC with Clock and Reference |

| LTC1410                 | 1.25Msps    | 150mW             | 71dB at Nyquist, Differential Input    |

12ピット・シリアル出力ADC

| PART NUMBER     | V <sub>CC</sub> | SAMPLE RATE   | POWER DISSIPATION | DESCRIPTION                                            |

|-----------------|-----------------|---------------|-------------------|--------------------------------------------------------|

| LTC1285/LTC1288 | 3V              | 7.5/6.6ksps   | 0.48mW            | 3V, One or Two Input, Micropower, SO-8                 |

| LTC1286/LTC1298 | 5V              | 12.5/11.1ksps | 1.25mV            | One or Two Input, Micropower, SO-8                     |

| LTC1290         | 5/±5V           | 50ksps        | 30mW              | 8 Input, Full-Duplex Serial I/O                        |

| LTC1296         | 5/±5V           | 46.5ksps      | 30mW              | 8 Input, Half-Duplex Serial I/O, Power Shutdown Output |