# | **ANALOG** 12/14/16ビット*nano*DAC®、デュアル、 | **DEVICES** 5ppm/℃のオンチップ電圧リファレンス付き

# AD5623R/AD5643R/AD5663R

### 特長

低消費電力、最小サイズのピン互換、デュアルnanoDAC

AD5663R:16ビット AD5643R:14ビット AD5623R:12ビット

外部または内部リファレンスの選択可能 デフォルト状態:外部リファレンス

1.25/2.5V出力、5ppm/Cのオンチップ電圧リファレンス

10ピンMSOPおよび3mm×3mm LFCSP

電源電圧: 2.7~5.5V

設計により単調増加性を保証

ゼロスケールへのパワーオン・リセット

チャンネルごとのパワーダウン

シリアル・インターフェース:最高50MHz

ハードウェアLDAC機能とCLR機能

### アプリケーション

プロセス制御

データ・アクイジション・システム バッテリ駆動の携帯型計測器 ゲインとオフセットのデジタル調整 プログラマブルな電圧源と電流源 プログラマブル減衰器

#### 概要

nanoDACファミリーのAD5623R/AD5643R/AD5663Rは、低 消費電力のデュアル12/14/16ビット・バッファ付きの電圧出力 D/Aコンバータ (DAC) です。2.7~5.5V単電源で動作し、設 計により単調増加性が保証されています。

AD5623R/AD5643R/AD5663Rはオンチップ電圧リファレンス を備えています。AD5623R-3/AD5643R-3/AD5663R-3には、 1.25V、5ppm/℃のリファレンスがあり、2.5Vのフルスケール 出力を提供します。AD5623R-5/AD5643R-5/AD5663R-5には、 2.5V、5ppm/℃のリファレンスがあり、5Vのフルスケール出力 を提供します。このオンチップ電圧リファレンスはパワーアッ プ時にオフに設定されるため、外部電圧リファレンスの使用が 可能になります。すべてのデバイスは2.7~5.5Vの単電源で動 作できます。内部リファレンスをオンにするには、DACに書込 みを行います。

これらのデバイスはパワーオン・リセット回路を内蔵してお り、DAC出力をパワーアップ時にOVに設定して、デバイスへ の有効な書込みが行われるまでその状態を維持します。5Vの電 源時にデバイスの消費電流を480nAまで低減するパワーダウン 機能を搭載しており、パワーダウン・モードではソフトウェア で選択可能な出力負荷を提供できます。

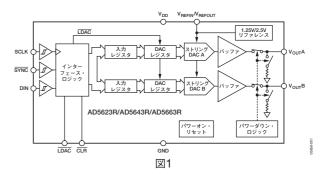

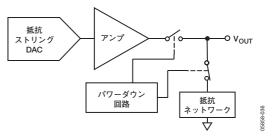

### 機能ブロック図

表1. 関連デバイス

| 製品番号   | 説明                                     |

|--------|----------------------------------------|

| AD5663 | 2.7~5.5V、デュアル16ビット<br>nanoDAC、外部リファレンス |

通常動作時の消費電力が低いため、携帯型のバッテリ駆動機器 に最適です。

AD5623R/AD5643R/AD5663Rは、最高50MHzのクロック速 度で動作する汎用3線式シリアル・インターフェースを使用し、 標準のSPI®、QSPI<sup>TM</sup>、MICROWIRE<sup>TM</sup>、DSPインターフェー ス規格と互換性があります。オンチップ高精度出力アンプによ り、レールtoレールの出力振幅が可能です。

#### 製品のハイライト

- 1. デュアル、12/14/16ビットDAC

- 2. 1.25/2.5V、5ppm/℃のオンチップ電圧リファレンス

- 3. 10ピンMSOPおよび3mm×3mmの10ピン、LFCSPパッ

- 4. 低消費電力: 3V電源時に0.6mW、5V電源時に1.25mW

- 5. AD5623Rで4.5μsの最大セトリング時間

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の 利用に関して、あるいは利用によって生じる騙こ者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有 に属します

に関いています。 ※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。 © 2006 Analog Devices, Inc. All rights reserved.

REV. A

社/〒105-6891

東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル 電話03 (5402) 8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪MTビル2号 電話06(6350)6868

# 目次

| 特長1                            | 出力アンプ20                     |

|--------------------------------|-----------------------------|

| アプリケーション1                      | 内部リファレンス20                  |

| 概要                             | 外部リファレンス20                  |

| 機能ブロック図1                       | シリアル・インターフェース20             |

| 製品のハイライト1                      | 入力シフト・レジスタ21                |

| 改訂履歴2                          | <del>SYNC</del> 割込み21       |

| 仕様                             | パワーオン・リセット22                |

| AD5623R-5/AD5643R-5/AD5663R-5  | ソフトウェア・リセット22               |

| AD5623R-3/AD5643R-3/AD5663R-35 | パワーダウン・モード22                |

| AC特性6                          | <del>LDAC</del> 機能          |

| タイミング特性7                       | 内部リファレンスの設定24               |

| タイミング図7                        | マイクロプロセッサとのインターフェース25       |

| 絶対最大定格                         | アプリケーション情報26                |

| ESDに関する注意8                     | リファレンスを電源として使用する方法26        |

| ピン配置と機能の説明9                    | AD5663Rを使用するバイポーラ動作26       |

| 代表的な性能特性10                     | 絶縁インターフェースでAD5663Rを使用する方法26 |

| 用語の説明18                        | 電源のバイパスとグラウンディング27          |

| 動作原理20                         | 外形寸法28                      |

| デジタル/アナログ部20                   | オーダー・ガイド28                  |

| 抵抗ストリング20                      |                             |

| 改訂履歴                           |                             |

| 12/06—Rev. 0 to Rev A          |                             |

| Changes to Table 2             |                             |

| Changes to Table 3             |                             |

| Changes to Figure 39           |                             |

4/06—Revision 0: Initial Version

# 仕様

### AD5623R-5/AD5643R-5/AD5663R-5

特に指定のない限り、 $V_{DD}$ =4.5~5.5V、 $R_L$ =2 $k\Omega$ (GNDに接続)、 $C_L$ =200pF(GNDに接続)、 $V_{REFIN}$ = $V_{DD}$ 、すべての仕様は $T_{MIN}$ ~  $T_{MAX}$ で規定。

#### 表2

|                           |     | Вグレ       | − ド¹                        |       |                                                       |

|---------------------------|-----|-----------|-----------------------------|-------|-------------------------------------------------------|

| パラメータ                     | Min | Тур       | Max                         | 単位    | 条件/備考                                                 |

| 静的性能2                     |     |           |                             |       |                                                       |

| AD5663R                   |     |           |                             |       |                                                       |

| 分解能                       | 16  |           |                             | ビット   |                                                       |

| 相対精度                      |     | $\pm 8$   | $\pm 16$                    | LSB   |                                                       |

| 微分非直線性                    |     |           | $\pm 1$                     | LSB   | 設計により単調増加性を保証                                         |

| AD5643R                   |     |           |                             |       |                                                       |

| 分解能                       | 14  |           |                             | ビット   |                                                       |

| 相対精度                      |     | $\pm 2$   | $\pm 4$                     | LSB   |                                                       |

| 微分非直線性                    |     |           | $\pm 0.5$                   | LSB   | 設計により単調増加性を保証                                         |

| AD5623R                   |     |           |                             |       |                                                       |

| 分解能                       | 12  |           |                             | ビット   |                                                       |

| 相対精度                      |     | $\pm 0.5$ | $\pm 1$                     | LSB   |                                                       |

| 微分非直線性                    |     |           | $\pm 0.25$                  | LSB   | 設計により単調増加性を保証                                         |

| ゼロスケール誤差                  |     | +2        | +10                         | mV    | DACレジスタに全「0」をロード                                      |

| オフセット誤差                   |     | $\pm 1$   | $\pm 10$                    | mV    |                                                       |

| フルスケール誤差                  |     | -0.1      | $\pm 1$                     | FSRの% | DACレジスタに全「1」をロード                                      |

| ゲイン誤差                     |     |           | $\pm 1.5$                   | FSRの% |                                                       |

| ゼロスケール誤差ドリフト              |     | $\pm 2$   |                             | μV/°C |                                                       |

| ゲイン温度係数                   |     | $\pm 2.5$ |                             | ppm   | FSR ∅ ppm/°C                                          |

| DC電源電圧変動除去比               |     | -100      |                             | dB    | DACコード=ミッドスケール、 $V_{DD}=5V$ ±10%                      |

| DCクロストーク<br>(外部リファレンス使用時) |     | 10        |                             | μV    | フルスケール出力の変化による $R_L=2k\Omega$ (GNDまたは $V_{DD}$ に接続)   |

|                           |     | 10        |                             | μV/mA | 負荷電流の変化による                                            |

|                           |     | 5         |                             | μV    | パワーダウンによる(各チャンネル)                                     |

| DCクロストーク<br>(内部リファレンス使用時) |     | 25        |                             | μV    | フルスケール出力の変化による $R_L = 2k\Omega$ (GNDまたは $V_{DD}$ に接続) |

|                           |     | 20        |                             | μV/mA | 負荷電流の変化による                                            |

|                           |     | 10        |                             | μV    | パワーダウンによる (各チャンネル)                                    |

|                           |     |           |                             |       |                                                       |

| 出力電圧範囲                    | 0   |           | $V_{\scriptscriptstyle DD}$ | V     |                                                       |

| 容量性負荷安定性                  |     | 2         |                             | nF    | $R_L = \infty$                                        |

|                           |     | 10        |                             | nF    | $R_L = 2k\Omega$                                      |

| DC出力インピーダンス               |     | 0.5       |                             | Ω     |                                                       |

| 短絡電流                      |     | 30        |                             | mA    | $V_{DD} = 5V$                                         |

| パワーアップ時間                  |     | 4         |                             | μs    | パワーダウン・モードからの復帰 $V_{DD}$ =5 $V$                       |

REV. A -3-

|                                                       |       | Вグレ      | √ – ド¹      |           |                                      |

|-------------------------------------------------------|-------|----------|-------------|-----------|--------------------------------------|

| パラメータ                                                 | Min   | Тур      | Max         | 単位        | 条件/備考                                |

| リファレンス入力                                              |       |          |             |           |                                      |

| リファレンス電流                                              |       | 170      | 200         | μA        | $V_{REF} = V_{DD} = 5.5V$            |

| リファレンス入力範囲                                            | 0.75  |          | $ m V_{DD}$ | V         |                                      |

| リファレンス入力インピーダンス                                       |       | 26       |             | $k\Omega$ |                                      |

| リファレンス出力                                              |       |          |             |           |                                      |

| 出力電圧                                                  | 2.495 |          | 2.505       | V         | 室温                                   |

| リファレンス温度係数3                                           |       | $\pm 5$  | $\pm 10$    | ppm/℃     | MSOPパッケージ・モデル                        |

|                                                       |       | $\pm 10$ |             | ppm/℃     | LFCSPパッケージ・モデル                       |

| 出力インピーダンス                                             |       | 7.5      |             | $k\Omega$ |                                      |

| ロジック入力 <sup>3</sup>                                   |       |          |             |           |                                      |

| 入力電流                                                  |       |          | $\pm 2$     | μA        | すべてのデジタル入力                           |

| $V_{	ext{INL}}$ (ローレベル入力電圧)                           |       |          | 0.8         | V         | $V_{DD} = 5V$                        |

| $V_{ m INH}$ (ハイレベル入力電圧)                              | 2     |          |             | V         | $V_{DD} = 5V$                        |

| ピン容量                                                  |       | 3        |             | pF        | DIN, SCLK, SYNC                      |

|                                                       |       | 19       |             | pF        | LDAC, CLR                            |

| 電源条件                                                  |       |          |             |           |                                      |

| $ m V_{DD}$                                           | 4.5   |          | 5.5         | V         |                                      |

| $I_{DD}~(\emph{/}-\emph{vn}\cdot\emph{t}-\emph{k})^4$ |       |          |             |           | $V_{IH} = V_{DD}$ および $V_{IL} = GND$ |

| $V_{DD} = 4.5 \sim 5.5 V$                             |       | 0.25     | 0.45        | mA        | 内部リファレンスをオフ                          |

| $V_{DD} = 4.5 \sim 5.5 V$                             |       | 0.8      | 1           | mA        | 内部リファレンスをオン                          |

| $I_{DD}$ (すべてのパワーダウン・モード) $^5$                        |       |          |             |           |                                      |

| $V_{DD} = 4.5 \sim 5.5 V$                             |       | 0.48     | 1           | μΑ        | $V_{IH} = V_{DD}, V_{IL} = GND$      |

<sup>|</sup> 温度範囲:Bグレードは−40~+105℃。

| 直線性は狭いコード範囲 (AD5663R: コード512~65,024、AD5643R: コード128~16,256: AD5623R: コード32~4,064) で計算しています。出力は無負荷。

| これらの仕様については出荷テストを行っていませんが、設計および特性評価により保証しています。

| インターフェースが非アクティブ、全DACがアクティブ、DAC出力が無負荷時の条件を適用しています。

| DACが2つともパワーダウン。

# AD5623R-3/AD5643R-3/AD5663R-3

特に指定のない限り、 $V_{DD}$ =2.7~3.6V、 $R_{L}$ =2 $k\Omega$ (GNDに接続)、 $C_{L}$ =200pF(GNDに接続)、 $V_{REFIN}$ = $V_{DD}$ 、すべての仕様は $T_{MIN}$ ~ $T_{MAX}$ で規定。

#### 表3

|                           |      | Bグレ       | - K1       |       |                                                     |

|---------------------------|------|-----------|------------|-------|-----------------------------------------------------|

| パラメータ                     | Min  | Тур       | Max        | 単位    | 条件/備考                                               |

| 静的性能 <sup>2</sup>         |      |           |            |       |                                                     |

| AD5663R                   |      |           |            |       |                                                     |

| 分解能                       | 16   |           |            | ビット   |                                                     |

| 相対精度                      |      | $\pm 8$   | $\pm 16$   | LSB   |                                                     |

| 微分非直線性                    |      |           | $\pm 1$    | LSB   | 設計により単調増加性を保証                                       |

| AD5643R                   |      |           |            |       |                                                     |

| 分解能                       | 14   |           |            | ビット   |                                                     |

| 相対精度                      |      | $\pm 2$   | $\pm 4$    | LSB   |                                                     |

| 微分非直線性                    |      |           | $\pm 0.5$  | LSB   | 設計により単調増加性を保証                                       |

| AD5623R                   |      |           |            |       |                                                     |

| 分解能                       | 12   |           |            | ビット   |                                                     |

| 相対精度                      |      | $\pm 0.5$ | $\pm 1$    | LSB   |                                                     |

| 微分非直線性                    |      |           | $\pm 0.25$ | LSB   | 設計により単調増加性を保証                                       |

| ゼロスケール誤差                  |      | +2        | +10        | mV    | DACレジスタに全「0」をロード                                    |

| オフセット誤差                   |      | $\pm 1$   | $\pm 10$   | mV    |                                                     |

| フルスケール誤差                  |      | -0.1      | $\pm 1$    | FSRの% | DACレジスタに全「1」をロード                                    |

| ゲイン誤差                     |      |           | $\pm 1.5$  | FSRの% |                                                     |

| ゼロスケール誤差ドリフト              |      | $\pm 2$   |            | μV/°C |                                                     |

| ゲイン温度係数                   |      | $\pm 2.5$ |            | ppm   | FSR⊘ppm/℃                                           |

| DC電源電圧変動除去比               |      | -100      |            | dB    | DACコード=ミッドスケール、 $V_{DD}=3V$<br>±10%                 |

| DCクロストーク<br>(外部リファレンス使用時) |      | 10        |            | μV    | フルスケール出力の変化による $R_L=2k\Omega$ (GNDまたは $V_{DD}$ に接続) |

|                           |      | 10        |            | μV/mA | 負荷電流の変化による                                          |

|                           |      | 5         |            | μV    | パワーダウンによる (各チャンネル)                                  |

| DCクロストーク<br>(内部リファレンス使用時) |      | 25        |            | μV    | フルスケール出力の変化による $R_L=2k\Omega$ (GNDまたは $V_{DD}$ に接続) |

|                           |      | 20        |            | μV/mA | 負荷電流の変化による                                          |

|                           |      | 10        |            | μV    | パワーダウンによる (各チャンネル)                                  |

| 出力特性 <sup>3</sup>         |      |           |            |       |                                                     |

| 出力電圧範囲                    | 0    |           | $V_{DD}$   | V     |                                                     |

| 容量性負荷安定性                  |      | 2         | 22         | nF    | $R_L = \infty$                                      |

|                           |      | 10        |            | nF    | $R_L = 2k\Omega$                                    |

| DC出力インピーダンス               |      | 0.5       |            | Ω     |                                                     |

| 短絡電流                      |      | 30        |            | mA    | $V_{DD}=3V$                                         |

| パワーアップ時間                  |      | 4         |            | μs    | パワーダウン・モードからの復帰                                     |

|                           |      |           |            | ľ     | $V_{DD} = 3V$                                       |

| リファレンス入力                  |      |           |            |       |                                                     |

| リファレンス電流                  |      | 170       | 200        | μA    | $V_{REF} = V_{DD} = 3.6V$                           |

| リファレンス入力範囲                | 0.75 |           | $V_{DD}$   | V     |                                                     |

| リファレンス入力インピーダンス           |      | 26        |            | kΩ    |                                                     |

REV. A — 5 —

|                                                                               |       | Вグレ      | /一ド <sup>1</sup> |           |                                          |

|-------------------------------------------------------------------------------|-------|----------|------------------|-----------|------------------------------------------|

| パラメータ                                                                         | Min   | Тур      | Max              | 単位        | 条件/備考                                    |

| リファレンス出力                                                                      |       |          |                  |           |                                          |

| 出力電圧                                                                          | 1.247 |          | 1.253            | V         | 室温                                       |

| リファレンス温度係数³                                                                   |       | $\pm 5$  | $\pm 15$         | ppm/℃     | MSOPパッケージ・モデル                            |

|                                                                               |       | $\pm 10$ |                  | ppm/℃     | LFCSPパッケージ・モデル                           |

| 出力インピーダンス                                                                     |       | 7.5      |                  | $k\Omega$ |                                          |

| ロジック入力 <sup>3</sup>                                                           |       |          |                  |           |                                          |

| 入力電流                                                                          |       |          | $\pm 2$          | μA        | すべてのデジタル入力                               |

| $\mathbf{V}_{	ext{INL}}$ (ローレベル入力電圧)                                          |       |          | 0.8              | V         | $V_{DD}=3V$                              |

| $\mathbf{V}_{	ext{INH}}$ (ハイレベル入力電圧)                                          | 2     |          |                  | V         | $V_{DD}=3V$                              |

| ピン容量                                                                          |       | 3        |                  | pF        | DIN, SCLK, SYNC                          |

|                                                                               |       | 19       |                  | pF        | LDAC, CLR                                |

| 電源条件                                                                          |       |          |                  |           |                                          |

| $V_{\scriptscriptstyle DD}$                                                   | 2.7   |          | 3.6              | V         |                                          |

| $I_{DD} \ (\emph{J} - \slash \emph{V} \cdot \tilde{\mathcal{T}} - \slash )^4$ |       |          |                  |           | $V_{IH} = V_{DD}$ および $V_{IL} = GND$     |

| $V_{DD} = 2.7 \sim 3.6 V$                                                     |       | 200      | 425              | mA        | 内部リファレンスをオフ                              |

| $V_{DD} = 2.7 \sim 3.6 V$                                                     |       | 800      | 900              | mA        | 内部リファレンスをオン                              |

| $I_{DD}$ (すべてのパワーダウン・モード) $^5$                                                |       |          |                  |           |                                          |

| $V_{DD} = 2.7 \sim 3.6 V$                                                     |       | 0.2      | 1                | μΑ        | $V_{IH}$ = $V_{DD}$ および $V_{IL}$ = $GND$ |

特に指定のない限り、 $V_{DD}$ =2.7~5.5V、 $R_{L}$ =2 $k\Omega$ (GNDに接続)、 $C_{L}$ =200pF(GNDに接続)、 $V_{REFIN}$ = $V_{DD}$ 、すべての仕様は $T_{MIN}$ ~ T<sub>MAX</sub>で規定。

#### 表4

| パラメータ <sup>1、2</sup>     | Min | Тур | Max | 単位             | 条件/備考3                                       |

|--------------------------|-----|-----|-----|----------------|----------------------------------------------|

| 出力電圧セトリング時間              |     |     |     |                |                                              |

| AD5623R                  |     | 3   | 4.5 | μs             | コード $1/4$ スケール~ $3/4$ スケール( $\pm 0.5$ LSB以内) |

| AD5643R                  |     | 3.5 | 5   | μs             | コード $1/4$ スケール~ $3/4$ スケール( $\pm 0.5$ LSB以内) |

| AD5663R                  |     | 4   | 7   | μs             | コード1/4スケール~3/4スケール (±2LSB以内)                 |

| スルーレート                   |     | 1.8 |     | V/µs           |                                              |

| デジタル/アナログ・グリッチ・<br>インパルス |     | 10  |     | nV-s           | メジャー・キャリー周辺の1LSBの変化                          |

| デジタル・フィードスルー             |     | 0.1 |     | nV-s           |                                              |

| リファレンス・フィードスルー           |     | -90 |     | dB             | V <sub>REF</sub> =2V±0.1Vp-p、周波数=10Hz~20MHz  |

| デジタル・クロストーク              |     | 0.1 |     | nV-s           |                                              |

| アナログ・クロストーク              |     | 1   |     | nV-s           | 外部リファレンス                                     |

|                          |     | 4   |     | nV-s           | 内部リファレンス                                     |

| DAC問クロストーク               |     | 1   |     | nV-s           | 外部リファレンス                                     |

|                          |     | 4   |     | nV-s           | 内部リファレンス                                     |

| 乗算帯域幅                    |     | 340 |     | kHz            | $V_{REF} = 2V \pm 0.1Vp-p$                   |

| 全高調波歪み                   |     | -80 |     | dB             | V <sub>REF</sub> =2V±0.1Vp-p、周波数=10kHz       |

| 出力ノイズ・スペクトル密度            |     | 120 |     | $nV/\sqrt{Hz}$ | DACコード=ミッドスケール、1kHz                          |

|                          |     | 100 |     | $nV/\sqrt{Hz}$ | DACコード=ミッドスケール、10kHz                         |

| 出力ノイズ                    |     | 15  |     | μVp-p          | 0.1~10Hz                                     |

<sup>1</sup> これらの仕様については出荷テストを行っていませんが、設計および特性評価により保証しています。 2 「用語の説明」を参照。 3 温度範囲:Bグレードは $-40\sim+105$   $\mathbb{C}$  、+25  $\mathbb{C}$  で測定。

-6-REV. A

<sup>|</sup> 温度範囲:Bグレードは-40~+105℃。

| 直線性は狭いコード範囲 (AD5663R: コード512~65,024、AD5643R: コード128~16,256: AD5623R: コード32~4,064) で計算しています。出力は無負荷。

| これらの仕様については出荷テストを行っていませんが、設計および特性評価により保証しています。

| インターフェースが非アクティブ、全DACがアクティブ、DAC出力が無負荷時の条件を適用しています。

| DACが2つともパワーダウン。

# タイミング特性

すべての入力信号は、 $t_R=t_F=1$ ns/V( $V_{DD}$ の $10\sim90$ %)で規定し、( $V_{IL}+V_{IH}$ )/2の電圧レベルからの時間とします。特に指定のない限 り、 $V_{DD}$ =2.7~5.5V、すべての仕様は $T_{MIN}$ ~ $T_{MAX}$ で規定。 $^{1}$

#### 表5

|                             | T <sub>MIN</sub> 、T <sub>MAX</sub> での限界値 |          |                              |

|-----------------------------|------------------------------------------|----------|------------------------------|

| パラメータ                       | V <sub>DD</sub> =2.7∼5.5V                | 単位       | 条件/備考                        |

| t <sub>1</sub> <sup>2</sup> | 20                                       | ns (min) | SCLKサイクル時間                   |

| $t_2$                       | 9                                        | ns (min) | SCLKハイレベル時間                  |

| $t_3$                       | 9                                        | ns (min) | SCLKローレベル時間                  |

| $t_4$                       | 13                                       | ns (min) | SYNCからSCLK立下がりエッジまでのセットアップ時間 |

| $t_5$                       | 5                                        | ns (min) | データのセットアップ時間                 |

| $t_6$                       | 5                                        | ns (min) | データのホールド時間                   |

| $t_7$                       | 0                                        | ns (min) | SCLK立下がりエッジからSYNC立上がりエッジまで   |

| $t_8$                       | 15                                       | ns (min) | SYNCの最小ハイレベル時間               |

| $t_9$                       | 13                                       | ns (min) | SYNC 立上がりエッジからSCLK立下がりエッジまで  |

| t <sub>10</sub>             | 0                                        | ns (min) | SCLK立下がりエッジからSYNC立下がりエッジまで   |

| t <sub>11</sub>             | 10                                       | ns (min) | LDACローレベル・パルス幅               |

| t <sub>12</sub>             | 15                                       | ns (min) | SCLK立下がりエッジからLDAC立上がりエッジまで   |

| t <sub>13</sub>             | 5                                        | ns (min) | CLRローレベル・パルス幅                |

| t <sub>14</sub>             | 0                                        | ns (min) | SCLK立下がりエッジからLDAC立下がりエッジまで   |

| t <sub>15</sub>             | 300                                      | ns (max) | CLRパルス起動時間                   |

<sup>&</sup>lt;sup>1</sup> これらの仕様については出荷テストを行っていませんが、設計および特性評価により保証しています。 <sup>2</sup> SCLKの最大周波数は、 $V_{\rm DD}$ =2.7 $\sim$ 5.5Vで50MHzです。

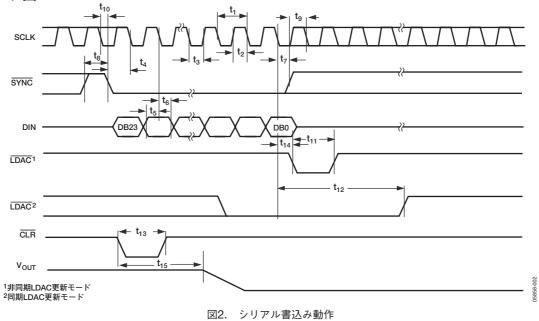

### タイミング図

REV. A

# 絶対最大定格

特に指定のない限り、T<sub>A</sub>=25℃。

#### 表6

| パラメータ                          | 定格值                               |

|--------------------------------|-----------------------------------|

| GNDに対するV <sub>DD</sub>         | $-0.3 \sim +7V$                   |

| GNDに対するV <sub>OUT</sub>        | $-0.3V \sim V_{DD} + 0.3V$        |

| GNDに対する $V_{REFIN}/V_{REFOUT}$ | $-0.3V \sim V_{DD} + 0.3V$        |

| GNDに対するデジタル入力電圧                | $-0.3V \sim V_{DD} + 0.3V$        |

| 動作温度範囲                         |                                   |

| 工業用                            | -40~+105°C                        |

| 保存温度範囲                         | -65~+150°C                        |

| ジャンクション温度(T <sub>J</sub> max)  | 150℃                              |

| 消費電力                           | $(T_{J} max - T_{A})/\theta_{JA}$ |

| LFCSP_WDパッケージ (4層ボード)          |                                   |

| $	heta_{JA}$ 熱抵抗               | 61℃/W                             |

| MSOPパッケージ(4層ボード)               |                                   |

| $	heta_{JA}$ 熱抵抗               | 142℃/W                            |

| $	heta_{ m JC}$ 熱抵抗            | 43.7℃/W                           |

| リフロー・ハンダ処理のピーク温度               |                                   |

| 鉛フリー                           | 260 (+0/−5) ℃                     |

|                                |                                   |

左記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作セクションに記 載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くと、デバイスの 信頼性に影響を与えることがあります。

### ESDに関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

—8— REV. A

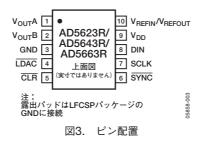

# ピン配置と機能の説明

表7. ピン機能の説明

| ピン番号 | 記号                                      | 説明                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | V <sub>OUT</sub> A                      | DAC Aからのアナログ出力電圧。出力アンプはレールtoレールで動作。                                                                                                                                                                                                                                                                                                                                                                   |

| 2    | V <sub>OUT</sub> B                      | DAC Bからのアナログ出力電圧。出力アンプはレールtoレールで動作。                                                                                                                                                                                                                                                                                                                                                                   |

| 3    | GND                                     | グラウンド。AD5623R/AD5643R/AD5663Rの全回路の基準ポイント。                                                                                                                                                                                                                                                                                                                                                             |

| 4    | LDAC                                    | このピンをローレベルに設定すると、入力レジスタに新しいデータがある場合にDACレジスタのいずれかまたはすべてを更新できます。これにより、すべてのDAC出力の同時更新が可能です。このピンを常にローレベルに固定しておくこともできます。                                                                                                                                                                                                                                                                                   |

| 5    | CLR                                     | 非同期 $\rho$ リア入力。 $\overline{\text{CLR}}$ 入力は立下がりエッジ・センシティブです。 $\overline{\text{CLR}}$ がローレベルの間、すべての $\overline{\text{LDAC}}$ パルスが無視されます。 $\overline{\text{CLR}}$ がアクティブになると、すべての入力レジスタとDACレジスタにゼロスケールがロードされ、出力は $0V$ にクリアされます。 $\overline{\text{AD5623R/AD5643R/AD5663R}}$ は、次の書込みの $\overline{\text{24}}$ 番目の立下がりエッジでクリア・コード・モードを終了します。書込みシーケンス中に $\overline{\text{CLR}}$ がアクティブになると、その書込みはアボートされます。 |

| 6    | SYNC                                    | レベル・トリガの制御入力(アクティブ・ロー)。入力データ用のフレーム同期信号です。SYNCがローレベルになると、入力シフト・レジスタがイネーブルになり、データは後続のクロックの立下がりエッジで入力されます。DACは24番目のクロック・サイクルの後に更新されます。ただし、このエッジより前にSYNCをハイレベルにすると、SYNCの立上がりエッジは割込みとして機能し、DACはこの書込みシーケンスを無視します。                                                                                                                                                                                           |

| 7    | SCLK                                    | シリアル・クロック入力。データは、シリアル・クロック入力の立下がりエッジで入力シフト・レジスタにクロック入力されます。最高50MHzのレートでデータを転送できます。                                                                                                                                                                                                                                                                                                                    |

| 8    | DIN                                     | シリアル・データ入力。このデバイスには24ビットのシフト・レジスタがあります。データは、シリアル・クロック入力の立下がりエッジでレジスタにクロック入力されます。                                                                                                                                                                                                                                                                                                                      |

| 9    | $V_{ m DD}$                             | 電源入力。 $AD5623R/AD5643R/AD5663R$ は $2.7\sim5.5V$ で動作できます。 $10\mu$ Fのコンデンサと $0.1\mu$ Fのコンデンサをこのピンと $GND$ との間に並列接続して、電源をデカップリングする必要があります。                                                                                                                                                                                                                                                                |

| 10   | V <sub>REFIN</sub> /V <sub>REFOUT</sub> | 共通のリファレンス入力/リファレンス出力。内部リファレンスを選択するとリファレンス出力ピンとなり、外部リファレンスを選択するとリファレンス入力ピンになります。このピンのデフォルトは、<br>リファレンス入力です。                                                                                                                                                                                                                                                                                            |

REV. A — 9 —

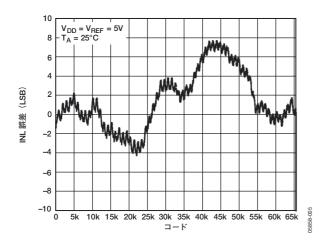

# 代表的な性能特性

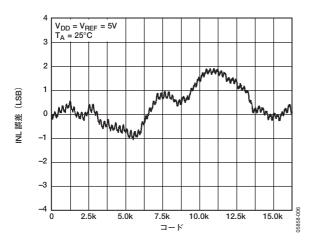

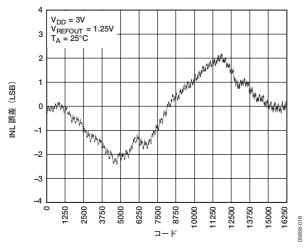

図4. INL (AD5663R、外部リファレンス)

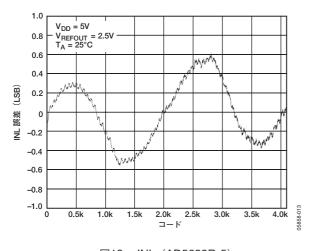

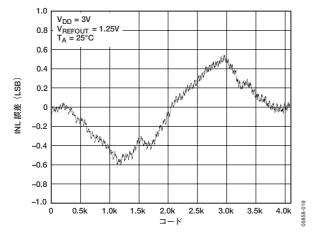

図5. INL (AD5643R、外部リファレンス)

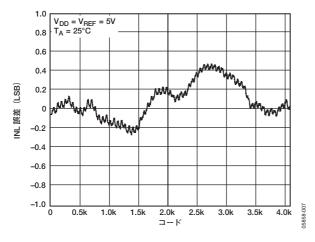

図6. INL (AD5623R、外部リファレンス)

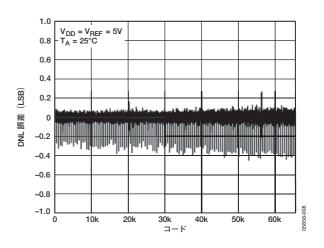

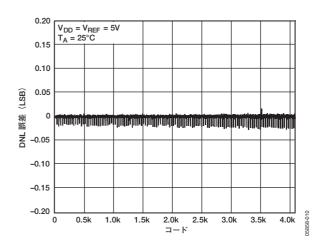

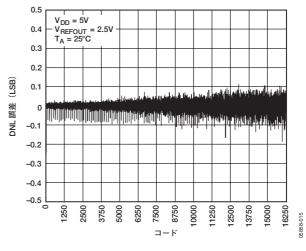

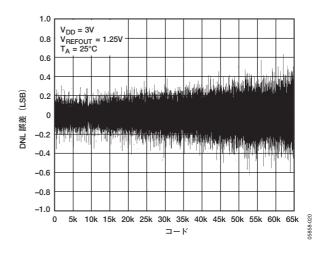

図7. DNL (AD5663R、外部リファレンス)

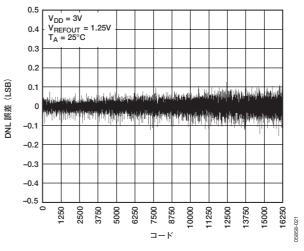

図8. DNL (AD5643R、外部リファレンス)

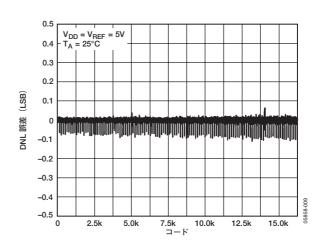

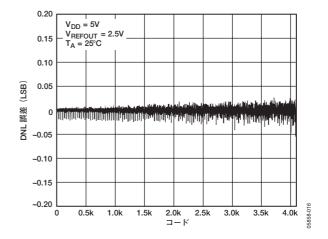

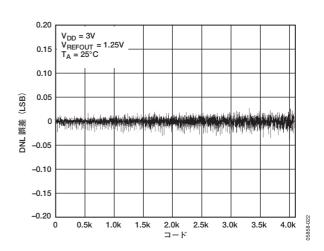

図9. DNL (AD5623R、外部リファレンス)

— 10 — REV. A

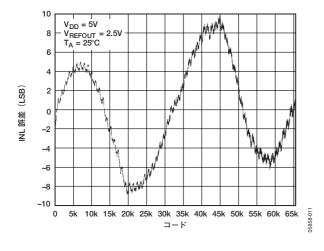

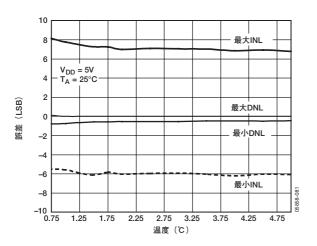

図10. INL (AD5663R-5)

図13. DNL (AD5663R-5)

図11. INL (AD5643R-5)

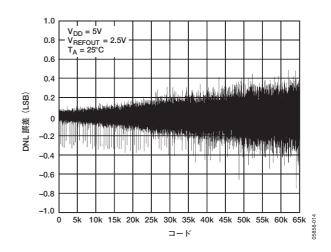

図14. DNL (AD5643R-5)

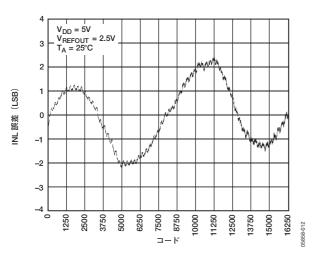

図12. INL (AD5623R-5)

図15. DNL (AD5623R-5)

REV. A — 11 —

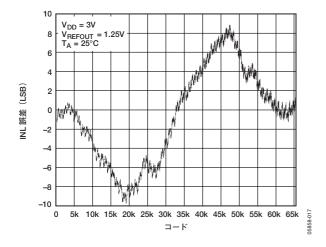

図16. INL (AD5663R-3)

図17. INL (AD5643R-3)

図18. INL (AD5623R-3)

図19. DNL (AD5663R-3)

図20. DNL (AD5643R-3)

図21. DNL (AD5623R-3)

— 12 — REV. A

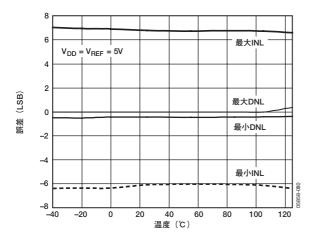

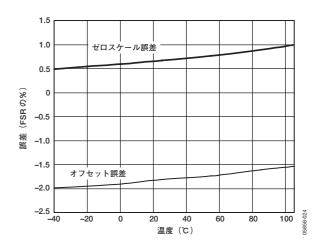

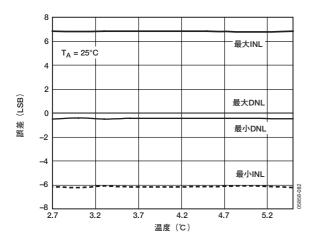

図22. INL誤差とDNL誤差の温度特性

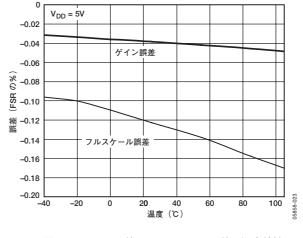

図25. ゲイン誤差とフルスケール誤差の温度特性

図23. V<sub>RFF</sub> 対 INL誤差およびDNL誤差

図26. ゼロスケール誤差とオフセット誤差の温 度特性

図24. 電源 対 INL誤差およびDNL誤差

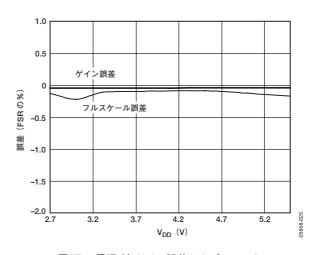

図27. 電源 対 ゲイン誤差およびフルスケール 誤差

REV. A — 13 —

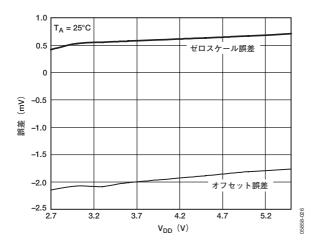

図28. 電源 対 ゼロスケール誤差およびオフ セット誤差

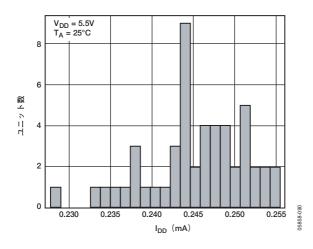

図29. I<sub>DD</sub>ヒストグラム (外部リファレンス使用 時)

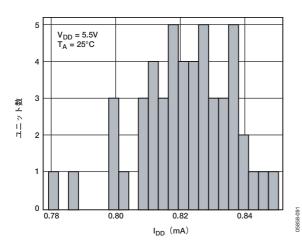

図30. I<sub>DD</sub>ヒストグラム(内部リファレンス使用 時)

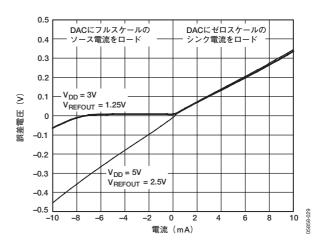

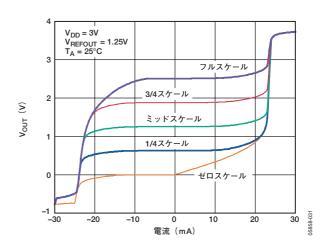

図31. ソースおよびシンク電流 対 電源レール のヘッドルーム

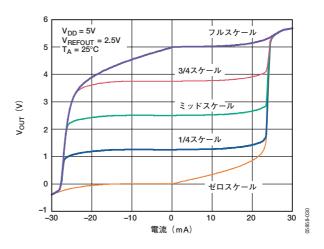

図32. AD56x3R-5のソース能力とシンク能力

図33. AD56x3R-3のソース能力とシンク能力

— 14 — REV. A

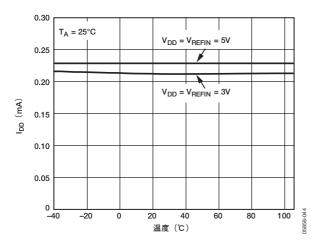

図34. 電源電流の温度特性

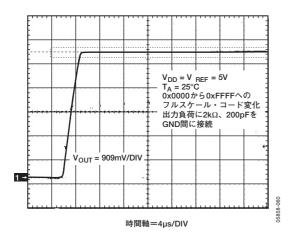

図35. フルスケールのセトリング時間(5V)

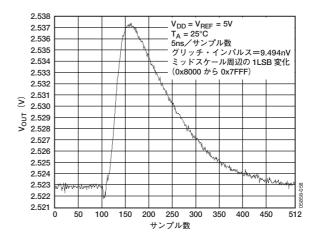

図38. デジタル/アナログ・グリッチ・インパルス (負極性)

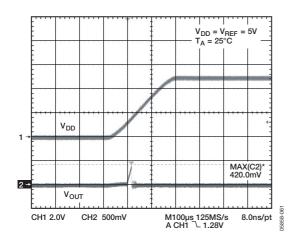

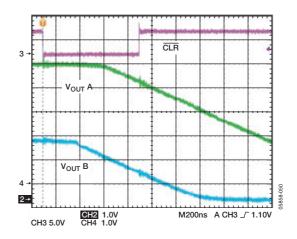

図36. 0Vへのパワーオン・リセット

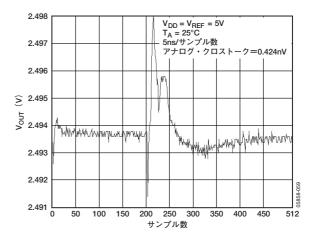

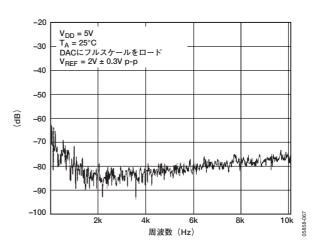

図39. アナログ・クロストーク (外部リファレンス)

REV. A — 15 —

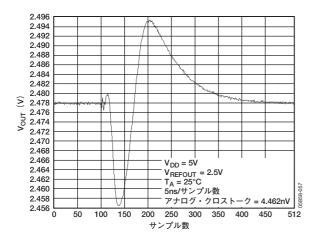

図40. アナログ・クロストーク (内部リファレンス)

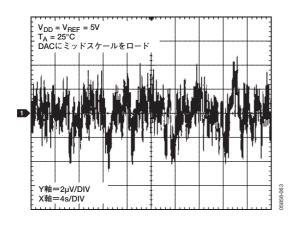

図41. 0.1~10Hz出力ノイズのプロット(外部 リファレンス)

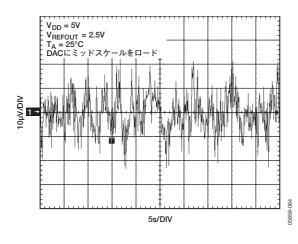

図42. 0.1~10Hz出力ノイズのプロット(内部 リファレンス)

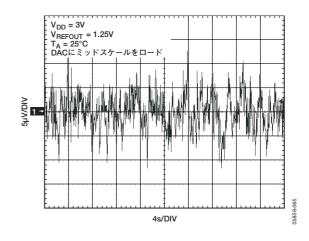

図43. 0.1~10Hz出力ノイズのプロット(内部 リファレンス)

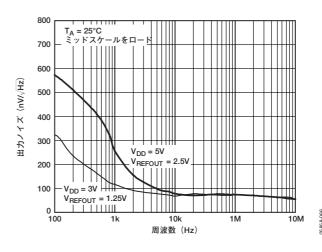

図44. ノイズ・スペクトル密度(内部リファレンス)

図45. 全高調波歪み

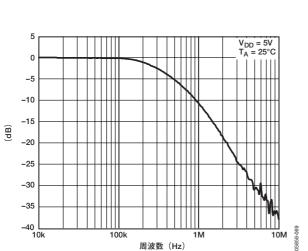

— 16 — REV. A

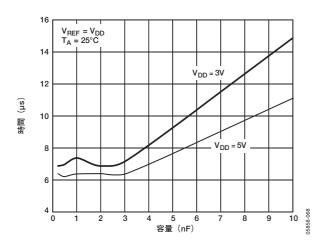

図46. 容量性負荷 対 セトリング時間

図47. 乗算帯域幅

図48. CLRパルス起動時間

REV. A — 17 —

# 用語の説明

#### 相対精度または積分非直線性(INL)

DACの場合、相対精度または積分非直線性 (INL) とは、DAC伝達関数の2つのエンドポイントを結ぶ直線からの最大偏差 (単位はLSB) を表します。代表的なコードとINLの関係を図5に示します。

#### 微分非直線性(DNL)

隣接する2つのコード間における1LSB変化の測定値と理論値の差です。微分非直線性の仕様が±1LSB以内の場合は、単調増加性が保証されています。このDACは設計により単調増加性を保証しています。代表的なコードとDNLの関係を図9に示します。

#### ゼロスケール誤差

ゼロコード(0x0000)をDACレジスタにロードしたときの出力誤差を表します。出力は理論上0Vになるはずです。AD56x3RではDAC出力が0Vよりも低くなることはないため、ゼロコード誤差は常に正の値となります。この誤差は、DACのオフセット誤差と出力アンプのオフセット誤差が原因で発生します。ゼロコード誤差はmVの単位で表します。ゼロコード誤差の温度特性を図26に示します。

#### フルスケール誤差

フルスケール・コード (0xFFFF) をDACレジスタにロードしたときの出力誤差を表します。出力は理論上 $V_{DD}$ -1LSBになるはずです。フルスケール誤差は、フルスケール・レンジの%値で表します。フルスケール誤差の温度特性を図25に示します。

#### ゲイン誤差

DACのスパン誤差を表します。これはDAC伝達特性の理論値からの実際の傾き偏差を示すもので、フルスケール・レンジの%値で表します。

#### ゼロスケール誤差ドリフト

温度変化にともなうゼロスケール誤差の変化を表し、 $\mu V/\mathbb{C}$ の単位で表します。

#### ゲイン温度係数

温度変化にともなうゲイン誤差の変化を表し、(フルスケール・レンジのppm)/℃の単位で表します。

#### オフセット誤差

伝達関数の直線領域における $V_{OUT}$  (実際の出力電圧) と $V_{OUT}$  (理想的な出力電圧) との差をmVの単位で表します。 AD56x3Rのオフセット誤差は、コード512をDACレジスタにロードして測定します。これは正または負の値となります。

#### DC電源電圧変動除去比 (PSRR)

電源電圧の変動がDACの出力に与える影響を示します。PSRR は、DACのフルスケール出力に関する $V_{OUT}$ の変動と $V_{DD}$ の変動の比を表します。これはdBの単位で測定します。 $V_{REF}$ を2Vに保持し、 $V_{DD}$ を $\pm 10\%$ のレンジで変動させます。

#### 出力電圧セトリング時間

入力がフルスケールの1/4から3/4に変化するときに、DACの出力が規定のレベルにセトリングするまでの所要時間を表し、SCLKの24番目の立下がりエッジから測定します。

#### デジタル/アナログ・グリッチ・インパルス

DACレジスタの入力コードの状態が変化したときに、アナログ出力に現れるインパルスを表します。通常、グリッチの面積として規定され、nV-sで表します。メジャー・キャリーの遷移 (0x7FFFから0x8000) 時に、デジタル入力コードが1LSB変化したときの測定値です。図38を参照。

#### デジタル・フィードスルー

DACのデジタル入力によってDACのアナログ出力に現れるインパルスの大きさですが、これはDAC出力の更新が行われていないときに測定されます。nV-sの単位で規定され、データ・バス上でのフルスケールのコード変化時、すなわち全ビット[0]から全ビット[1]に変化したとき、または全ビット[1]から全ビット[0]にコードが遷移するときに測定します。

#### リファレンス・フィードスルー

リファレンス・フィードスルーは、DAC出力の更新が行われていないとき(つまり、 $\overline{\text{LDAC}}$ がハイレベル)のDAC出力の信号振幅とリファレンス入力との比を示します。これは $\overline{\text{dB}}$ の単位で表します。

#### ノイズ・スペクトル密度

内部で発生するランダム・ノイズの測定値です。ランダム・ノイズは、スペクトル密度  $(nV\sqrt{Hz})$  として特性付けられます。この測定は、DACにミッドスケールをロードし、そのときに出力で発生するノイズを計測する方法によって行います。ノイズ・スペクトル密度のプロットを図44に示します。

#### DCクロストーク

DCクロストークは、1つのDACの出力変動に呼応して、もう1 つのDACで起こる出力レベルのDC変化です。測定では、1つのDACでフルスケール出力を変化させて(あるいはソフト・パワーダウンとパワーアップを行って)、ミッドスケールに保持されているもう1つのDACをモニタリングします。 $\mu$ V単位で表します。

負荷電流の変化によって生じるDCクロストークは、DACの負荷電流の変化がミッドスケールに保持されているもう1つのDACに及ぼす影響を表します。これは、 $\mu V/mA$ の単位で表します。

#### デジタル・クロストーク

1つのDACの入力レジスタで発生するフルスケール・コード変化(全[0]から全[1]、または全[1]から全[0]へのコード遷移)に呼応して、ミッドスケールでもう1つのDACの出力に注入されるグリッチ・インパルスです。スタンドアロン・モードで測定し、nV-s単位で表します。

#### アナログ・クロストーク

1つDACの出力変化に起因しても<u>う1つのDAC</u>の出力に注入されるグリッチ・インパルスです。 $\overline{LDAC}$ をハイレベルに保持している間に、フルスケールのコード変化(全「0」から全「1」、または全「1」から全「0」へのコード遷移)を入力レジスタの1つにロードして測定します。次いで、 $\overline{LDAC}$ をローレベルに引き込み、デジタル・コードが変化しなかったDACの出力をモニタリングします。グリッチの面積をnV-s単位で表します。

#### DAC間クロストーク

1つのDACのデジタル・コード変化とこれに続く出力変化に起因して、もう1つのDACの出力に注入されるグリッチ・インパルスです。デジタルとアナログのクロストークがあります。 $\overline{\text{LDAC}}$ をローレベルに保持している間に、DACの1つにフルスケールのコード変化(全「0」から全「1」、または全「1」から全「0」へのコード遷移)をロードし、もう1つのDACの出力をモニタリングして測定します。グリッチのエネルギーをnV-s単位で表します。

#### 乗算帯域幅

DACに内蔵されているアンプの帯域幅は有限です。乗算帯域幅はこの測定値です。リファレンス上のサイン波(フルスケール・コードをDACにロードした状態)が、出力上に現れます。乗算帯域幅は、出力振幅が入力よりも3dB低くなるときの周波数です。

#### 全高調波歪み (THD)

DACを使用して減衰したサイン波と理論的なサイン波との偏差を表します。DACのリファレンスにサイン波を使用し、DACの出力上に存在する高調波成分を測定した値がTHDになります。dBの単位で測定します。

REV. A — 19 —

# 動作原理

### デジタル/アナログ部

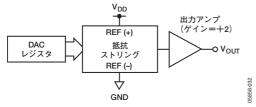

AD5623R/AD5643R/AD5663R DACは、CMOSプロセスを用いて製造されています。このアーキテクチャは、ストリングDACとその後段の出力バッファ・アンプから構成されています。図49に、DACアーキテクチャのブロック図を示します。

図49. DACアーキテクチャ

DACの入力コーディングはストレート・バイナリであるため、外部リファレンス使用時の理論的な出力電圧は次の式から求められます。

$$V_{OUT} = V_{REFIN} \times \left(\frac{D}{2^N}\right)$$

内部リファレンス使用時の理論的な出力電圧は次の式から求められます。

$$V_{OUT} = 2 \times V_{REFOUT} \times \left(\frac{D}{2^{N}}\right)$$

ここで、

Dは、DACレジスタにロードされるバイナリ・コードの10進値で、次の値になります。

AD5623R (12ビット) では0~4,095 AD5643R (14ビット) では0~16,383 AD5663R (16ビット) では0~65.535

NはDAC分解能です。

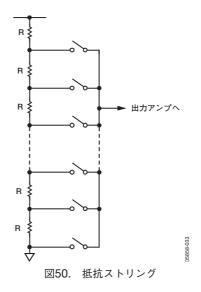

### 抵抗ストリング

図50に抵抗ストリング部を示します。これは、値がそれぞれRの抵抗によるストリングです。DACレジスタにロードされるコードに基づいて、ストリングのどのノードから電圧が出力アンプに送り込まれるかが決まります。ストリングとアンプを接続するスイッチの1つが閉じると、電圧が供給されます。抵抗のストリングであるため、単調増加性が保証されています。

#### 出力アンプ

出力バッファ・アンプは、出力上でレールtoレール電圧を生成できます。これによって、出力電圧範囲が0Vから $V_{DD}$ になります。このアンプは、GNDとの間に並列に接続した1000pFコンデンサと $2k\Omega$ の抵抗の負荷を駆動できます。出力アンプの電流ソースおよびシンク能力を図31に示します。スルーレートは $1.8V/\mu s$ で、フルスケールの1/4から3/4に変化するときのセトリング時間は10usです。

#### 内部リファレンス

AD5623R/AD5643R/AD5663Rのオンチップ電圧リファレンスは、パワーアップ時にオフであり、コントロール・レジスタへの書込みによってイネーブルになります。詳細については「内部リファレンスの設定」を参照してください。

AD56x3R-3には1.25V、5ppm/ $\mathbb C$ のリファレンスがあり、2.5Vのフルスケール出力を提供します。AD56x3R-5には2.5V、5ppm/ $\mathbb C$ のリファレンスがあり、5Vのフルスケール出力を提供します。各デバイスの内部リファレンスは、 $\mathbb V_{REFOUT}$ ピンから使用できます。リファレンス出力を使用して外部負荷を駆動する場合は、バッファが必要です。内部リファレンスを使用する場合は、リファレンスを安定させるため、リファレンス出力とGNDとの間に100nFのコンデンサを配置することを推奨します。

### 外部リファレンス

アプリケーションが必要とする場合は、AD56x3R-3とAD56x3R-5の $V_{REFIN}$ ピンから外部リファレンスを使用できます。オンチップ電圧リファレンスはパワーアップ時にオフであり、これがデフォルト状態です。AD56x3R-3とAD56x3R-5は、2.7~5.5Vの単電源から動作します。

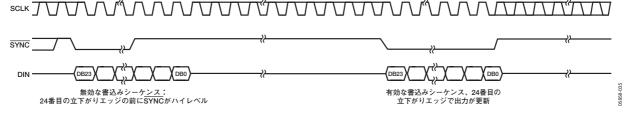

#### シリアル・インターフェース

AD5623R/AD5643R/AD5663Rには、3線式シリアル・インターフェース( $\overline{SYNC}$ 、 $\overline{SCLK}$ 、 $\overline{DIN}$ )があります。このインターフェースは、業界標準の $\overline{SPI}$ 、 $\overline{QSPI}$ 、 $\overline{MICROWIRE}$ インターフェース、および大半の $\overline{DSP}$ に適合します。代表的な書込みシーケンスのタイミング図については、図2を参照してください。

SYNCラインをローレベルにすることによって、書込みシーケンスが開始します。DINラインからのデータは、SCLKの立下がりエッジで24ビットのシフト・レジスタにクロック入力されます。最高50MHzのシリアル・クロック周波数を使用できるため、AD5623R/AD5643R/AD5663Rは高速DSPにも対応できます。クロックの24番目の立下がりエッジで、最後のデータビットがクロック入力され、プログラムされた機能(DACレジスタの内容や動作モードの変更など)が実行されます。

— 20 — REV. A

この時点で、SYNCラインをローレベルに維持するか、またはハイレベルに遷移させることができます。いずれの場合も、次の書込みシーケンスが開始される前に少なくとも15nsの間SYNCラインをハイレベルに保持しなければ、SYNCの立下がりエッジで次の書込みシーケンスを開始できません。

$\overline{\text{SYNC}}$ バッファは $V_{\text{IN}}$ =0.8Vのときよりも $V_{\text{IN}}$ =2Vのときの方が電流を多く消費するため、消費電力をさらに低減するには、書込みシーケンスが終了して次の書込みシーケンスが開始されるまでの間、 $\overline{\text{SYNC}}$ をローレベルのアイドル状態にしておきます。ただし、上述のように、次の書込みシーケンスが開始される直前には $\overline{\text{SYNC}}$ を再びハイレベルに戻す必要があります。

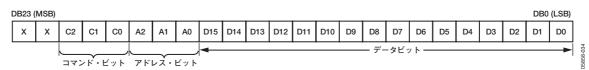

#### 入力シフト・レジスタ

入力シフト・レジスタは24ビット幅です(図52を参照)。最初の2ビットはドント・ケア・ビットで、次の3ビットはコマンド・ビットC2 $\sim$ CO(表8を参照)、その後に3ビットのDACアドレスA2 $\sim$ AO(表9を参照)、最後に16/14/12ビットのデータワードが続きます。

AD5663R/AD5643R/AD5623Rのデータワードは、それぞれ16、14、12ビットの入力コードと、それに続く0、2、4個のドント・ケア・ビットから構成されます (図51、図52、図53を参照)。データビットは、SCLKの24番目の立下がりエッジでDACレジスタに転送されます。

表8. コマンドの定義

| C2 | C1 | C0 | コマンド                                                     |

|----|----|----|----------------------------------------------------------|

| 0  | 0  | 0  | 入力レジスタ <b>n</b> への書込み                                    |

| 0  | 0  | 1  | DACレジスタnの更新                                              |

| 0  | 1  | 0  | 入力レジスタ $n$ への書込み、すべて更新(ソフトウェア $\overline{\text{LDAC}}$ ) |

| 0  | 1  | 1  | DACチャンネルnへの書込みと更新                                        |

| 1  | 0  | 0  | DACのパワーダウン (パワーアップ)                                      |

| 1  | 0  | 1  | リセット                                                     |

| 1  | 1  | 0  | LDACレジスタ・セットアップ                                          |

| 1  | 1  | 1  | 内部リファレンスの設定(オン/オフ)                                       |

表9. アドレス・コマンド

| A2 | A1 | A0 | アドレス (n) |

|----|----|----|----------|

| 0  | 0  | 0  | DAC A    |

| 0  | 0  | 1  | DAC B    |

| 0  | 1  | 0  | 予備       |

| 0  | 1  | 1  | 予備       |

| 1  | 1  | 1  | 全DAC     |

### SYNC割込み

通常の書込みシーケンスでは、SCLKの少なくとも24個の立下がりエッジの間、SYNCラインがローレベルになり、SCLKの24番目の立下がりエッジでDACが更新されます。ただし、24番目のエッジが立ち下がる前にSYNCがハイレベルになると、書込みシーケンスの割込み信号になります。このとき、シフト・レジスタがリセットされ、書込みシーケンスは無効と見なされます。DACレジスタのデータ内容は更新されず、動作モードも変更されません(図54を参照)。

図51. AD5663R入力シフト・レジスタの内容

図52. AD5643R入力シフト・レジスタの内容

図53. AD5623R入力シフト・レジスタの内容

図54. SYNCの割込み機能

REV. A

### パワーオン・リセット

AD5623R/AD5643R/AD5663Rファミリーには、パワーアップ時に出力電圧を制御するパワーオン・リセット回路があります。AD5623R/AD5643R/AD5663Rでは、パワーアップ時にDAC出力が0Vに設定され、DACへの有効な書込みシーケンスが実行されるまで出力はその状態を維持します。パワーアップ実行中のDACの出力状態を把握しておかなければならないアプリケーションでは、この機能が役立ちます。パワーオン・リセット中の $\overline{\text{LDAC}}$ や $\overline{\text{CLR}}$ のイベントは、すべて無視されます。

#### ソフトウェア・リセット

AD5623R/AD5643R/AD5663Rには、ソフトウェア・リセット機能があります。コマンド101がソフトウェア・リセット機能用に予約されています(表8を参照)。ソフトウェア・リセット・コマンドには、コントロール・レジスタのDB0ビットの設定によってソフトウェアからプログラムできるリセット・モードが2種類あります。表10は、ビットの状態とデバイスの動作モードの対応を示します。表12は、ソフトウェア・リセット動作モード中の入力シフト・レジスタの内容を示します。

表10. ソフトウェア・リセット・モード

| DB0            | 0にリセットされるレジスタ       |

|----------------|---------------------|

| 0              | DACレジスタ             |

|                | 入力レジスタ              |

| 1 (パワーオン・リセット) | DACレジスタ             |

|                | 入力レジスタ              |

|                | LDAC レジスタ           |

|                | パワーダウン・レジスタ         |

|                | 内部リファレンスの設定レジス<br>タ |

#### パワーダウン・モード

AD5623R/AD5643R/AD5663Rには4種類の動作モードがあります。コマンド100がパワーダウン機能用に予約されています (表8を参照)。これらの動作モードは、コントロール・レジスタの2つのビット (DB5とDB4) を設定することでソフトウェアからプログラムできます。表11は、この2つのビットの設定と対応するデバイスの動作モードを示します。対応する2つのビット (ビットDB1とビットDB0) を1に設定することによって、DACのいずれかまたはすべて (DAC BとDAC A) を選択したモードにパワーダウンできます。

同じコマンド100を実行し、ビットDB5とビットDB4を設定すれば、任意の組み合わせのDACを通常動作モードにパワーアップできます。

パワーアップするDACチャンネルの組み合わせを選択するには、対応する2つのビット(ビットDB1とビットDB0)を1に設定してください。パワーダウン/パワーアップ動作時の入力シフト・レジスタの内容については、表13を参照してください。

LDACがローレベルの間は、DAC出力は入力レジスタ内の値までパワーアップします。LDACがハイレベルの場合は、パワーダウン前のDACレジスタに保持されていた値までパワーアップします。

表11. 動作モード

| DB5 | DB4 | 動作モード           |

|-----|-----|-----------------|

| 0   | 0   | 通常動作            |

|     |     | パワーダウン・モード      |

| 0   | 1   | 1kΩを介してGNDに接続   |

| 1   | 0   | 100kΩを介してGNDに接続 |

| 1   | 1   | スリーステート         |

図55. パワーダウン時の出力段

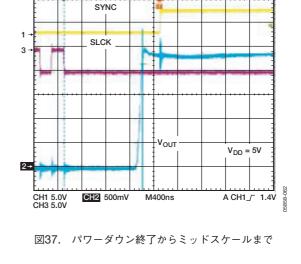

パワーダウン・モードを起動すると、バイアス・ジェネレータ、出力アンプ、抵抗ストリング、その他の関連するリニア回路がシャットダウンします。ただし、パワーダウン中にDACレジスタの内容が変わることはありません。パワーダウン・モードからの復帰時間は、一般に $V_{DD}$ =5Vでも $V_{DD}$ =3Vでも4 $\mu$ sです(図37を参照)。

表12. ソフトウェア・リセット・コマンドに対する24ビット入力シフト・レジスタの内容

| DB23~DB22 (MSB) | DB21             | DB20 | DB19 | DB18  | DB17    | DB16 | DB15~DB1   | DB0 (LSB)              |

|-----------------|------------------|------|------|-------|---------|------|------------|------------------------|

| X               | 1                | 0    | 1    | x     | x       | x    | x          | 1/0                    |

| ドント・ケア          | コマンド・ビット (C2~C0) |      |      | アドレス・ | ビット (A2 | ~A0) | ドント・<br>ケア | ソフトウェア・リセッ<br>ト・モードを指定 |

— 22 — REV. A

表13. パワーアップ/ダウン機能の24ビット入力シフト・レジスタの内容

| DB23~<br>DB22<br>(MSB) | DB21 | DB20 | DB19 | DB18            | DB17 | DB16   | DB15~<br>DB6 | DB5 | DB4   | DB3 | DB2                                    | DB1            | DB0<br>(LSB) |

|------------------------|------|------|------|-----------------|------|--------|--------------|-----|-------|-----|----------------------------------------|----------------|--------------|

| X                      | 1    | 0    | 0    | X               | X    | X      | x            | PD1 | PD0   | X   | X                                      | DAC B          | DAC A        |

| ドント・<br>ケア             |      |      |      | ス・ビッ Ì<br>ヾント・ク |      | ドント・ケア | パワード         |     | ドント・ケ | 7   | パワーダウ<br>アップする<br>の選択。ビ<br>設定してチ<br>選択 | チャンネル<br>ットを1に |              |

表14. LDACレジスタのセットアップ・コマンドに対する24ビット入力シフト・レジスタの内容

| DB23~<br>DB22<br>(MSB) | DB21 | DB20   | DB19   | DB110                       | DB17 | DB16       | DB15~DB2                       | DB1   | DB0<br>(LSB) |

|------------------------|------|--------|--------|-----------------------------|------|------------|--------------------------------|-------|--------------|

| x                      | 1    | 1      | 0      | X                           | х    | х          | x                              | DAC B | DAC A        |

| ドント・<br>ケア             | コマンド | ・ビット(( | C2~C0) | アドレス・ビット (A3~A0)、<br>ドント・ケア |      | ドント・<br>ケア | ビットを0または1に設定して、<br>必要な動作モードを指定 |       |              |

#### LDAC機能

AD5623R/AD5643R/AD5663R DACには、入力レジスタとDACレジスタの2バンクのレジスタで構成されるダブルバッファ・インターフェースがあります。入力レジスタは入力シフト・レジスタに直接接続し、有効な書込みシーケンスが終了するとデジタル・コードが該当する入力レジスタに転送されます。DACレジスタに、抵抗ストリングで使用するデジタル・コードが格納されます。

$\overline{DAC}$ レジスタへのアクセスは、 $\overline{LDAC}$ ピンによって制御します。  $\overline{LDAC}$ ピンがハイレベルのとき、 $\overline{DAC}$ レジスタはラッチされ、 $\overline{DAC}$ レジスタの内容を変えずに入力レジスタの状態を変えることができます。  $\overline{LDAC}$ がローレベルになると、 $\overline{DAC}$ レジスタが透過的になり、入力レジスタの内容が $\overline{DAC}$ レジスタに転送されます。 ダブルバッファ・インターフェースは、すべての $\overline{DAC}$ 出力を同時に更新する必要がある場合に便利です。入力レジスタの1つに別々に書込みを行い、次いで他の $\overline{DAC}$ 入力レジスタに書込みを行うときに $\overline{LDAC}$ をローレベルにすることによって、すべての出力を同時に更新できます。

この他に、最後に $\overline{\text{LDAC}}$ をローレベルにしてから入力レジスタが更新されていなければ、 $\overline{\text{DAC}}$ レジスタも更新されない機能も追加されています。通常は、 $\overline{\text{LDAC}}$ がローレベルになると、 $\overline{\text{DAC}}$ レジスタに入力レジスタの内容がロードされます。 $\overline{\text{AD5623R}}$ /AD5643R/AD5663Rの場合は、 $\overline{\text{DAC}}$ レジスタが最後に更新されてから入力レジスタの内容に変更があった場合に限り、 $\overline{\text{DAC}}$ レジスタが更新されます。これにより、不要なデジタル・クロストークがなくなります。

すべてのDACの出力を同時に更新するには、ハードウェア $\overline{\text{LDAC}}$ ピンを使用します。

#### 同期LDAC

24番目のSCLKパルスの立下がりエッジで新しいデータが読み込まれた後、DACレジスタが更新されます。図2に示すように、LDACを常にローレベルに固定するかパルスを与えることができます。

#### 非同期LDAC

入力レジスタの書込み動作と出力の更新は、同時に行われません。 $\overline{\text{LDAC}}$ がローレベルになると、 $\overline{\text{DAC}}$ レジスタが入力レジスタの内容に更新されます。

$\overline{\text{LDAC}}$ レジスタを使用すれば、ハードウェア $\overline{\text{LDAC}}$ ピンをきわめて柔軟に制御できます。このレジスタで、ハードウェア $\overline{\text{LDAC}}$ ピンの実行時に同時に更新するチャンネルの組み合わせを選択できます。 $\overline{\text{DAC}}$ チャンネルの $\overline{\text{LDAC}}$ ビット・レジスタに0を設定すると、 $\overline{\text{LDAC}}$ ピンでこのチャンネルの更新を制御できます。このビットを1に設定すると、チャンネルが同期して更新されます。すなわち、 $\overline{\text{LDAC}}$ ピンの状態とは無関係に、新しいデータが読み込まれた後で $\overline{\text{DAC}}$ レジスタが更新されます。事実上、 $\overline{\text{LDAC}}$ ピンはローレベルと見なされます。 $\overline{\text{LDAC}}$ レジスタの動作モードについては、表15を参照してください。この柔軟性は、選択したチャンネルを同時に更新し、残りのチャンネルを同期して更新したいアプリケーションで役に立ちます。

コマンド110を使用してDACに書き込むと、2ビットの $\overline{LDAC}$ レジスタ[DB1:DB0]にロードされます。各チャンネルのデフォルトは0で、 $\overline{LDAC}$ ピンは普通に動作します。ビットを1に設定すると、 $\overline{LDAC}$ ピンの状態とは無関係にDACレジスタが更新されます。 $\overline{LDAC}$ レジスタのセットアップ・コマンド実行中の入力シフト・レジスタの内容については、表14を参照してください。

表15. LDACレジスタの動作モード

| LDACビット<br>(DB1∼DB0) | LDACピン          | LDACの動作                                                                            |

|----------------------|-----------------|------------------------------------------------------------------------------------|

| 0                    | 1/0<br>x=ドント・ケア | LDACピンにより指定<br>24番目のSCLKパルスの立<br>下がりエッジで新しいデー<br>タが読み込まれた後、<br>DACレジスタが更新され<br>ます。 |

REV. A — 23 —

# 内部リファレンスの設定

オンチップ電圧リファレンスは、デフォルトではパワーアップ時にオフになります。このリファレンスのオン/オフを切り替えるには、コントロール・レジスタのソフトウェア・プログラマブル・ビットDBOを設定します。表16には、ビットの状態と動作モードの対応関係を示します。コマンド111は、内部リファレンスの設定用に予約されています(表8を参照)。表17には、内部リファレンスの設定コマンド実行時の、入力シフト・レジスタの内容を示します。

#### 表16. リファレンス設定レジスタ

| 内部リファレンス<br>設定レジスタ(DB0) | 動作                   |

|-------------------------|----------------------|

| 0                       | リファレンスをオフ(デフォ<br>ルト) |

| 1                       | リファレンスをオン            |

#### 表17. リファレンス設定機能用の32ビット入力シフト・レジスタの内容

| DB23~DB22 (MSB) | DB21             | DB20 | DB19 | DB18  | DB17    | DB16 | DB15~DB1   | DB0 (LSB)        |

|-----------------|------------------|------|------|-------|---------|------|------------|------------------|

| X               | 1                | 1    | 1    | x     | x       | x    | X          | 1/0              |

| ドント・ケア          | コマンド・ビット (C2~C0) |      |      | アドレス・ | ビット (A2 | ~A0) | ドント・<br>ケア | リファレンス設定<br>レジスタ |

— 24 — REV. A

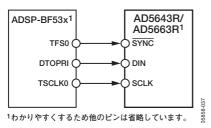

### マイクロプロセッサとのインターフェース AD5623R/AD5643R/AD5663RとBlackfin® ADSP BF53xのインターフェース

図56は、AD5623R/AD5643R/AD5663RとBlackfin ADSP-BF53xマイクロプロセッサのシリアル・インターフェースを示します。ADSP-BF53xプロセッサ・ファミリーには、シリアル通信とマルチプロセッサ通信用に2つのデュアル・チャンネル同期シリアル・ポート(SPORT1とSPORT0)が内蔵されています。SPORT0を用いたAD5623R/AD5643R/AD5663Rとの接続では、次のようにインターフェースをセットアップします。DT0PRIがAD5623R/AD5643R/AD5663RのDINピンを駆動します。

TSCLK0がAD5623R/AD5643R/AD5663RのSCLKを駆動します。

SYNCピンがTFS0から駆動されます。

図56. AD5623R/AD5643R/AD5663RとBlackfin ADSP-BF53xのインターフェース

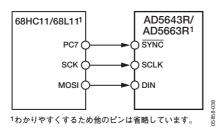

#### AD5623R/AD5643R/AD5663Rと68HC11/68L11の インターフェース

図57は、AD5623R/AD5643R/AD5663Rと68HC11/68L11マイクロコントローラのシリアル・インターフェースを示します。68HC11/68L11のSCKがAD5623R/AD5643R/AD5663RのSCLKを駆動し、MOSI出力はDACのシリアル・データ・ラインを駆動します。

図57. AD5623R/AD5643R/AD5663Rと68HC11/68L11 のインターフェース

SYNC信号はポート・ライン (PC7) から取ります。このインターフェースを正しく動作させるには、次のセットアップ条件に従います。

68HC11/68L11のCPOLビットを0に設定します。 68HC11/68L11のCPHAビットを1に設定します。

データがDACに送信されているとき、SYNCラインをローレベルにします(PC7)。68HC11/68L11が前述のように設定されていれば、MOSI出力に現われるデータは、SCKの立下がりエッジで有効になります。68HC11/68L11からのシリアル・データは8ビットのバイトで転送され、送信サイクル内の立下がりクロック・エッジは8個しかありません。

データはMSBファーストで送信されます。AD5623R/AD5643R/AD5663Rにデータをロードするには、最初の8ビットの転送後もPC7をローレベルのままにして、DACに2番目のシリアル書込み動作を行います。この手順の終わりに、PC7をハイレベルにします。

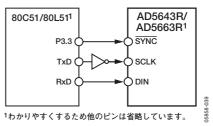

#### AD5623R/AD5643R/AD5663Rと80C51/80L51の インターフェース

図58は、AD5623R/AD5643R/AD5663Rと80C51/80L51マイクロコントローラのシリアル・インターフェースを示します。インターフェースのセットアップは、次のとおりです。

80C51/80L51のTxDがAD5623R/AD5643R/AD5663RのSCLKを駆動します。

RxDがAD5623R/AD5643R/AD5663Rのシリアル・データ・ラインを駆動します。

**SYNC**信号は、ポート上のビット・プログラマブル・ピンから取ります。この場合、ボート・ラインP3.3を使用します。データがAD5623R/AD5643R/AD5663Rに送信されるときには、P3.3をローレベルにします。80C51/80L51は8ビットのバイトのみでデータを送信するため、送信サイクルでは8個の立下がりクロック・エッジだけが発生します。データをDACにデータをロードするには、最初の8ビットの転送後もP3.3をローレベルのままにして、2番目の書込みサイクルを実行すると、データの2番目のバイトが転送されます。このサイクルの完了後にP3.3をハイレベルにします。

80C51/80L51は、LSBファーストのフォーマットでシリアル・データを出力します。AD5623R/AD5643R/AD5663Rは、MSBファーストでデータを受信する必要があります。80C51/80L51の送信ルーチンでは、この点を考慮に入れてください。

図58. AD5623R/AD5643R/AD5663Rと80C51/80L51の インターフェース

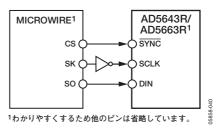

#### AD5623R/AD5643R/AD5663RとMICROWIREの インターフェース

図59は、AD5623R/AD5643R/AD5663RとMICROWIRE互換 デバイスのインターフェースを示します。シリアル・データは、 シリアル・クロックの立下がりエッジでシフト・アウトされ、 SKの立上がりエッジでAD5623R/AD5643R/AD5663Rにクロック入力されます。

図59. AD5623R/AD5643R/AD5663RとMICROWIREの インターフェース

REV. A — 25 —

# アプリケーション情報

#### リファレンスを電源として使用する方法

AD5623R/AD5643R/AD5663Rに必要な電源電流は非常に低いため、電圧リファレンスを使用してAD5623R/AD5643R/AD5663Rに必要な電圧を供給することができます(図60を参照)。電源ノイズが非常に大きい場合、あるいはシステムの電源電圧が5Vまたは3V以外の電圧値(たとえば15V)である場合は、この方法が特に便利です。電圧リファレンスは、AD5623R/AD5643R/AD5663Rに対して定常の電源電圧を出力します。低ドロップアウト電圧のREF195を使用する場合は、DACの出力に負荷を接続していない状態でAD5623R/AD5643R/AD5663Rに500 $\mu$ Aの電流を供給する必要があります。DAC出力に負荷がある場合も、REF195が負荷に電流を供給する必要があります。必要な電流の合計値(DAC出力に5k $\Omega$ の負荷を接続している場合)は、以下のようになります。

$$500\mu A + (5V/5k\Omega) = 1.25mA$$

通常、REF195の負荷レギュレーションは2ppm/mAであるため、REF195から1.25mAの電流を供給すると3ppm( $15\mu V$ )の誤差が生じます。これは、0.196LSBの誤差に相当します。

図60. AD5623R/AD5643R/AD5663Rの電源としてREF195 を使用する回路

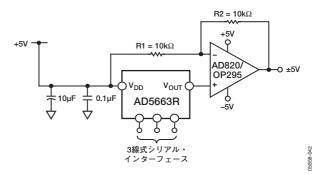

### AD5663Rを使用するバイポーラ動作

AD5663Rは単電源の動作に設計されていますが、図61の回路を使用して、バイポーラ出力電圧範囲にすることも可能です。この回路では、出力電圧範囲が $\pm 5$ Vとなります。出力アンプにAD820またはOP295を使用すると、アンプ出力のレールtoレール動作が可能になります。

任意の入力コードに対応する出力電圧は、以下の式で計算できます。

$$V_{O} = \left[V_{DD} \times \left(\frac{D}{65,536}\right) \times \left(\frac{RI + R2}{RI}\right) - V_{DD} \times \left(\frac{R2}{RI}\right)\right]$$

ここで、Dは10進数値( $0\sim65,535$ )で表した入力コードです。  $V_{DD}=5$ V、RI=R2=10k $\Omega$ のときは、以下のようになります。

$$V_o = \left(\frac{10 \times D}{65.536}\right) - 5V$$

出力電圧範囲は $\pm 5$ Vとなり、0x00000が-5V出力、0xFFFFが+5V出力に相当します。

図61. AD5663Rを使用したバイポーラ動作

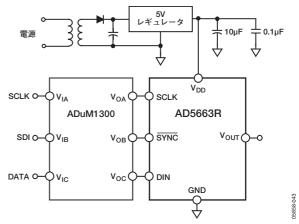

### 絶縁インターフェースでAD5663Rを使用する 方法

工業環境のプロセス制御アプリケーションでは、DACが動作している環境で発生する危険な同相電圧から制御回路を保護したり絶縁するために、絶縁インターフェースが必要になることがあります。 $2.5 \mathrm{kV}$ を超える絶縁には、 $i\mathrm{Couplet}^{\mathrm{eo}}$ を使用できます。AD5663Rは3線式シリアル・ロジック・インターフェースを使用しているため、3 チャンネルのデジタル・アイソレータADuM1300によって必要な絶縁が得られます(図62を参照)。AD5663Rの電源も絶縁する必要がありますが、これにはトランスを使用します。トランスのDAC側では、 $5\mathrm{V}$ レギュレータがAD5663Rに必要な $5\mathrm{V}$ 電源を供給します。

図62. 絶縁インターフェースを備えたAD5663R

— 26 — REV. A

### 電源のバイパスとグラウンディング

精度が重視される回路では、ボード上の電源とグラウンド・リターンのレイアウトに注意してください。AD5663Rを実装するプリント回路ボードは、アナログ部とデジタル部を分離し、ボード内でそれぞれをまとめて配置するように設計してください。

複数のデバイスがAGNDとDGND間の接続を必要とするシステムでAD5663Rを使用する場合は、必ず1ヵ所のみでこの接続を行ってください。グラウンド・ポイントはAD5663Rのできるかぎり近くに配置してください。

AD5663Rの電源は、 $10\mu$ Fと $0.1\mu$ Fのコンデンサを使用してバイパスします。コンデンサはデバイスのできるだけ近くに配置し、 $0.1\mu$ Fのコンデンサは理想的にはデバイスの真上に配置してください。 $10\mu$ Fのコンデンサはタンタルのビード型を使います。 $0.1\mu$ Fのコンデンサは、一般的なセラミック型のように等価直列抵抗(ESR)が小さく、かつ等価直列インダクタンス(ESI)が小さいものを使うことが重要です。

この0.1μFのコンデンサは、内部ロジックのスイッチングによる過渡電流によって発生する高周波に対して、グラウンドへの低インピーダンス・パスを提供します。

電源ラインはできるだけ太いパターンにしてインピーダンスを小さくし、電源ライン上のグリッチによる影響を低減させます。クロックとその他の高速スイッチング・デジタル信号は、デジタル・グラウンドを用いてボード上の他の部分からシールドします。デジタル信号とアナログ信号は、できるだけ交差しないようにしてください。ボードの反対側のパターンは、互いに直角になるように配置し、ボードを通過するフィードスルーの影響を削減します。最適なボード・レイアウト技術は、ボードの部品側をグラウンド・プレーン専用として使い、信号パターンをハンダ面に配置するマイクロストリップ技術ですが、2層ボードでは必ずしも使用できるとは限りません。

REV. A — 27 —

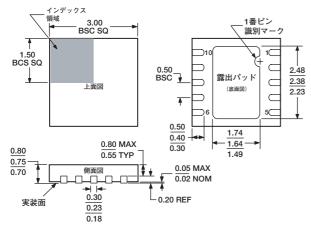

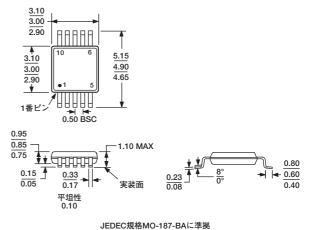

# 外形寸法

図63. 10ピン・リード・フレーム・チップ・スケール・ パッケージ [LFCSP\_WD] 3mm×3mmボディ、極薄型、デュアル・リード (CP-10-9) 寸法単位:mm

図64. 10ピン・ミニ・スモール・アウトライン・パッケージ [MSOP] (RM-10) 寸法単位:mm

### オーダー・ガイド

|                                 |            |            | 内部     |              | パッケージ・  |       |

|---------------------------------|------------|------------|--------|--------------|---------|-------|

| モデル                             | 温度範囲       | 精度         | リファレンス | パッケージ        | オプション   | マーキング |

| AD5623RBCPZ-3R2 <sup>1</sup>    | -40~+105°C | ±1LSB INL  | 1.25V  | 10ピンLFCSP_WD | CP-10-9 | D85   |

| AD5623RBCPZ-3REEL7 <sup>1</sup> | -40~+105°C | ±1LSB INL  | 1.25V  | 10ピンLFCSP_WD | CP-10-9 | D85   |

| AD5623RBRMZ-31                  | -40~+105℃  | ±1LSB INL  | 1.25V  | 10ピンMSOP     | RM-10   | D85   |

| AD5623RBRMZ-3REEL7 <sup>1</sup> | -40~+105℃  | ±1LSB INL  | 1.25V  | 10ピンMSOP     | RM-10   | D85   |

| AD5623RBRMZ-5 <sup>1</sup>      | -40~+105℃  | ±1LSB INL  | 2.5V   | 10ピンMSOP     | RM-10   | D86   |

| AD5623RBRMZ-5REEL7 <sup>1</sup> | -40~+105℃  | ±1LSB INL  | 2.5V   | 10ピンMSOP     | RM-10   | D86   |

| AD5643RBRMZ-3 <sup>1</sup>      | -40~+105℃  | ±4LSB INL  | 1.25V  | 10ピンMSOP     | RM-10   | D81   |

| AD5643RBRMZ-3REEL7 <sup>1</sup> | -40~+105℃  | ±4LSB INL  | 1.25V  | 10ピンMSOP     | RM-10   | D81   |

| AD5643RBRMZ-51                  | -40~+105℃  | ±4LSB INL  | 2.5V   | 10ピンMSOP     | RM-10   | D7Q   |

| AD5643RBRMZ-5REEL7 <sup>1</sup> | -40~+105℃  | ±4LSB INL  | 2.5V   | 10ピンMSOP     | RM-10   | D7Q   |

| AD5663RBCPZ-3R2 <sup>1</sup>    | -40~+105°C | ±16LSB INL | 1.25V  | 10ピンLFCSP_WD | CP-10-9 | D7S   |

| AD5663RBCPZ-3REEL7 <sup>1</sup> | -40~+105℃  | ±16LSB INL | 1.25V  | 10ピンLFCSP_WD | CP-10-9 | D7S   |

| AD5663RBRMZ-3 <sup>1</sup>      | -40~+105℃  | ±16LSB INL | 1.25V  | 10ピンMSOP     | RM-10   | D7S   |

| AD5663RBRMZ-3REEL7 <sup>1</sup> | -40~+105℃  | ±16LSB INL | 1.25V  | 10ピンMSOP     | RM-10   | D7S   |

| AD5663RBRMZ-51                  | -40~+105°C | ±16LSB INL | 2.5V   | 10ピンMSOP     | RM-10   | D7H   |

| AD5663RBRMZ-5REEL7 <sup>1</sup> | -40~+105°C | ±16LSB INL | 2.5V   | 10ピンMSOP     | RM-10   | D7H   |

| EVAL-AD5663REB                  |            |            |        | 評価用ボード       |         |       |

<sup>1</sup> Z=鉛フリー製品