# 4.5A、500kHz降圧 スイッチング・レギュレータ

# 特長

■ 500kHz固定スイッチング周波数

■ 同期が容易

■ すべて表面実装型部品を使用可能

■ 最小1.8µHのインダクタ・サイズ

■ 飽和スイッチ設計:0.07 ■ 実効電源電流:2.5mA ■ シャットダウン電流:20μA ■ サイクル単位の電流制限

# アプリケーション

■ ポータブル・コンピュータ

■ バッテリ電源機器

■ バッテリ・チャージャ

■ 分配電源

### 概要

LT®1374は、500kHzのモノリシック降圧スイッチング・レギュレータです。4.5Aのスイッチがレギュレータに必要なすべての発振器、制御、およびロジック回路とともにチップに内蔵されています。スイッチング周波数が高いため、外部部品サイズをかなり小さくできます。高速過渡応答および優れたループ安定性を実現するため、電流モードのトポロジーを採用しています。固定電圧出力と可変出力があります。

特別な高速バイポーラ・プロセスと新しい設計技術を駆使し、高いスイッチング周波数でも高効率を達成しています。出力を使用して回路をバイアスしたり、電源ブースト・コンデンサを用いてパワー・スイッチを飽和させることにより、広い出力電流範囲で高い効率が維持されます。

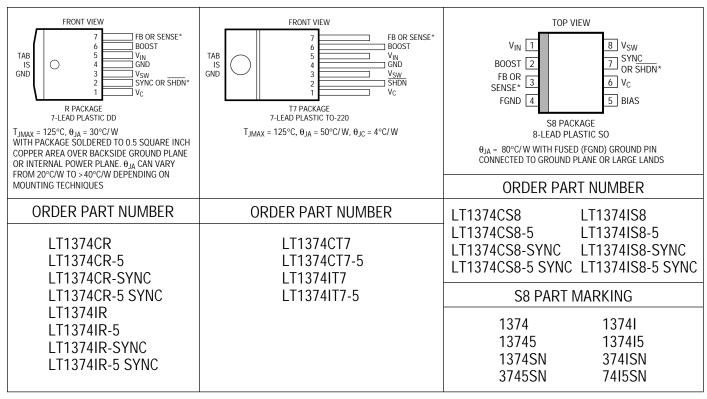

LT1374は標準7ピンDD、TO-220、およびヒューズド・リードSO-8パッケージに収容されています。完全なサイクル単位の短絡保護、およびサーマル・シャットダウン機能を備えています。インダクタやコンデンサなど外付け部品は、標準表面実装型のものが使用できます。シャットダウンまたは同期のオプション機能があります。シャットダウン時には消費電流が20μAに減少します。同期機能を使用して、外部ロジック・レベル信号により内部発振器を580kHzから1MHzに高めることができます。

**▲ブ**、LTC、LTはリニアテクノロジー社の登録商標です。

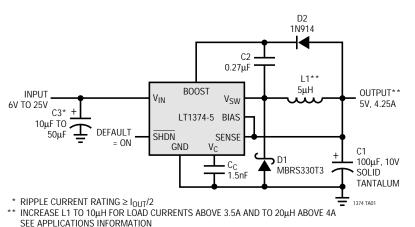

# 標準的応用例

### 5\バック(降圧)コンバータ

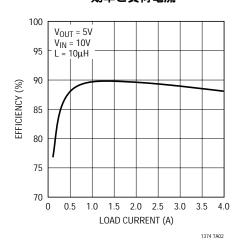

#### 効率と負荷電流

**T**LINEAR

# 絶対最大定格

| 入力電圧                | 25V  |

|---------------------|------|

| BOOSTピン電圧( 入力電圧基準 ) | 15V  |

| SHDNピン電圧            | 7V   |

| BIASピン電圧            | 7V   |

| FBピン電圧( 可変出力 )      | 3.5V |

| FBピン電流( 可変出力 )      | 1mA  |

| センス電圧( 5V固定デバイス )   | 7V   |

|                     |      |

| SYNCピン電圧          | 7V    |

|-------------------|-------|

| 動作接合部温度範囲         |       |

| LT1374C0          | ~ 125 |

| LT1374I 40        | ~ 125 |

| 保存温度範囲 65         | ~ 150 |

| リード温度( 半田付け、10秒 ) | 300   |

# パッケージ/発注情報

<sup>\*</sup> デフォルトは、FBピンおよびシャットダウン機能付き可変出力電圧デバイスです。5V固定出力アプリケーション用のオプション-5はFBがSENSEピンに置き換わ ります。同期が必要なアプリケーション用の-SYNCはSHDNがSYNCピンに置き換わります。ミリタリ・グレードに関してはお問い合わせください。

# 電気的特性

注記がない限り、 $T_J = 25$  、 $V_{IN} = 15V$ 、 $V_C = 1.5V$ 、プースト  $= V_{IN} + 5V$ 、スイッチ・オープン

| PARAMETER                         | CONDITIONS              |   | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------|-------------------------|---|------|------|------|-------|

| Feedback Voltage (Adjustable)     |                         |   | 2.39 | 2.42 | 2.45 | V     |

|                                   | All Conditions          | • | 2.36 |      | 2.48 | V     |

| Sense Voltage (Fixed 5V)          |                         |   | 4.94 | 5.0  | 5.06 | V     |

|                                   | All Conditions          | • | 4.90 |      | 5.10 | V     |

| SENSE Pin Resistance              |                         |   | 7    | 10   | 14   | kΩ    |

| Reference Voltage Line Regulation | $5V \le V_{IN} \le 25V$ |   |      | 0.01 | 0.03 | %/V   |

# 電気的特性

注記がない限り、T<sub>J</sub>=25 、V<sub>IN</sub>=15V、V<sub>C</sub>=1.5V、プースト=V<sub>IN</sub>+5V、スイッチ・オープン

| PARAMETER                                             | CONDITIONS                                                                                                    |   | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---|------|------|------|-------|

| Feedback Input Bias Current                           |                                                                                                               | • |      | 0.5  | 2    | μА    |

| Error Amplifier Voltage Gain                          | (Notes 1, 7)                                                                                                  |   | 200  | 400  |      |       |

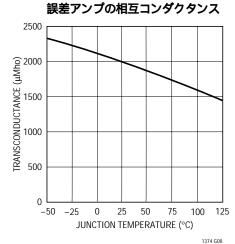

| Error Amplifier Transconductance                      | $\Delta I (V_C) = \pm 10 \mu A \text{ (Note 7)}$                                                              |   | 1500 | 2000 | 2700 | μMho  |

|                                                       |                                                                                                               | • | 1000 |      | 3100 | μMho  |

| V <sub>C</sub> Pin to Switch Current Transconductance |                                                                                                               |   |      | 5.3  |      | A/V   |

| Error Amplifier Source Current                        | $V_{FB} = 2.1V$ or $V_{SENSE} = 4.4V$                                                                         | • | 140  | 225  | 320  | μΑ    |

| Error Amplifier Sink Current                          | $V_{FB} = 2.7V$ or $V_{SENSE} = 5.6V$                                                                         | • | 140  | 225  | 320  | μА    |

| V <sub>C</sub> Pin Switching Threshold                | Duty Cycle = 0                                                                                                |   |      | 0.9  |      | V     |

| V <sub>C</sub> Pin High Clamp                         |                                                                                                               |   |      | 2.1  |      | V     |

| Switch Current Limit                                  | $V_C$ Open, $V_{FB}$ = 2.1V or $V_{SENSE}$ = 4.4V, DC $\leq$ 50%                                              | • | 4.5  | 6    | 8.5  | A     |

| Slope Compensation (Note 8)                           | DC = 80%                                                                                                      |   |      | 0.8  |      | А     |

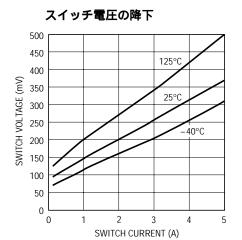

| Switch On Resistance (Note 6)                         | I <sub>SW</sub> = 4.5A                                                                                        |   |      | 0.07 | 0.1  | Ω     |

|                                                       |                                                                                                               | • |      |      | 0.13 | Ω     |

| Maximum Switch Duty Cycle                             | $V_{FB} = 2.1V$ or $V_{SENSE} = 4.4V$                                                                         |   | 90   | 93   |      | %     |

|                                                       |                                                                                                               | • | 86   | 93   |      | %     |

| Switch Frequency                                      | V <sub>C</sub> Set to Give 50% Duty Cycle                                                                     |   | 460  | 500  | 540  | kHz   |

|                                                       |                                                                                                               | • | 440  |      | 560  | kHz   |

| Switch Frequency Line Regulation                      | 5V ≤ V <sub>IN</sub> ≤ 25V                                                                                    | • |      | 0    | 0.15 | %/V   |

| Frequency Shifting Threshold on FB Pin                | $\Delta f = 10kHz$                                                                                            | • | 0.8  | 1.0  | 1.3  | V     |

| Minimum Input Voltage (Note 2)                        |                                                                                                               | • |      | 5.0  | 5.5  | V     |

| Minimum Boost Voltage (Note 3)                        | I <sub>SW</sub> ≤ 4.5A                                                                                        | • |      | 2.3  | 3.0  | V     |

| Boost Current (Note 4)                                | I <sub>SW</sub> = 1A                                                                                          | • |      | 20   | 35   | mA    |

|                                                       | I <sub>SW</sub> = 4.5A                                                                                        | • |      | 90   | 140  | mA    |

| V <sub>IN</sub> Supply Current (Note 5)               | V <sub>BIAS</sub> = 5V                                                                                        | • |      | 0.9  | 1.4  | mA    |

| BIAS Supply Current (Note 5)                          | V <sub>BIAS</sub> = 5V                                                                                        | • |      | 3.2  | 4.0  | mA    |

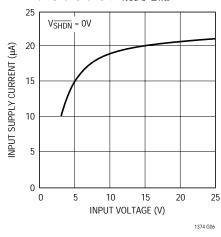

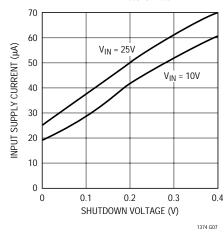

| Shutdown Supply Current                               | $V_{\overline{SHDN}} = 0V$ , $V_{\overline{IN}} \le 25V$ , $V_{\overline{SW}} = 0V$ , $V_{\overline{C}}$ Open |   |      | 20   | 50   | μA    |

|                                                       |                                                                                                               | • |      |      | 75   | μA    |

| Lockout Threshold                                     | V <sub>C</sub> Open                                                                                           | • | 2.3  | 2.38 | 2.46 | V     |

| Shutdown Thresholds                                   | V <sub>C</sub> Open Device Shutting Down                                                                      | • | 0.13 | 0.37 | 0.60 | V     |

| Construction Through and                              | Device Starting Up                                                                                            |   | 0.25 | 0.45 | 0.7  | V     |

| Synchronization Threshold                             |                                                                                                               | • | F00  | 1.5  | 2.2  |       |

| Synchronizing Range                                   |                                                                                                               |   | 580  | 40   | 1000 | kHz   |

| SYNC Pin Input Resistance                             |                                                                                                               |   |      | 40   |      | kΩ    |

### ● は全動作温度範囲の規格値を意味する。

Note 1:利得は、スイッチング・スレッショルド・レベルより200mV上から、 上側クランプ・レベルより200mV下までのV<sub>C</sub>振幅で測定される。

Note 2:最小入力電圧は直接測定されていないが、他のテストで保証されている。最小入力電圧は、リファレンス電圧と発振器周波数が一定のまま維持され るよう、内部パイアス・ラインが安定化されている場合の電圧として定義されている。安定化出力を維持するための実際の最小入力電圧は、出力電圧と負荷

電流に依存する。アプリケーション情報を参照。

Note 3: これは、内部パワー・スイッチの完全な飽和を保証するために必要なプースト・コンデンサ両端の最小電圧である。

Note 4: ブースト電流は、ブースト・ピンを入力電圧より5V高く保持したときピンに流入する電流である。ブースト電流はスイッチ・オン時間中しか流れな

Note  $5: V_{\text{IN}}$ 電源電流は、BIASピンが5Vに保持され、スイッチングがディスエーブルされているときに流れる電流である。BIASピンが無効かまたはオープ ンの場合は、V<sub>IN</sub>およびBIAS電源電流の合計がV<sub>IN</sub>ピンに流れる。

Note 6: スイッチ・オン抵抗は、 $V_{\rm IN}$  -  $V_{\rm SW}$ 電圧を与えた電流 (4.5A)で除算して計算される。他の電流でのスイッチ電圧のグラフについては、標準的性能特性

Note 7: トランスコンダクタンスと電圧利得は、電圧分割器を除く内部アンプ Note 7:アプスコンテグタスと電圧が得は、電圧が制器を除く内部アプラ に関係する。固定電圧デバイスに関して、利得とトランスコンダクタンスを計 算するには、SENSEピンを参照する。除算値はV<sub>OUT</sub>/2.42の比率による。 Note 8:スロープ補償はデューティ・サイクル80%のときのスイッチ制限電流 から減算された電流。詳細については、アプリケーション情報の最大出力負荷

電流を参照。

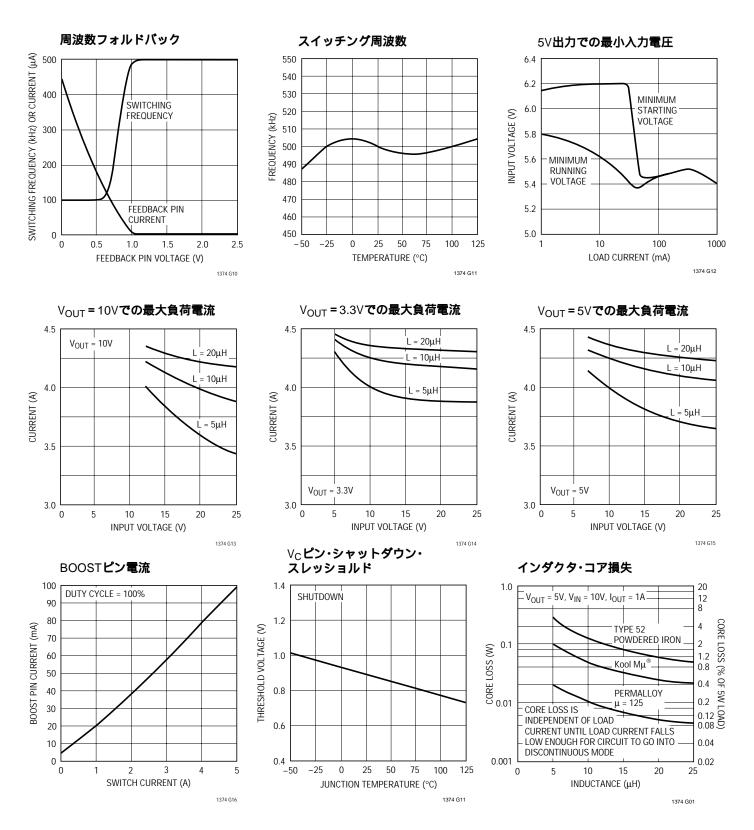

# 標準的性能特性

6.5 SWIICH BEAK CURRENT (A) 2.5 SWIICH PEAK CURRENT (A) 3.5 SWIICH PEAK CURRENT (A) 3.5 SWIICH PEAK CURRENT (B) 3.5 SWIICH (B) 3.5

スイッチ・ピーク電流制限

シャットダウン・ピン・パイアス 電流

DUTY CYCLE (%)

40

60

80

1374 G02

3.0

0

20

シャットダウン消費電流

シャットダウン消費電流

# 標準的性能特性

Kool  $\mbox{M}\mu$  is a registered trademark of Magnetics, Inc.

# ピン機能

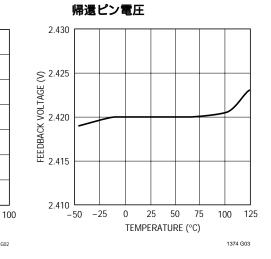

FB/SENSE: この帰還ピンは、内部2.42Vソースを基準とする誤差アンプの入力です。出力電圧は外付け抵抗分割器を使用して設定します。固定電圧デバイス(-5)は分割器をチップに内蔵しているため、FBピンをSENSEピンとして使用し5V出力に直接接続します。FBピンにはそのほかに3つの機能があります。ピンの電圧が1.7V以下に低下すると、スイッチ電流制限が低下します。1.5V以下になると、外部同期機能がディスエーブルされます。1V以下になると、スイッチング周波数も低下します。詳細については、アプリケーション情報の帰還ピンの機能のセクションを参照してください。

BOOST: BOOSTピンを使用して、入力電圧より高いドライブ電圧を内部バイポーラNPNパワー・スイッチに供給します。この電圧が追加されない場合は、標準スイッチ電圧損失は約1.5Vとなります。追加ブースト電圧により、スイッチが飽和でき、電圧損失はFET構造上の損失0.07 に接近します。効率は従来のバイポーラ設計では75%であったのに対し、これら新しいデバイスでは89%以上に向上します。

V<sub>IN</sub>: これは内蔵パワーNPNスイッチのコレクタです。このピンはBIASピンからのバイアスがないときに、内部回路と内部レギュレータに電源を供給します。NPNスイッチがオン、オフすると、このピンに高いdl/dtエッジが発生します。外付けのバイパスとキャッチ・ダイオードをこのピンの近くに接続してください。このパスのすべてのトレース・インダクタンスは、スイッチ・オフで電圧スパイクを生成し、内部NPN両端のV<sub>CE</sub>電圧を上昇させます。

GND: GNDピンの接続は、2つの理由から塾考する必要があります。まず、GNDピンは安定化出力の基準であるため、負荷の「グランド」エンドがICのGNDピンと同じ電圧でない場合はロード・レギュレーションに問題が生じます。この状態は、GNDピンと負荷グランド点の間の金属パスを負荷電流またはそのほかの電流が流れるときに発生します。GNDピンと負荷の間のグランド・パスを短くし、可能であればグランド・プレーンを使用します。もう1つの考慮事項は、GNDピン電流スパイクにより生じるEMIです。V<sub>SW</sub>ピンとGNDピン間の内部ではいり生じるEMIです。V<sub>SW</sub>ピンとGNDピン間の内部流スパイクが発生します。GNDピンが長い金属トレースでシステム・グランドに接続されている場合は、このトレースが過度なEMIを放射することがあります。入力バイパスとGNDピンの間のパスを短くしてください。

V<sub>SW</sub>: このスイッチ・ピンは、内蔵パワーNPNスイッチのエミッタです。スイッチ・オン時間に、入力ピン電圧までドライブされます。スイッチ・オフ時間には、インダクタ電流がスイッチ・ピンを負にドライブします。負電圧は外部キャッチ・ダイオードによってクランプされます。許容される最大スイッチ負電圧は - 0.8Vです。

SYNC:(RおよびSO-8パッケージのみ)。SYNCピンは内部発振器を外部信号に同期させるのに使用します。このピンはロジックレベル・コンパチブルで、デューティ・サイクルが10%から90%の信号でドライブできます。同期範囲は初期動作周波数から最大1MHzまでです。このピンは、-SYNCオプションのデバイスではSHDNから置き換えられています。詳細については、アプリケーション情報の同期のセクションを参照してください。

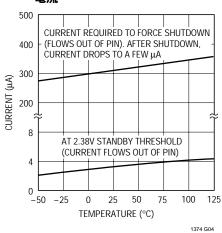

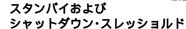

SHDN:シャットダウン・ピンは、レギュレータをターンオフして、入力ドレイン電流を数μAまで低減するのに使用します。実際には、このピンには2つの別々のスレッショルドがあり、1つはスイッチングを停止させるための2.38Vのスレッショルド、もう1つは完全なマイクロパワー・シャットダウンを実行するための0.4Vのスレッショルドです。2.38Vスレッショルドは、高精度の低電圧ロックアウト(UVLO)として機能します。低電圧ロックアウトは、入力電圧があらかじめ決められたレベルに達するまで、レギュレータを動作させない目的に使用することができます。

V<sub>C</sub>: V<sub>C</sub>ピンは誤差アンプの出力であり、ピーク・スイッチ電流コンパレータの入力でもあります。このピンは通常周波数補償に使用されますが、電流クランプや制御ループのオーバライドなど、2つの機能を実行することができます。このピンは非常に軽い負荷では約1Vに留まりますが、最大負荷時には2Vになります。グランド電位にすれば、レギュレータを停止できますが、"H"にドライブした場合は電流を4mAに制限しなければなりません。

BIAS:(SOパッケージのみ)。このBIASピンを使用して、高入力電圧および軽負荷電流での動作時の効率を改善します。このピンを安定化出力電圧に接続すると、大部分の内部回路が入力電源ではなく、出力電圧から動作電流を引き出します。これは入力電圧が出力電圧よりはるかに高い場合は、非常に効率の高い方法です。この動作モードの最小出力電圧値は3.3Vです。V<sub>IN</sub> = 20V、V<sub>OUT</sub> = 5V、およびI<sub>OUT</sub> = 25mAでは、効率が10%以上向上します。

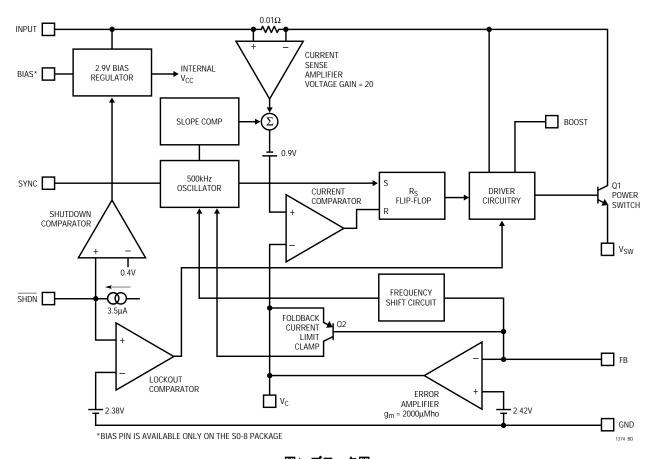

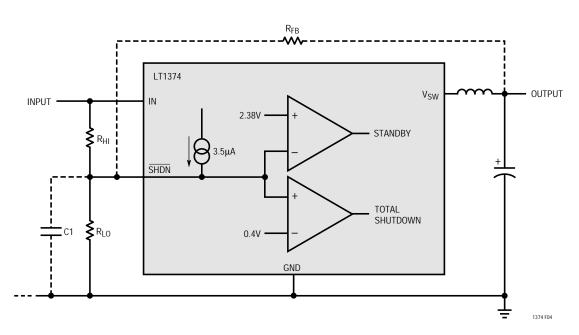

# ブロック図

LT1374は定周波数、電流モード・バック(降圧)コンバー タです。つまり、パワー・スイッチのデューティ・サイクル を制御するための内部クロックと2つの帰還ループがあ ります。通常の誤差アンプのほかに、サイクル単位でス イッチ電流をモニタする電流センス・アンプがあります。 スイッチ・サイクルは、発振器パルスがRsフリップ・フ ロップをセットすると、スイッチがターンオンして開始 します。スイッチ電流がコンパレータの反転入力で設定 されるレベルに達すると、フリップ・フロップがリセット され、スイッチがターンオフします。出力電圧は誤差アン プの出力を使用して、スイッチの電流トリップ点を設定 することにより制御されます。この手法では誤差アンプ は、電圧ではなく出力に供給すべき電流を指示します。電 圧帰還システムでは、インダクタと出力コンデンサの共 振周波数までは位相シフトは小さく、共振周波数を超え ると急激に180 ℃位相シフトが発生します。電流帰還シ ステムでは、共振周波数よりかなり低い周波数でも90 ℃ 位相シフトがありますが、LC共振周波数よりはるかに高 い周波数まで、位相シフトがさらに90 追加されることは ありません。このため、帰還ループの周波数補償がはるか に簡単になり、過渡応答を迅速に行うことができます。

LT1374の大部分の回路は内部の2.9Vバイアス・ラインで動作します。バイアス・レギュレータには通常、レギュレータ入力ピンから電力が供給されますが、BIASピンを3V以上の外部電圧に接続した場合は、バイアス電力は外部ソース(通常は、安定化出力電圧)から供給されます。これによってBIASピン電圧がレギュレータ入力電圧より低い場合に効率が向上します。

BOOSTピンを使用して、スイッチ・ドライバに入力電圧より高い電圧を供給すると、高いスイッチ効率が達成され、スイッチを飽和させることができます。このブースト電圧は、外部コンデンサとダイオードで生成されます。2つのコンパレータがシャットダウン・ピンに接続されています。1つは低電圧ロックアウト用の2.38Vスレッショルドを持ち、もう1つは完全なシャットダウン用の0.4Vスレッショルドを持っています。

図1. ブロック図

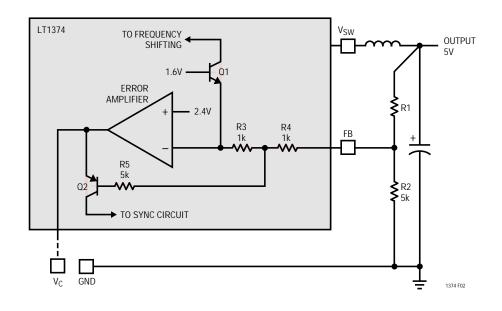

### 帰還ピンの機能

LT1374の帰還(FB)ピンは出力電圧の設定と、いくつかの過負荷保護機能に使用します。このセクションの最初の部分では出力電圧を設定するための抵抗選択について説明し、次にフォルドバック周波数およびFBピンによる電流制限について説明します。最終設計に入る前に両方の説明を読んでください。5V固定出力のLT1374-5は分圧抵抗を内蔵し、FBピンはSENSEという名前が付けられ、出力に直接接続されています。

FBからグランドへの出力分割抵抗(R2)の推奨値(図2参照)は5k 以下で、R1を求める式を以下に示します。FBピンの入力バイアス電流によって生じる出力電圧誤差は、R2 = 5k の場合には0.25%以下です。表1に代表的な出力電圧に対する1%精度の抵抗値が記載してあります。これらの推奨値より分割器抵抗値が大きくなる場合は以下の説明を読んでください。

$$R1 = \frac{R2(V_{OUT} - 2.42)}{2.42}$$

表1.

| OUTPUT<br>VOLTAGE<br>(V) | R2<br>(kΩ) | R1<br>(NEAREST 1%)<br>(kΩ) | % ERROR AT OUTPUT<br>DUE TO DISCREET 1%<br>RESISTOR STEPS |

|--------------------------|------------|----------------------------|-----------------------------------------------------------|

| 3                        | 4.99       | 1.21                       | +0.23                                                     |

| 3.3                      | 4.99       | 1.82                       | + 0.08                                                    |

| 5                        | 4.99       | 5.36                       | +0.39                                                     |

| 6                        | 4.99       | 7.32                       | -0.5                                                      |

| 8                        | 4.99       | 11.5                       | -0.04                                                     |

| 10                       | 4.99       | 15.8                       | +0.83                                                     |

| 12                       | 4.99       | 19.6                       | -0.62                                                     |

| 15                       | 4.99       | 26.1                       | + 0.52                                                    |

### 電圧帰還以外の機能

帰還ピンは出力電圧の検出以外にも使用できます。すなわち出力電圧が非常に低い場合に、スイッチング周波数や電流制限を低減します(標準的性能特性のフォルドバック・グラフを参照)。これにより短絡状態では、ICと外部ダイオード、およびインダクタの電力消費を抑えます。出力が短絡するとスイッチング・レギュレータは非常に低いデューティ・サイクルで動作する必要があり、ダイオードとインダクタを流れる平均電流は、スイッチの短絡制限電流(3A以下でフォルドバックするときには、LT1374では標準6A)と等しくなります。スイッ

図2. 周波数および電流制限フォールド・バック

チング周波数が500kHzに維持されていれば、最小スイッチ・オン時間の制限によってスイッチャのデューティ・サイクルが低くなりすぎることはありません。したがって、周波数は帰還ピンの電圧が1V以下に低下すると約1/5減少します(周波数フォルドバック・グラフ参照)。これは通常の負荷条件での動作には影響を与えません。出力電圧が上昇すると、起動時のスイッチング周波数にギア・シフトが観察されるだけです。

LT1374はスイッチング周波数を低下することに加え て、帰還ピンの電圧が1.7V以下に低下すると、より低い スイッチ電流制限で動作します。図2のQ2はVcピンを、 標準2.1Vの上位クランプ・レベル以下の電圧にクランプ して、この機能を実行します。このフォルドバック電流 制限機能は、短絡状態でのIC、ダイオード、およびイン ダクタの消費電力を大幅に低減します。フォルドバック 動作を妨害しないように、外部同期もディスエーブルさ れます。前述したように、通常の負荷条件ではユーザが この存在を意識することはありません。影響を受ける可 能性のある負荷は、出力電圧が最終値の50%以下の状態 で全負荷電流を維持しようとする電流源負荷だけです。 このような希な状況では、外部ダイオードを用いて帰還 ピンを1.5Vより高くクランプして、フォルドバック電流 制限を無効にすることができます。**注意:**帰還ピンをク ランプすると、周波数シフトも無効になるため、高い入 力電圧で出力を完全に短絡すると、LT1374は電流制限 を制御できなくなる可能性があります。

出力電圧が低い場合、スイッチング周波数を低下させる 内部回路によって帰還ピンから電流が流れ出すようにな ります。この等価回路を図2に示します。Q1は通常動作 中は完全にオフになっています。FBピンが1V以下に低 下すると、Q1が電流を流し始め、約5kHz/μAの割合で周 波数を低下させます。適切な周波数フォルドバックを確 保するには 最悪短絡条件で )、外部分割器のテブナン抵 抗は、FBピンを0.6Vにして、FBピンから150μAを引き 出せるだけ低い値でなければなりません(R<sub>DIV</sub>≤4k)。 その結果、周波数および電流制限の低下は、出力電圧分 割器のインピーダンスに影響されます。分割器のイン ピーダンスは非常に厳密ではありませんが、抵抗値が推 奨値より高く、入力電圧が高いときに短絡状態が発生す るときは注意してください。高周波ピックアップが増加 し、周波数および電流フォルドバックによる保護機能が 低下します。

### 最大出力負荷電流

バック・コンバータの最大負荷電流は、LT1374の最大スイッチ電流定格( lp )によって制限されます。この電流定格は50%のデューティ・サイクル( DC )まで4.5Aで、80%のデューティ・サイクルでは3.7Aに減少します。これを標準的性能特性に図示し、以下の式で示します。

I<sub>P</sub> = 4.5A( DC ≤ 50%の場合 ) I<sub>P</sub> = 3.21 + 5.95( DC ) - 6.75( DC ) ( 50% < DC < 90%の場合 )

$DC = デューティ・サイクル = V_{OUT}/V_{IN}$  例: $V_{OUT} = 5V$ 、 $V_{IN} = 8V$ 、したがってDC = 5/8 = 0.625の場合、

$I_{SW(MAX)} = 3.21 + 5.95(0.625) - 6.75(0.625)^2 = 4.3A$

LT1374は、電流モードの低調波スイッチングを防止するためにスロープ補償回路を内蔵しており、デューティ・サイクルに応じて電流定格が低下します。詳細についてはアプリケーション・ノート19を参照してください。LT1374はこの点に関しては多少異なり、非直線スロープ補償を採用しているため、電流制限がわずかに低下するだけで優れた補償を実現できます。

最大負荷電流は、無限に大きなインダクタに対しては最大スイッチ電流と等しくなりますが、有限インダクタ・サイズでは、最大負荷電流はピーク・ツー・ピークのインダクタ電流の1/2に減少します。以下の式では連続モード動作を仮定しており、右の項がIpの1/2以下になります。

$$I_{OUT(MAX)}$$

=

連続モード  $I_P - \frac{\left(V_{OUT}\right)\left(V_{IN} - V_{OUT}\right)}{2\left(L\right)\left(f\right)\left(V_{IN}\right)}$

上記の条件でL = 3.3μHの場合、

$$I_{OUT(MAX)} = 4.3 - \frac{(5)(8-5)}{2(3.3 \cdot 10^{-6})(500 \cdot 10^{3})(8)}$$

$$= 4.3 - 0.57 = 3.73 \text{ A}$$

$V_{IN}$  = 15Vでは、デューティ・サイクルが33%であるため、 $I_P$ は4.5Aで一定であり、 $I_{OUT(MAX)}$ は以下のようになります。

$$4.5 - \frac{(5)(15 - 5)}{2(3.3 \cdot 10^{-6})(500 \cdot 10^{3})(15)}$$

= 4.5 - 1 = 3.5A

入力電圧が高いとインダクタのリップル電流が増加するため、引き出せる負荷電流が少なくなることに注意してください。ただし常にそうであるとは限りません。インダクタ値と入力電圧範囲の特定の組合せでは、デューティ・サイクルが高いとピーク・スイッチ電流が減少するため、最低入力電圧で得られる負荷電流が減少する場合があります。負荷電流が利用可能な最大値に近い場合は、入力電圧範囲の最大値、最小値で利用可能な最大電流を調べてください。ある条件における実際のピーク・スイッチ電流を計算するには、以下の式を使用します。

$$I_{SW\left(PEAK\right)} = I_{OUT} + \frac{V_{OUT} \left(V_{IN} - V_{OUT}\right)}{2\left(L\right)\!\left(f\right)\!\left(V_{IN}\right)}$$

不連続動作が可能な軽負荷の場合、最大負荷電流は以下のようになります。

例:L = 1.2 $\mu$ H、  $V_{OUT}$  = 5V、  $V_{IN(MAX)}$  = 15Vの場合、

$$I_{OUT(MAX)} = \frac{\left(4.5\right)^2 \left(500 \cdot 10^3\right) \left(1.2 \cdot 10^{-6}\right) \left(15\right)}{2 \left(5\right) \left(15 - 5\right)} = 1.82A$$

このような小さなインダクタを使用する主な理由は、物理的に非常に小さいためですが、ピーク・ツー・ピークのインダクタ電流はかなり高くなることを忘れないでください。これは出力リップル電圧を増加させます。リップル電圧を低下させるために出力コンデンサを大きくしなければならない場合は、実際に回路全体が大きくなる可能性があります。

### インダクタと出力コンデンサの選択

ほとんどのアプリケーションでは、出力インダクタは 3μHから20μHの範囲になります。インダクタンス値が低いほど、インダクタの物理的サイズも小さくなります。値が大きいと、LT1374のスイッチ(電流制限値が 4.5A)に現れるピーク電流が低下するため、流せる出力電流が大きくなります。インダクタンスが大きいと、出力リップル電圧も低下し、コア損失が低減されます。標準的性能特性セクションのグラフに、最大出力負荷電流対インダクタ・サイズ、および入力電圧を示します。別のグラフに、各種コア材料におけるコア損失対インダクタ・サイズを示します。

インダクタを選択する際は、最大負荷電流、コア損失および銅損失、許容される部品の高さ、電圧リップル、EMI、インダクタのフォールト電流、飽和、そしていうまでもなくコストを検討しなければなりません。多少複雑で矛盾するこれらの要求条件に対処する方法として、以下の手順が推奨されます。

1. 最大負荷電流およびコア損失のグラフからµH単位で値を選択します。小さなインダクタを選択すると、軽負荷時に不連続動作モードになる場合がありますが、LT1374はいずれの動作モードでも良好に動作するように設計されています。少なくともトロイダルコアなどクローズド・コア形状の場合、低コア損失はコストが高くなることを覚えておいてください。コア損失のグラフに絶対損失と5W出力に対するパーセント損失を示します。実際のパーセント損失は、それぞれの状況に応じて計算する必要があります。

平均インダクタ電流が負荷電流と等しいと仮定し、インダクタが連続フォールト条件に耐えなければならないかどうかを決定します。たとえば最大負荷電流が0.5Aの場合、0.5Aインダクタは4.5Aの過負荷条件で破損することがあります。LT1374はフォルドバック電流制限機能を備えているため、完全短絡は実際にはより穏やかなものになります。

2. インダクタが飽和しないよう保証するために、全負荷電流でのピーク・インダクタ電流を計算してください。ピーク電流は、特にインダクタが小さく負荷が軽いときには、出力電流より大幅に高くなる可能性があるため、この手順を省略してはなりません。 鉄粉コアはソフトに飽和するため許容され、他方、

フェライト・コアは急激に飽和します。その他のコア材の飽和はこれらの中間になります。以下の式は連続モード動作を想定したものですが、不連続モードの場合はハイサイドでわずかに誤差が生じるだけなので、あらゆる条件に使用できます。

$$I_{PEAK} = I_{OUT} + \frac{V_{OUT} \Big(V_{IN} - V_{OUT}\Big)}{2\Big(f\Big)\!\Big(L\Big)\!\Big(V_{IN}\Big)}$$

V<sub>IN</sub> = 最大入力電圧 f = スイッチング周波数、500kHz

- 3. 高い磁界を放射するロッドやバレルなどの「オープン」コア形状でよいか、あるいはEMI問題を防止するためにトロイダルコアのようなクローズド・コアが必要かどうか判断してください。たとえば、誰でも磁気記憶媒体の隣にオープン・コアを置きたくはありません! ロッドやバレルは、安価で小形なため魅力的ですが、磁界放射が問題となる状況での計算方法のガイドラインがなく判断に迷います。

- 4. コア形状、ピーク電流(飽和を回避するため)、平均電流(温度上昇を制限するため)、および故障電流(インダクタが過熱した場合、ワイヤの絶縁が溶けて巻線間が短絡します)の要件を満足するインダクタを購入してください(表2の代表的な表面実装部品を参照)。高効率、ロープロフィール、高温動作などの優れた特質は、場合によっては大幅なコスト増になることを忘れないでください。価格に目安を付けるため最初に最も安い部品の価格を調べ、次に実際には何が欲しいかを追及してください。

- 5. 最初の選択を行った後、出力電圧リップル、セカンド・ソースなど、第二の事項を検討してください。 もしも最終的な選択に不安があるときは、リニアテクノロジーのエンジニアにご相談ください。広範なインダクタ・タイプを扱った経験のあるエンジニアが、ロープロフィール、表面実装部品などの最新の開発状況をご説明します。

表2.

| 182.                |               |              |              |                              |                       |                |

|---------------------|---------------|--------------|--------------|------------------------------|-----------------------|----------------|

| VENDOR/<br>PART NO. | VALUE<br>(µH) | DC<br>(Amps) | CORE<br>TYPE | SERIES<br>RESIS-<br>TANCE(Ω) | CORE<br>MATER-<br>IAL | HEIGHT<br>(mm) |

| Coiltronics         | •             |              |              |                              |                       | •              |

| CTX2-1              | 2             | 4.1          | Tor          | 0.011                        | КМμ                   | 4.2            |

| CTX5-4              | 5             | 4.4          | Tor          | 0.019                        | КМμ                   | 6.4            |

| CTX8-4              | 8             | 3.5          | Tor          | 0.020                        | КМμ                   | 6.4            |

| CTX2-1P             | 2             | 3.4          | Tor          | 0.014                        | 52                    | 4.2            |

| CTX2-3P             | 2             | 4.6          | Tor          | 0.012                        | 52                    | 4.8            |

| CTX5-4P             | 5             | 3.3          | Tor          | 0.027                        | 52                    | 6.4            |

| Sumida              | •             |              |              |                              |                       |                |

| CDRH125             | 10            | 4.0          | SC           | 0.025                        | Fer                   | 6              |

| CDRH125             | 12            | 3.5          | SC           | 0.027                        | Fer                   | 6              |

| CDRH125             | 15            | 3.3          | SC           | 0.030                        | Fer                   | 6              |

| CDRH125             | 18            | 3.0          | SC           | 0.034                        | Fer                   | 6              |

| Coilcraft           | •             |              |              |                              |                       |                |

| DT3316-222          | 2.2           | 5            | SC           | 0.035                        | Fer                   | 5.1            |

| DT3316-332          | 3.3           | 5            | SC           | 0.040                        | Fer                   | 5.1            |

| DT3316-472          | 4.7           | 3            | SC           | 0.045                        | Fer                   | 5.1            |

| Pulse               |               |              |              |                              |                       |                |

| PE-53650            | 4             | 4.8          | Tor          | 0.017                        | Fer                   | 9.1            |

| PE-53651            | 5             | 5.4          | Tor          | 0.018                        | Fer                   | 9.1            |

| PE-53652            | 9             | 5.5          | Tor          | 0.022                        | Fer                   | 10             |

| PE-53653            | 16            | 5.1          | Tor          | 0.032                        | Fer                   | 10             |

| Dale                |               |              |              |                              |                       |                |

| IHSM-4825           | 2.7           | 5.1          | Open         | 0.034                        | Fer                   | 5.6            |

| IHSM-4825           | 4.7           | 4.0          | Open         | 0.047                        | Fer                   | 5.6            |

| IHSM-5832           | 10            | 4.3          | Open         | 0.053                        | Fer                   | 7.1            |

| IHSM-5832           | 15            | 3.5          | Open         | 0.078                        | Fer                   | 7.1            |

| IHSM-7832           | 22            | 3.8          | Open         | 0.054                        | Fer                   | 7.1            |

Tor = Toroid

SC = Semi-closed geometry

Fer = Ferrite core material

52 = Type 52 powdered iron core material

$KM\mu = Kool M\mu$

#### 出力コンデンサ

出力コンデンサは通常、等価直列抵抗 ESR か値をもとに 選択します。これはESRの値によって出力リップル電圧が 決まるためです。500kHzでは、有極性コンデンサは本質的 に抵抗性です。ESRを低くすると体積が大きくなるため、 物理的に小形のコンデンサはESRが高くなっています。標 準的なLT1374アプリケーションでのESRの範囲は、0.05 ~0.2 です。標準的な出力コンデンサは、ESRが0.1 以下 のAVX社のTPSタイプ、100μF@10Vです。これは「D」サイ ズの表面実装型固体タンタル・コンデンサです。TPSコン デンサは、低ESRを実現するために特別に製造され試験さ れており、単位体積当たり最小のESRを実現しています。 容量値 μF)はそれほど重要ではなく、22μFから500μF以上 の容量でも十分に動作しますが、ESRの特徴は顕著に現れ ます。小型の22μF固形タンタル・コンデンサの場合は、 ESRが高く、大きな出力リップル電圧が現れます。表3に 代表的な固体タンタル表面実装型コンデンサを示します。

# 表3. 表面実装型固体タンタル・コンデンサのESRとリップル電流

| E Case Size           | ESR (Max., Ω) | Ripple Current (A) |

|-----------------------|---------------|--------------------|

| AVX TPS, Sprague 593D | 0.1 to 0.3    | 0.7 to 1.1         |

| AVX TAJ               | 0.7 to 0.9    | 0.4                |

| D Case Size           |               |                    |

| AVX TPS, Sprague 593D | 0.1 to 0.3    | 0.7 to 1.1         |

| C Case Size           |               |                    |

| AVX TPS               | 0.2 (typ)     | 0.5 (typ)          |

多くのエンジニアは、固体タンタル・コンデンサは高いサージ電流が加わると故障しやすいということを聞いたことがあると思います。これは歴史的な事実です。TPSタイプのコンデンサはサージ能力が特別に試験されていますが、サージ耐久性は出力コンデンサでは重大な問題ではありません。固体タンタル・コンデンサはターンオン・サージが高すぎると故障しますが、レギュレータ出力ではこのようなサージは発生しません。レギュレータ出力が完全に短絡するような高い放電サージがあっても、コンデンサには影響はありません。

入力コンデンサとは異なり、出力コンデンサのRMS リップル電流は通常は非常に低いため、リップル電流定 格が問題になることはありません。電流波形は 200mA<sub>RMS</sub>(標準値)の三角波です。これを計算する式は以下のとおりです。

出力コンデンサ・リップル電流(RMS):

$$I_{RIPPLE(RMS)} = \frac{0.29(V_{OUT})(V_{IN} - V_{OUT})}{(L)(f)(V_{IN})}$$

### セラミック・コンデンサ

容量値が高く低コストのセラミック・コンデンサが、より小型のケース・サイズで供給されるようになりました。これらはESRが非常に低いため、スイッチング・レギュレータ用としては魅力的です。残念ながら、ESRが低すぎてループ安定性の問題が生じる可能性があります。固体タンタル・コンデンサのESRは、5kHzから50kHzでループ「ゼロ」を生成するため、ループ位相マージンを許容範囲に収めるのに有効です。セラミック・ジンを許容範囲に収めるのに有効では容量性で、通常ESRが効果を発揮する前にESLとの間で共振します。これらはリップル電流定格が高く、ターンオン・サージ耐久性に優れているため、入力のバイパスに適しています。リニアテクノロジーは近いうちにセラミック・コンデンサの使い方を説明したデザイン・ノートの発行を予定しています。

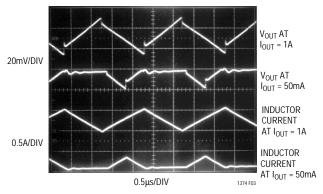

#### 出力リップル電圧

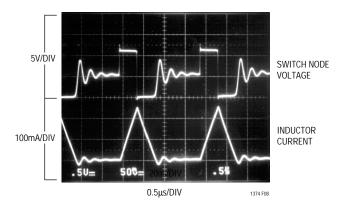

図3にLT1374の標準的な出力リップル電圧波形を示します。リップル電圧は、出力コンデンサの高周波数領域でのインピーダンスと、インダクタを流れるリップル電流で決定されます。インダクタを通して出力コンデンサに流れるピーク・ツー・ピーク・リップル電流は以下のとおりです。

$$I_{P-P} = \frac{\left(V_{OUT}\right)\left(V_{IN} - V_{OUT}\right)}{\left(V_{IN}\right)\left(L\right)\left(f\right)}$$

高周波数スイッチャの場合、リップル電流のスルーレートの和も関係する場合があり、次式から計算することができます:

$$\Sigma \frac{dI}{dt} = \frac{V_{IN}}{L}$$

ピーク・ツー・ピーク出力リップル電圧は、ピーク・ツー・ピーク・リップル電流とESRの積で形成される三角波と、寄生インダクタンス(ESL)およびリップル電流スルーレートによって形成される方形波の和です。容量性リアクタンスは、ESRまたはESLと比較して小さいものと仮定しています。

$$V_{RIPPLE} = (I_{P-P})(ESR) + (ESL) \Sigma \frac{dI}{dt}$$

例: $V_{IN}$  = 10V、 $V_{OUT}$  = 5V、L = 10 $\mu$ H、 ESR = 0.1 、 ESL = 10nHの場合、

$$I_{P-P} = \frac{(5)(10-5)}{(10)(10 \cdot 10^{-6})(500 \cdot 10^{3})} = 0.5A$$

$$\Sigma \frac{dI}{dt} = \frac{10}{10 \cdot 10^{-6}} = 10^{6}$$

$$V_{RIPPLE} = (0.5A)(0.1) + (10 \cdot 10^{-9})(10^{6})$$

$$= 0.05 + 0.01 = 60 \text{mV}_{P-P}$$

図3. LT1374のリップル電圧波形

### キャッチ・ダイオード

推奨されるキャッチ・ダイオード(D1)は、1N5821ショットキ、またはそれと同等なモトローラ製MBR330です。このダイオードの定格は、平均順方向電流が3Aで逆電圧が30Vです。また、標準順方向電圧は3Aで0.5Vです。このダイオードはスイッチ・オフ時間中にのみ導

通します。ピーク逆電圧はレギュレータの入力電圧と等 しくなります。また、通常動作時の平均順方向電流は次 式から計算できます。

$$I_{\text{CV}} = \frac{I_{\text{OUT}} \left( V_{\text{IN}} - V_{\text{OUT}} \right)}{V_{\text{IN}}}$$

この式では入力電圧対出力電圧の比が3.4:1を超えない限り、最大負荷電流を4.25Aにしても、3Aより大きな値にはなりません。大容量ダイオードを検討する唯一の理由は、入力電圧が高く、出力が過負荷(短絡ではない)になったワーストケース条件です。短絡状態では、フォルドバック電流制限によってダイオード電流は2.6A以下に低減されますが、出力が過負荷になっても出力電圧の1/3以下に低下しないときには、フォルドバックは機能しません。過負荷状態では、出力電流は6Aのピーク・スイッチ電流制限によって決定される5.7Aの標準値まで増加します。 $V_{IN}=15V$ 、 $V_{OUT}=4$ V(過負荷時は5V) および $I_{OUT}=5.7$ Aの場合、

$$I_{\text{IX}} = \frac{5.7(15-4)}{15} = 4.18A$$

これは短時間は安全ですが、これらの条件下で連続動作に耐えなければならない場合は、ダイオード・メーカに問い合わせてください。

### BOOSTピンの考慮事項

大部分のアプリケーションでは、ブースト用部品として 0.27µFコンデンサと1N914または1N4148ダイオードを使用します。アノードは安定化出力電圧に接続され、ブースト・コンデンサの両端に安定化出力とほぼ同じ電圧を発生します。特定のアプリケーションでは、アノードを非安定化入力電圧に接続する場合もあります。これは安定化出力電圧が非常に低い(3V以下)か、あるいは入力電圧が5V以下のときに必要になる場合があります。効率はコンデンサ値には影響されませんが、最小入力電圧の最悪条件下でも、十分再充電できるようにESRは1以下にしなければなりません。どのタイプのフィルムまたはセラミック・コンデンサでも十分に機能します。

警告! BOOSTピンのピーク電圧は、非安定化入力電圧とブースト・コンデンサ両端の電圧の和になります。これは一般に、BOOSTピンのピーク電圧が入力電圧+出力電圧と等しいことを意味しますが、レギュレータ入力にブースト・ダイオードが接続されているときはBOOSTピンのピーク電圧は入力電圧の2倍になります。BOOSTピン電圧が最大定格を超えないようにしてください。

ほとんどのアプリケーションにおいて、0.27μFのブース ト・コンデンサが十分効果的に働きますが、念のためこ こで詳細を説明しておきます。ブースト・コンデンサの 容量は、スイッチ・ドライブ電流条件によって決定しま す。スイッチ・オン時間中にコンデンサに流れる電流は 約I<sub>OUT</sub>/50です。したがって、4.25Aのピーク負荷電流で は、全電流は85mAになります。コンデンサのリップル 電圧は、オン時間 x(電流/容量値)になります。つま リ、ΔV = (t<sub>ON</sub>) 85mA/C)です。t<sub>ON</sub> = 1.8μsの最悪条件下 でコンデンサのリップル電圧を、0.6V(あまり根拠のな い数字)以下に維持するには、コンデンサは0.27μFでな ければなりません。ブースト・コンデンサのリップル電 圧は重要なパラメータではないものの、コンデンサ両端 の最小電圧が3V以下に低下すれば、パワー・スイッチ が完全に飽和しないため、効率が低下します。絶対最小 コンデンサ値を求める近似式は以下のとおりです。

$$C_{MIN} = \frac{(I_{OUT} / 50)(V_{OUT} / V_{IN})}{(f)(V_{OUT} - 3V)}$$

f = スイッチング周波数 V<sub>OUT</sub> = 安定化出力電圧 V<sub>IN</sub> = 最小入力電圧

この式からは0.27μFよりかなり小さいコンデンサ値が得られますが、コンデンサの直列抵抗、温度による容量変動、出力過負荷などの二次的要素を考慮していないため注意が必要です。

### シャットダウン機能と低電圧ロックアウト

図4に、低電圧ロックアウト(UVLO)をLT1374に付加する方法を示します。一般にUVLOは入力電源が電流制限されているか、または比較的高い信号源抵抗をもつ状況で使用されます。スイッチング・レギュレータはソースから一定の電力を取り出すため、ソース電圧が低下するとソース電流は増加します。これはソースに対して負の抵抗負荷のようにみえ、ソースが電流制限されるか、または低ソース電圧状態で L "にラッチされる可能性があ

図4. 低電圧ロックアウト

ります。UVLOはレギュレータが、問題の発生する可能 性があるソース電圧で動作するのを防止します。

ロックアウトに対するスレッショルド電圧は約2.38Vで、内部2.42V基準電圧よりわずかに低くなっています。スレッショルド電圧時にはピンからは、3.5μAのバイアス電流が流れ出します。シャットダウン・ピンが開放されている場合は、内部で生成されたこのバイアス電流を使用してシャットダウン・ピンをデフォルトの"H"状態にします。低シャットダウン電流が問題にならないときは、R<sub>LO</sub>を10k 以下にすれば、この電流による誤差を最小限にすることができます。シャットダウン電流が問題になる場合は、R<sub>LO</sub>を100k まで高くすることができますが、このバイアス電流による誤差と温度変化を考慮しなければなりません。

$$R_{HI} = \frac{R_{LO}(V_{IN} - 2.38V)}{2.38V - R_{LO}(3.5\mu A)}$$

### V<sub>IN</sub> = 最小入力電圧

抵抗からシャットダウン・ピンまでの接続を短くし、プレーン間またはスイッチング・ノードまでの表面容量が最小になるようにしてください。高抵抗値を使用する場合は、スイッチング・ノードとの結合問題を回避するために、1000pFコンデンサを使用して、シャットダウン・ピンをバイパスしなければなりません。低電圧ロックアウト点にヒステリシスをもたせたい場合は、出力ノードに抵抗R<sub>FB</sub>を追加することができます。抵抗値は次式から計算できます。

$$\begin{split} R_{HI} = & \frac{R_{LO} \bigg[ V_{IN} - 2.38 \Big( \Delta V / V_{OUT} + 1 \Big) + \Delta V \bigg]}{2.38 - R2 \Big( 3.5 \mu A \Big)} \\ R_{FB} = & \Big( R_{HI} \Big) \Big( V_{OUT} / \Delta V \Big) \end{split}$$

R<sub>IO</sub>には25k を推奨します。

V<sub>IN</sub> = 入力電圧がトリップ・レベルまで低下したとき に、スイッチングが停止する入力電圧

ΔV = 入力電圧レベルでのヒステリシス

例:出力電圧が5V、入力電圧が12V以下に低下するとスイッチングが停止し、入力が13.5Vまで上昇しない限り再開しないようにします。したがって、 $\Delta$ Vは1.5Vであり、 $V_{IN}$  = 12Vになります。 $R_{LO}$ は25k にします。次式により、 $R_{HI}$ と $R_{FB}$ を求めます。

$$R_{HI} = \frac{25k \left[12 - 2.38 \left(1.5/5 + 1\right) + 1.5\right]}{2.38 - 25k \left(3.5\mu A\right)}$$

$$= \frac{25k \left(10.41\right)}{2.29} = 114k$$

$$R_{FB} = 114k \left(5/1.5\right) = 380k$$

### スイッチ・ノードの検討事項

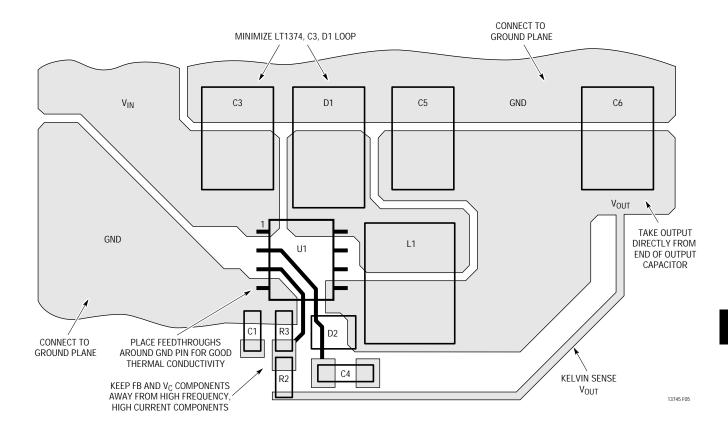

最大効率を実現するには、スイッチの立上り時間と立下 り時間を可能な限り短くします。放射と高周波での共振 の問題を防止するために、スイッチ・ノードに接続され る部品のレイアウトを適切に行うことが不可欠です。B (磁界)放射はキャッチ・ダイオード、スイッチ・ピン、 および入力バイパス・コンデンサのリードをできるだけ 短くすれば小さくなります。スイッチ・ピンとBOOST ピンに接続されるすべてのトレース長および面積を小さ くすれば、丘電界)放射が低くなります。スイッチング 回路の下に必ずグランド・プレーンを使用して、プレー ン間の結合を防止する必要があります。重要部品の推奨 レイアウトを図5に示します。帰還抵抗と補償用部品 は、スイッチ・ノードからできるだけ離してください。 また、キャッチ・ダイオードや入力コンデンサの大電流 グランド・パスは短くし、アナログ・グランド・ライン から離します。

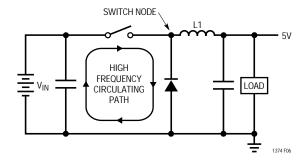

図6に高速スイッチング電流経路を図解します。クリーンなスイッチングと低EMIを保証するために、この経路のリード長はできる限り短くする必要があります。スイッチ、キャッチ・ダイオード、および入力コンデンサを含む経路だけが、立上りおよび立下り時間がnsの経路です。レイアウト上でこの経路を辿ってみると、それ以上ないほど短いことが理解できます。LT1374からダイオードや入力コンデンサを移動する場合は、その働きを

図5. 推奨レイアウト(トップサイドのみ表示)

図6. 高速スイッチング・パス

理解してから行ってください。その他の経路には直流と 500kHzの三角波の組合せが一部含まれているだけなの で、それほど重要ではありません。

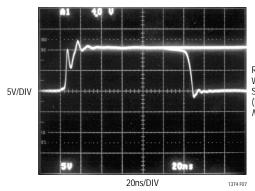

#### 寄生共振

スイッチ・ノードではときどき、共振すなわち「リンギング」がみられます(図7参照)。スイッチ、ダイオード、入力コンデンサのリード・インダクタンスとダイオードの容量によって、スイッチ立上り時間に続いて非常に高い周波数のリンギングが発生します。ショットキ・ダイオードはきわめで"Q"の高い接合容量をもっており、高周波数で励振されると何サイクルもリンギングが続く可能性があります。入力コンデンサ、ダイオード、およびスイッチ・パスの全リード長が2.54cmであれば、そのインダクタンスは約25nHになります。スイッチ・オフでは、これは入力電圧に加えてNPN出力デバイス両端でス

RISE AND FALL WAVEFORMS ARE SUPERIMPOSED (PULSE WIDTH IS NOT 120ns)

図7. スイッチ・ノード共振

図8. 不連続モード・リンギング

パイクを発生します。電流が大きい場合、レイアウトが適切でないとこのスパイクが10V~20Vまたはそれ以上になることがあり、潜在的に絶対最大スイッチ電圧を超えます。高信頼性動作を保証するには、スイッチ、キャッチ・ダイオード、および入力コンデンサの経路を可能な限り短くする必要があります。これを調べるときは、100MHz以上のオシロスコープを使用し、波形はパッケージのリードで観察しなければなりません。また、このスイッチ・オフ・スパイクによって、SWノードがグランド以下になります。LT1374はこの問題を緩和する特殊回路を内蔵していますが、1Vを超える負電圧が10ns以上続かないようにしなければなりません。図7の立下りエッジ・オーバシュートの詳細を観察するには、100MHz以上のオシロスコープでないと使えないことに注意してください。

また、スイッチ・オフ時間中にインダクタ電流がゼロになるほど負荷電流が低い場合は、スイッチ・オフ時間中にさらに低い周波数のリンギングがみられます(図8参照)。スイッチおよびダイオード容量がインダクタと共振して、1MHzから10MHzで減衰リンギングを生じます。このリンギングはレギュレータに影響はなく、EMIの大きな要因になるようなことも考えられません。それを抵抗スナバで減衰させようとすると効率が低下します。

### 入力のバイパスと電圧範囲

### 入力バイパス・コンデンサ

降圧コンバータには入力電源からパルス状の電流が流れます。これらパルスの平均高さは負荷電流と等しく、デューティ・サイクルはVour/Vinになります。この電流の立上りと立下りは非常に高速です。入力電源のローカル・バイパス・コンデンサは、レギュレータを適切に動作させ、入力電源に帰還するリップル電流を少なくするために必要です。このコンデンサは、タイトなローカル・ループにスイッチング電流を流してEMIを抑えます。

入力バイパス・コンデンサのリップル定格を低く見積 もったりμFの値に固執しないでください。入力コンデンサはすべてのスイッチング電流リップルを吸収するためのものであり、そのRMS値は負荷電流の1/2になる可能性があります。信頼性の高い動作を保証するために、コンデンサのリップル電流定格を遵守しなければなりません。多くの場合、必要なリップル定格を得るために、

2個のコンデンサを並列に接続する必要があります。電力の分担を確実にするため、両方のコンデンサは容量値とメーカが同じものでなければなりません。コンデンサの実際値( $\mu$ F)は、500kHzでは5 $\mu$ F以上は基本的に抵抗となるため、特に重要ではありません。RMSリップル電流定格が重要なパラメータです。実際のRMS電流は次式で計算できます。

$$I_{\text{RIPPLE}\left(\text{RMS}\right)} \!=\! I_{\text{OUT}} \sqrt{V_{\text{OUT}}\!\left(V_{\text{IN}}\!-V_{\text{OUT}}\right)\!/\left(V_{\text{IN}}\right)^2}$$

平方根内の項は、入力電圧が出力の2倍のときに最大値の0.5になり、比較的広い入力電圧範囲で0.5付近の値に留まります。したがって、単にワーストケース値を使用し、RMSリップル電流を負荷電流の1/2と仮定するのが一般的な方法です。LT1374の場合は4.5Aの最大出力電流では、入力バイパス・コンデンサは2.25Aのリップル電流で規定しなければなりません。しかし、最終リップル電流定格を選択する場合は、二次的な検討事項が多数あることに注意してください。これらには、周囲温度、平均対ピーク負荷電流、装置の動作スケジュール、おび所要製品寿命期間などが含まれます。詳細については、アプリケーション・ノート19および46、そしてデザイン・ノート95を参照してください。

### 入力コンデンサの種類

レギュレータの入力で使用するコンデンサの種類を選択 する場合、いくつかの注意事項があります。アルミニウ ム電解コンデンサは低コストですが、必要なリップル電 流定格を満足させるには物理的形状が大きく、サイズの 制約(特に高さ)のため使用できない場合があります。現 在、大きな容量のセラミック・コンデンサが入手可能に なりました。セラミック・コンデンサはリップル電流と 電圧定格が高いため入力のバイパスには最適です。ただ し、コストはかなり高く実装面積も大きくなる可能性が あります。固体タンタル・コンデンサも、起動時に大き なサージ電流が発生すると時に故障することを除いて は、良い選択といえます。固体タンタル・コンデンサは 短絡すると、明るい白色光を発っしながら多量の不快な 煙を出して燃え上がる可能性があります。この現象が発 生するのは全部のユニットのうちのごく少数ですが、一 部のOEMメーカは高サージ・アプリケーションでの使 用を禁じています。レギュレータの入力バイパス・コン デンサには、バッテリや大容量ソースが接続されていると、高サージが加わる可能性があります。一部のメーカがサージ能力を特別に試験したタンタル・コンデンサ・ライン(AVX TPSシリーズなど、表3参照)を開発しましたが、これらのユニットでも入力電圧サージがコンデンサの最大電圧定格に接近した場合は、故障する可能性があります。AVXは、高サージ・アプリケーションの場合はコンデンサ電圧を2:1にディレーティングすることを推奨しています。最大電圧定格は50Vですので、入力バイパスに固体タンタル・コンデンサを使用する場合は、25Vが実用上の上限になります。

入力電圧がデータシートで規定される最小値に非常に近い場合は、大きなコンデンサが必要になることがあります。スイッチ・オン時間でのわずかな電圧降下は通常問題になることはありませんが、入力電圧が非常に低い場合は入力電圧が最小仕様以下に低下するため、動作が不安定になるおそれがあります。入出力電圧差が最小値に近くなると問題が発生する可能性があります。容量性リアクタンスがこれらの項と比較して小さいため、これらの電圧降下の振幅は、通常コンデンサのESRとESLに関係します。ESRが支配項となる傾向があり、あるコンデンサ・タイプにおいて、コンデンサの物理的サイズに反比例します。

### 同期(-SYNCオプション)

LT1374-SYNCではSHDNピンがSYNCピンに置き換えら れており、内部発振器を外部信号に同期させるのに使用 します。SYNC入力は、10%から90%のデューティ・サ イクルで、ロジックレベル" L"から最大同期スレッショ ルドを通過しなければなりません。この入力は、ロジッ ク・レベル出力から直接ドライブできます。同期範囲は 初期動作周波数から最大1MHzまでです。つまり、実用 最小同期周波数は標準動作周波数(500kHz)ではなく、 最悪の場合の高自励発振周波数(550kHz)に一致するこ とを意味します。700kHz以上で同期させるときには、 同期周波数が高くなるほど、低調波スイッチングを防止 するのに使用した内部スロープ補償の振幅が小さくなる ため、注意が必要です。この種の低調波スイッチング は、入力電圧が出力電圧の2倍より低いときに発生しま す。インダクタ値が高いほど、この問題が解消される傾 向があります。この原因をスロープ補償が不十分と考え

る前に、まず周波数補償のセクションに記載されている別の低調波スイッチングの原因についての説明を参照してください。アプリケーション・ノート19に、スロープ補償に関する詳細が記載されています。

起動時に、 $V_C$ がFBピンでクランプされているとき(図2、Q2参照)、同期機能はディスエーブルされます。これによって、周波数フォルドバックが短絡出力状態でも動作することができます。通常動作中、FBピンが1.5Vに達するまで、スイッチング周波数は内部発振器によって制御され、その後でSYNCピンが機能するようになります。同期が不要なときは、このピンはグランドに接続しておいてください。

### 熱に関する計算

LT1374チップの消費電力は、スイッチDC損失、スイッチAC損失、ブースト回路電流、入力消費電流の4種類の要素で構成されます。以下にこれら各損失の計算方法を示します。これらの式は連続モード動作を仮定していますので、軽負荷電流時の効率を計算するのに使用してはなりません。

### スイッチ損失:

$$P_{SW} = \frac{R_{SW}(I_{OUT})^2(V_{OUT})}{V_{IN}} + 24ns(I_{OUT})(V_{IN})(f)$$

#### ブースト電流損失:

$$P_{BOOST} = \frac{V_{OUT}^2 (I_{OUT} / 50)}{V_{IN}}$$

#### 消費電流損失:

$$P_{Q} = V_{IN}(0.001) + V_{OUT}(0.005) + \frac{\left(V_{OUT}^{2}\right)(0.002)}{V_{IN}}$$

$R_{SW}$  = スイッチ抵抗(  $\approx 0.07$  ) 24ns = 等価スイッチ電流/電圧オーバラップ時間 f = スイッチ周波数

例: V<sub>IN</sub> = 10V、V<sub>OUT</sub> = 5V、およびI<sub>OUT</sub> = 3Aの場合、

$$P_{SW} = \frac{(0.07)(3)^{2}(5)}{10} + (24 \cdot 10^{-9})(3)(10)(500 \cdot 10^{3})$$

= 0.32 + 0.36 = 0.68W

$$P_{BOOST} = \frac{(5)^2 (3/50)}{10} = 0.15W$$

$$P_Q = 10(0.001) + 5(0.005) + \frac{(5)^2(0.002)}{10} = 0.04W$$

全消費電力は0.68 + 0.15 + 0.04 = 0.87Wです。

LT1374のパッケージの熱抵抗は内部、または裏面プレーンの存在に影響されます。SOパッケージの下側をすべてプレーンにした場合、熱抵抗は約80 /Wになります。プレーンがないと熱抵抗は約120 /Wに増えます。ダイ温度を計算するには、次のとおり希望のパッケージに対する適切な熱抵抗値を使用し、最悪の周囲温度に加算してください。

$$T_J = T_A + J_A(P_{TOT})$$

50 の周囲温度で、SO-8パッケージ( $_{JA}$  = 80 /W)を使用する場合は、以下のようになります。

$$T_1 = 50 + 80(0.87) = 120$$

デバイスの下側が良好な銅プレーンであるDDパッケージの場合、熱抵抗は約30 /Wになります。上記の条件では次のようになります。

$$T_J = 50 + 30(0.87) = 76$$

ダイ温度は低入力電圧で最も高くなるため、熱計算には 連続最低入力動作電圧を使用してください。

### 周波数補償

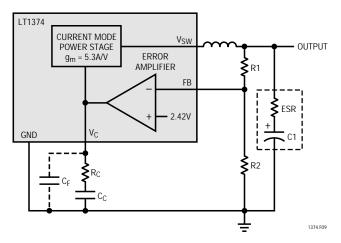

スイッチング・レギュレータのループ周波数補償は、高効率を実現するために使用されるリアクティブ部品が帰還ループ内に複数のポールを形成するため、複雑な問題になる可能性があります。従来の降圧コンバータに使用されるインダクタと出力コンデンサは、実際に共振タンク回路を形成し、共振周波数においてピーキングや急激な180°位相シフトを生じることがあります。対照的に、LT1374は「電流モード」アーキテクチャを使用して、インダクタによって形成される位相シフトを軽減していま

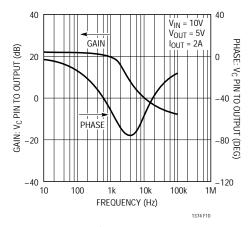

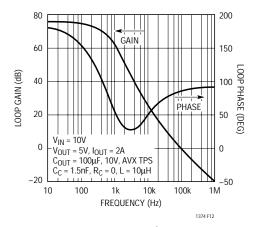

す。この基本接続を図9に示します。図10に、 $V_c$ ピンから出力を測定したLT1374の電力部の位相と利得のボード・プロットを示します。利得はLT1374の電力部の5.3A/Vのトランスコンダクタンスと、出力からグランドまでの実効複素インピーダンスで設定されます。利得は100 $\mu$ Fの出力コンデンサで設定される600Hzのポール周波数より高い周波数で、なだらかにロールオフします。位相の低下は約70 に制限されています。位相が回復し、利得はコンデンサのESR(0.1)で設定されるゼロ周波数( $\approx$ 16kHz)で安定します。

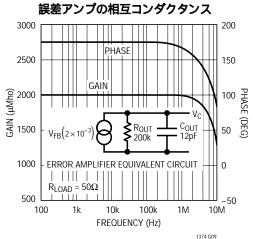

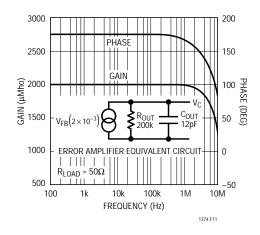

誤差アンプのトランスコンダクタンスの位相と利得を図11に示します。誤差アンプは、200k の出力インピーダンスに12pFを並列に接続した2000μモーの相互コンダクタンスとしてモデル化することができます。すべての実

用アプリケーションでは、V<sub>C</sub>ピンからグランドへの補償回路のインピーダンスは、500Hz以上の周波数では、アンプの出力インピーダンスよりはるかに低くなります。つまり、誤差アンプの特性自体はループに過剰な位相変化を与えないことを意味し、誤差アンプ部の位相/利得特性は外部補償回路によって完全に制御されます。

図12に、1.5nFの補償コンデンサを使用した場合の全ループ位相/利得特性を示します。誤差アンプは530Hzにポールをもち、位相は90 stでロールオフしそこで停滞します。全ループは低周波数において74dBの利得をもち、100kHzでユニティ・ゲインにロールオフします。位相は出力コンデンサのESRによって位相が10kHzより高くなるまで、2ポール特性を示します。位相マージンはユニティ・ゲインで約75 です。

図9. ループ応答のモデル

図10. ∨ ピンから出力への応答

図11. 誤差アンプ利得と位相

図12. 全ループ特性

アナログに詳しい人は4.4kHz周辺で、位相がゼロ位相マージンラインに非常に接近していることに気付くはずです。これはスイッチング・レギュレータに典型的なものであり、広範な負荷で動作するレギュレータでは特に顕著です。この低位相領域はユニティゲイン付近に発生しない限り問題になることはありません。実際には出力コンデンサのESRの可変性が、ループ応答に関する他のすべての効果を支配する傾向があります。ESRが変化するとユニティ・ゲインが変化しますが、同時に位相も変化します。したがって、ESRのきわめて広い範囲(≥±3:1)で十分な位相マージンが維持されます。

### 補償回路の抵抗について

誤差アンプの補償に「ゼロ」を追加してループの位相マージンを増大させることは、スイッチング・レギュレータの設計では一般に行われていることです。このゼロは補償コンデンサと直列の抵抗( $R_c$ )という形で外部回路に形成されます。一般に、この抵抗のサイズを増やすほどループの安定性が向上しますが、この値には2つの限界があります。1つは、出力コンデンサのESRと大きな値の $R_c$ の組合せによっては、利得余裕が完全にロールオフを停止するため利得余裕の問題が発生する場合があります。利得余裕がゼロになる $R_c$ の近似式は以下のとおりです。

$$R_{c}(\mu - プ利得 = 1) = \frac{V_{OUT}}{(G_{MP})(G_{MA})(ESR)(2.42)}$$

$G_{MP}$  = 電力段のトランスコンダクタンス = 5.3A/V  $G_{MA}$  = 誤差アンプのトランスコンダクタンス = 2(10 $^{-3}$ ) ESR = 出力コンデンサのESR 2.42 = 基準電圧

V<sub>OUT</sub> = 5VおよびESR = 0.03 の場合、R<sub>C</sub>を6.5k にすると利得余裕がゼロになり、これが上限です。第二の制限は、理論的な小信号動作には何も関係ありません。この抵抗は、スイッチング周波数での利得を含む誤差アンプの高周波数利得を設定します。スイッチング周波数利得が必要以上に高いと、出力リップル電圧が大きな振幅でV<sub>C</sub>ピンに現れてレギュレータの適切な動作が乱されます。極端な場合には低調波スイッチングが発生しますが、これはスイッチ・ノードのパルス幅が変化することによって確認できます。さらにひどい場合には、出力電

圧がほぼ適切であってもレギュレータから異常な音が聞こえることがあります。ボード・プロットは振幅とは無関係な解析であるため、これが理論的なボード・プロットに現れることはありません。 テストにより、 $V_{c}$ のリップル電圧を $100mV_{P-P}$ 以下に保持すれば、LT1374は正常に動作することが分かっています。以下の式は、ループに $R_{c}$ が追加されたときの $V_{c}$ リップル電圧を推定するものです。ただし、 $R_{c}$ は500kHzにおける $C_{c}$ のリアクタンスと比較して大きいと仮定します。

$$V_{C(RIPPLE)} = \frac{(R_{C})(G_{MA})(V_{IN} - V_{OUT})(ESR)(2.4)}{(V_{IN})(L)(f)}$$

GMA = 誤差アンプの相互コンダクタンス(2000μモー)

LT1374のコンピュータ・シミュレーションが、3k の直列補償抵抗により、十分な利得余裕をもつ最良の全ループ応答が得られることを示した場合は、 $V_{IN}$  = 10V、 $V_{OUT}$  = 5V、ESR = 0.1 、 L = 10 $\mu$ Hでの $V_{C}$ ピンのリップル電圧は、次のようになります。

$$V_{C(RIPPLE)} = \frac{(3k)(2 \cdot 10^{-3})(10 - 5)(0.1)(2.4)}{(10)(10 \cdot 10^{-6})(500 \cdot 10^{3})} = 0.144V$$

この高いリップル電圧は、低調波スイッチングを発生させる可能性があります。ほとんどの状況では、抵抗値を妥当な値(この場合は2k 以下)にすれば十分な位相マージンが得られ、低調波問題は起こりません。また、抵抗を大きくしないと許容できる位相応答が得られない場合もあり、その際は何らかの手段を講じて $V_C$ ピンのリップル電圧を制御する必要があります。推奨方法は、 $V_C$ ピンの $R_C/C_C$ 回路と並列にコンデンサ( $C_F$ )を追加することです。このコンデンサのポール周波数は一般にスイッチング周波数の1/5に設定されているため、スイッチング・リップルを大幅に減衰しますが、ループのユニティゲイン周波数で許容できない位相シフトが追加されることはありません。

R<sub>C</sub>=3k の場合、

$$C_F = \frac{5}{(2\pi)(f)(R_C)} = \frac{5}{2\pi(500 \cdot 10^3)(3k)} = 531pF$$

#### ループ安定性のテスト方法

LT1374の「標準的」な補償は、 $R_C$  = 0の場合は $C_C$ に1.5nFコンデンサを使用して行います。ほとんどのアプリケーションはこの補償で対応できますが、ループ補償部品の「最適」値は、さまざまな面で十分に制御されないパラメータに依存します。これらには、インダクタ値(製造公差、負荷電流、およびリップル電流変動により $\pm$ 30%)、出力容量(製造公差、温度、経年劣化、および負荷変動により $\pm$ 20%から $\pm$ 50%)、出力コンデンサのESR(製造公差、温度、および経年劣化により $\pm$ 200%)、そしてDC入力電流および出力負荷電流などがあります。したがって、設計者は最終設計をチェックして、これらすべての偏差に対応でき「耐久性」も高いことを確認することが重要です。

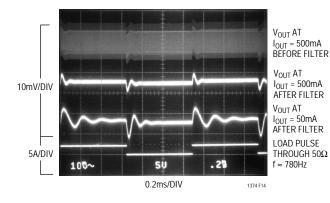

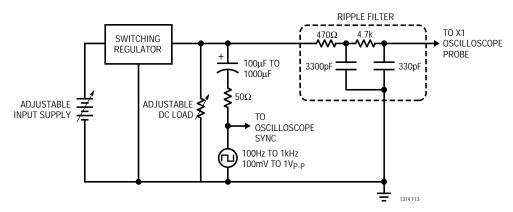

図13の回路を使用し、出力で過渡応答を観測しながら、レギュレータ出力にパルス負荷を与えてスイッチング・レギュレータのループ安定性をチェックします。レギュレータ・ループは、50Hz~1kHzの比較的低い周波数において小さな過渡AC負荷電流で「ヒット」されます。これにより、図14に示すように出力が数mVジャンプしますが、図14に示すように出力が数mVジャンプしますが、位相マージングしますが、位相マージンやリングしますが、位相マージンや」が発生します。リンギングの数は安定度を表し、このリンギング周波数はループの概略のユニティゲイン周波数を示します。ループが非直線動作になるほど振幅が高くなければ、信号の振幅は特に重要ではありません。

レギュレータの出力には、必要な低周波数過渡情報と適度な高周波 500kHz)リップルの両方が含まれています。リップルがあると小さな過渡信号の観測が困難なため、2ポール、100kHzフィルタを追加します。このフィルタは特に重要なものではなく、過渡信号を多少減衰させたとしても、振幅は重要でないため、これが問題になることはありません。

この回路構成が正しく動作していることを確認してから、 負荷電流と入力電圧を変化させて、過渡応答がリンギン グ」すると思われる組合せがみつかるかどうか試みまし た。この手順により、最良のループ安定性または高速ルー プ過渡応答を実現する調整が可能になる場合があります。 R<sub>C</sub>として数k の抵抗を追加すれば、ほとんどの場合は ループ応答が改善されるはずです。ただし、前にも説明し たように、1k 以上のR<sub>C</sub>を使用するとV<sub>C</sub>ピンのリップル を制御するために、さらにC<sub>F</sub>を追加しなければならない場 合があるため必要なときにだけ実施してください。

図14. ループ安定性のチェック

図13. ループ安定性のテスト回路

すべて順調であれば、温度特性を明確にするため回路 (特に出力コンデンサ)にヒートガンと冷却スプレーを使用します。

この手順では部品の初期許容差は考慮していないことを 覚えておいてください。部品値のバラツキによって問題 が発生しないようにするために、すべての負荷およびラ イン条件で、かなりクリーンな応答が観察できなければ なりません。注記事項:マーフィーによれば、製造工程 で変更される可能性の高い部品は出力コンデンサで、 メーカ間での(ESRの)偏差が大きく問題が生じるおそれ があります。製造時に出力コンデンサの供給元まで検査 するほうが賢明です。

図14のI<sub>LOAD</sub> = 50mAで明らかなように、「クリーンな応答」規則の例外は負荷が非常に軽い場合です。スイッチング・レギュレータは、負荷が非常に軽いときにループ応答が極端に変化する傾向があります。これはほとんどの場合インダクタ電流が不連続になるためです。結果的に、非常に低速ながら安定した特性が得られます。結果が1つの可能性としては位相マージンが小さいことにより、1つの可能性としては位相マージンが生じることによりないます。幸い軽負荷時の低位相マージンは、特に部品のバラツキに敏感ではないため、過渡応答テストで妥当な結果が得られれば製造時にも問題になりません。軽負荷時のリンギングの周波数は部品許容差に応じて変動しますが、位相マージンは通常一定です。

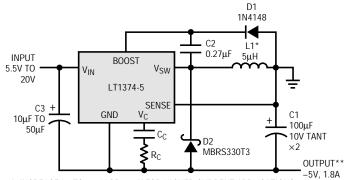

#### 正 - 負コンバータ

図15の回路は接地形インダクタを使用した従来方式の正 - 負トポロジーです。ただし、ICチップが帰還信号を得る方法は標準的なアプローチとは異なります。それは、LT1374が正帰還信号しか受け入れず、グランド・ピンを安定化された負電圧出力に接続しなければならないためです。したがって、グランドに接続した抵抗分圧器(この場合にはセンス・ピン)がチップに適切な帰還電圧を供給します。

極性反転レギュレータは、基本スイッチング回路がバック・レギュレータとは異なります。電流は負荷電流よりはるかに大きなピーク・ツー・ピーク振幅の方形波として出力に供給されます。つまり、最大負荷電流はインダクタ値を大きくしても、LT1374の最大負荷電流4.5Aよりはるかに小さくなります。

- \* INCREASE L1 TO 10µH OR 20µH FOR HIGHER CURRENT APPLICATIONS. SEE APPLICATIONS INFORMATION

- \* MAXIMUM LOAD CURRENT DEPENDS ON MINIMUM INPUT VOLTAGE AND INDUCTOR SIZE. SEE APPLICATIONS INFORMATION

図15. 正 - 負コンパータ

それに対してバック・コンバータは、電流を負荷電流と等しいDCレベルに重畳された三角波として出力に供給し、インダクタを大きくすると負荷電流が4.5Aに近づく可能性があります。正 - 負コンバータの出力リップル電圧は、バック・コンバータよりはるかに高くなります。出力コンデンサのリップル電流も非常に高くなります。以下の式を使用して、正 - 負コンバータの動作条件を計算することができます。

### 最大負荷電流:

$$I_{MAX} = \frac{\left[I_{P} - \frac{\left(V_{IN}\right)\!\left(V_{OUT}\right)}{2\!\left(V_{OUT} + V_{IN}\right)\!\left(f\right)\!\left(L\right)}\right]\!\left(V_{OUT}\right)\!\left(V_{IN} - 0.35\right)}{\left(V_{OUT} + V_{IN} - 0.35\right)\!\left(V_{OUT} + V_{F}\right)}$$

$I_P$  = 最大定格スイッチ電流  $V_{IN}$  = 最小入力電圧  $V_{OUT}$  = 出力電圧  $V_F$  = キャッチ・ダイオードの順方向電圧

v<sub>F</sub> = キャッテ・タイオートの順方向電 0.35 = 4.5Aでのスイッチ電圧降下

例:  $V_{IN(MIN)}$  = 5.5V、 $V_{OUT}$  = 5V、L =  $10\mu$ F、 $V_F$  = 0.5V、 $I_P$  = 4.5Aの場合、 $I_{MAX}$  = 2Aになります。この式では、LT1374の最大定格電流  $I_P$  )が、デューティ・サイクルが50%以上の場合はわずかに低下することを考慮していないことに注意してください。デューティ・サイクルが50%を超える(入力電圧が出力電圧より低い)場合は、電気特性表にある実際の $I_P$ 値を使用してください。

動作デューティ・サイクル:

$$DC = \frac{V_{OUT} + V_F}{V_{IN} - 0.3 + V_{OUT} + V_F}$$

(この式ではスイッチ損失に平均値を使用しているため、数パーセントの誤差が生ずる場合があります。)

上記の条件で:

$$DC = \frac{5 + 0.5}{5.5 - 0.3 + 5 + 0.5} = 51\%$$

このデューティ・サイクルは十分50%に近く、I<sub>P</sub>は4.5Aと推定できます。

### 出力分割器

可変部品を使用する場合、 $V_{OUT}$ に接続する抵抗(R2)は約5k に設定する必要があります。R1は次式から計算されます。

$$R1 = \frac{R2(V_{OUT} - 2.42)}{2.42}$$

### インダクタ値

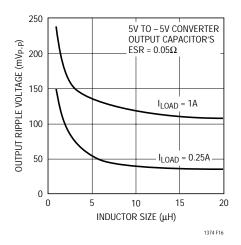

正・負コンバータは、バック・コンバータとは異なり、大きなインダクタ値を使用して出力リップル電圧を減らすことはできません。500kHzでは25µH以上の値を使用しても、出力リップルはほとんど変化しません。図16のグラフに、各種のインダクタ値に対する5Vから・5Vへのコンバータのピーク・ツー・ピーク出力リップル電を示します。したがって、一般にインダクタを選択よるを選がしては、最大スイッチ電流定格を超えないよう保証することです。これによって、使用可能な最小イン負でを立ってはいいとき、それが不要な高出力リップル電圧を生ずる値になることがあります。多くの場合、出力りを生ずる値になることがあります。グラフからわかるように、インダクタを大きくしても、いくらでも低

図16. 正 - 負コンバータのリップル電圧

いリップルが得られるとは限りませんが、インダクタを小さくするとリップルが高くなる可能性があります。

必要な最小インダクタ・サイズを計算する際に困難なことは、スイッチ電流が4.5Aの臨界点で、スイッチャが連続モードになるかを最初に知らなければならないことです。最初のステップは、下記の式を使用して、スイッチャが連続モードを使用しなければならない負荷電流を計算することです。負荷電流がこれより小さい場合は、不連続モードの式を使用して必要な最小インダクタを計算してください。負荷電流が高い場合は連続モードの式を使用してください。

連続モードで必要な出力電流:

$$I_{CONT} = \sqrt{\frac{\left(V_{IN}\right)^2\!\!\left(I_P\right)^2}{4\!\left(V_{IN} + V_{OUT}\right)\!\left(V_{IN} + V_{OUT} + V_F\right)}}$$

不連続モードでの最小インダクタ:

$$L_{MIN} = \frac{2(V_{OUT})(I_{OUT})}{(f)(I_P)^2}$$

連続モードでの最小インダクタ:

$$L_{MIN} = \frac{\left(V_{IN}\right)\!\!\left(V_{OUT}\right)}{2\!\!\left(f\right)\!\!\left(V_{IN} + V_{OUT}\right)\!\!\left[I_P - I_{OUT}\!\!\left(1 + \frac{\left(V_{OUT} + V_F\right)}{V_{IN}}\right)\right]}$$

上記の例で、1Aの最大負荷電流を使用すれば以下の結果が得られます。

$$I_{CONT} = \sqrt{\frac{\left(5.5\right)^2 \left(4.5\right)^2}{4\left(5.5 + 5\right) \left(5.5 + 5 + 0.5\right)}} = 1.15A$$

これより不連続モードが使用されることが分かります。 必要な最小インダクタは次式から求まります。

$$L_{MIN} = \frac{2(5)(1)}{(500 \cdot 10^3)(4.5)^2} = 1 \mu H$$

実際には損失と値のバラツキを処理するため、インダク タは計算された最小値より約30%ほど大きくしなければ なりません。これより、このアプリケーションでは 1.3μHの最小インダクタが推奨されますが、リップル電 圧チャートを参照すると、出力リップル電圧は15µHの インダクタを使用した場合は1/2に低減できることが分 かります。最終決定を行うための経験則はありません。 並のリップルが必要で、大きなインダクタで対処できる ようであれば、それを使用してください。リップルが重 要でない場合は、小さなインダクタを使用してくださ い。リップルが非常に重要な場合は、いずれの場合も第 二のフィルタを追加する必要があります。その場合、低 インダクタンスのものが使用されます。出力リップル電 圧を決定する際は、出力コンデンサが別の重要な要素に なることを忘れないでください。グラフ(図16)に示す リップルは、ESRが0.1 の2つの並列コンデンサを使用 した場合です。これはAVXタイプTPS「D」または「E」サ イズの表面実装型固体タンタル・コンデンサでは妥当な 値ですが、最終的に選択するコンデンサについては、 ESR特性を慎重に検討してください。

入力および出力コンデンサのリップル電流

正電圧から負電圧へのコンバータには、入力コンデンサと出力コンデンサのいずれにも高いリップル電流が流れます。コンデンサの寿命を長くするには、この電流のRMS値がコンデンサの高周波数リップル電流定格以下でなければなりません。以下の式でRMSリップル電流の概算値を求めることができます。この式は連続モードで大きなインダクタ値を想定したものです。小型のインダクタを使用すると、リップル電流は、特に不連続モード時に多少高くなります。正確な式は非常に複雑で、アプリケーション・ノート44の30および31ページに記載されています。本題の目的に対しては、単に余裕分の見込み係数(ff)を追加したものです。ffの値は高負荷電流されています。本題の目的に対しては、単に余裕分の見込み係数(ff)を追加したものです。ffの値は高負荷電流されてンダクタの場合、これは約2.0まで増大します。

コンデンサ

$$I_{RMS} = (ff)(I_{OUT})\sqrt{\frac{V_{OUT}}{V_{IN}}}$$

ff = 余裕分の見込みの係数(1.2~2.0)

### ダイオード電流

平均ダイオード電流は負荷電流に等しくなります。 ピーク・ダイオード電流はかなり高くなります。

#### ピーク・ダイオード電流:

連続モード=

$$I_{OUT} \frac{\left(V_{IN} + V_{OUT}\right)}{V_{IN}} + \frac{\left(V_{IN}\right)\!\left(V_{OUT}\right)}{2\!\left(L\right)\!\left(f\right)\!\left(V_{IN} + V_{OUT}\right)}$$

不連続モード =

$$\sqrt{\frac{2(I_{OUT})(V_{OUT})}{(L)(f)}}$$

起動時および出力過負荷時には、平均ダイオード電流は通常の負荷の場合よりはるかに高くなることを覚えておいてください。定格3A以下のダイオードを使用する場合、特に連続過負荷条件に耐える必要がある場合は注意してください。

### 標準的応用例

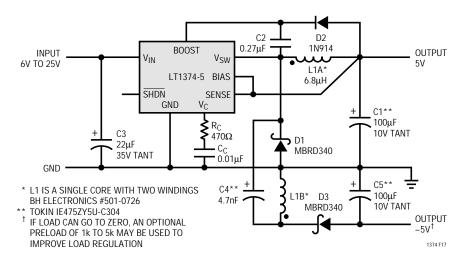

### デュアル出力SEPICコンバータ

図17の回路は、1つの磁気素子で正、負両方の5V出力を発生します。図に示す2つのインダクタは、実際には2巻線の1つの標準的なBH Electronicsインダクタです。5V出力のトポロジーは標準バック・コンバータです。 - 5Vトポロジーは、C4がない場合は単にバック・コンバータにフライバック巻線を結合したものです。C4はSEPIC Single-Ended Primary Inductance Converter)トポロジーを形成しており、レギュレーションを改善し、L1のリップル電流を低減します。C4がない場合、相対ローディングとカップリング損失のために、L1Bの電圧振幅はL1Aと異なります。C4はL1Bで等しい電圧振幅を維持するために、低インピーダンス・

パスを供給し、レギュレーションを改善します。フライバック・コンバータでは、スイッチ・オン時間中、L1Bには電流が流れないため、コンバータの全エネルギーはL1Aだけに蓄えられます。スイッチ・オフ時に、エネルギーは磁気結合によってL1Bに受け渡され、-5Vレールに電源を供給します。C4はスイッチ・オン時間中に、L1Bを正にし、電流が流れるようにして、L1BとC4にエネルギーを蓄積します。スイッチ・オフで、L1BとC4の両方に蓄えられているエネルギーが-5Vレールに電源を供給します。これによってL1Aの電流が減少し、L1B電流波形は方形波から三角波に変化します。この回路の詳細については、デザイン・ノート100を参照してください。

図17. デュアル出力SEPICコンパータ

### 関連製品

| 製品番号                  | 説明                              | 注釈                                  |

|-----------------------|---------------------------------|-------------------------------------|

| LT1074/LT1076         | 降圧スイッチング・レギュレータ                 | 入力40V、100kHz、5Aおよび2A                |

| LTC <sup>®</sup> 1148 | 高効率同期整流式降圧スイッチング・レギュレータ         | 外付けFETスイッチ                          |

| LTC1149               | 高効率同期整流式降圧スイッチング・レギュレータ         | 外付けFETスイッチ                          |

| LTC1174               | 高効率降圧および反転DC/DCコンバータ            | 0.5A、150kHzバースト・モード <sup>™</sup> 動作 |

| LT1176                | スイッチング・レギュレータ                   | PDIPパッケージのLT1076                    |

| LT1370                | 高効率DC/DCコンバータ                   | 42V、6A、500kHzスイッチ                   |

| LT1371                | 高効率DC/DCコンバータ                   | 35V、3A、500kHzスイッチ                   |

| LT1372/LT1377         | 500kHz/1MHz高効率1.5Aスイッチング・レギュレータ | 昇圧トポロジー                             |

| LT1435/LT1436         | 高効率降圧コンバータ                      | 外付けスイッチ、低ノイズ                        |

Burst Modeはリニアテクノロジー社の商標です。