資料・技術情報

ロジックICで構成した周波数カウンタの製作 【設計編 その3】

◎カウンタとラッチ

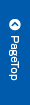

★ゲート後のブロック

ゲート後のブロックと各部の波形関係を図43に示します。

ゲート出力波形に注意してください。

ゲートをオープンしている間(ゲート時間)だけ波形整形回路からの信号が出力され、ゲートを閉じるカウンタへの信号はHレベル固定です。

★カウンタ

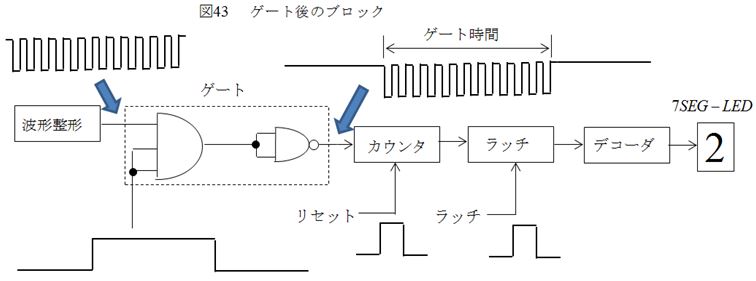

図44に74HC390のカウンタ接続を示します。

基準時間発生部の1/10分周は5進カウンタのクロックCKBにクロックを入力するデバイダ接続でしたが、カウンタ接続は2進カウンタのCKAへクロックを入力し、QAをCKBに接続すると10進カウンタになります。

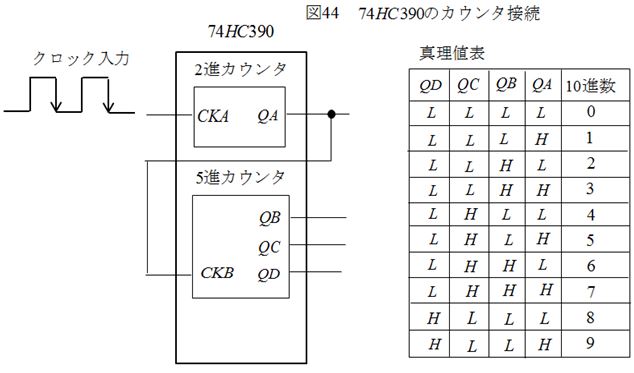

図45はこの時のタイミングチャートです。

クロック(CKA)が入る毎にカウントアップしていきます。

10進ですから、9の次は0(ゼロ)に戻ります。

★Dラッチ

ラッチはデータを保持する装置で、今回の場合、カウント値をデコーダにセットする役目をしています。

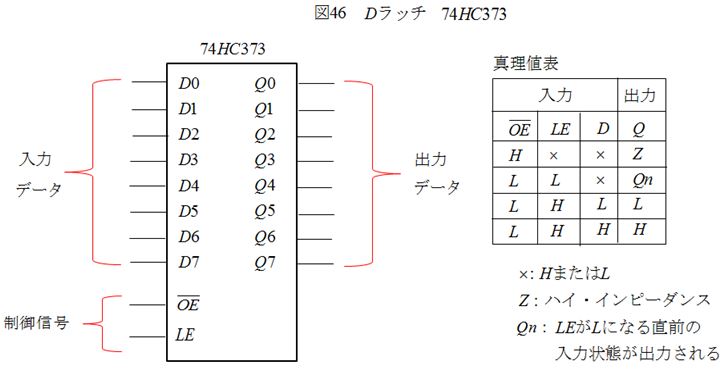

今回は図46のラッチIC 74HC373を用いています。

Dタイプ・ラッチと呼ばれるもので入力データはD0~D7の8ビット、出力はQ0~Q7でDとQは同じ数字に対応しています。

制御信号はOEバーとLEの2つで、OEバーは他の入力条件によらず、Hにすると出力(Q)はハイ・インピーダンスになります。

LEがラッチの制御信号で、HではD入力がそのまま出力されます。

また、LEをLにすると、Lになる前の入力状態が出力され、LEがLの間は入力が変化しても出力は変化しません。

これがラッチです。

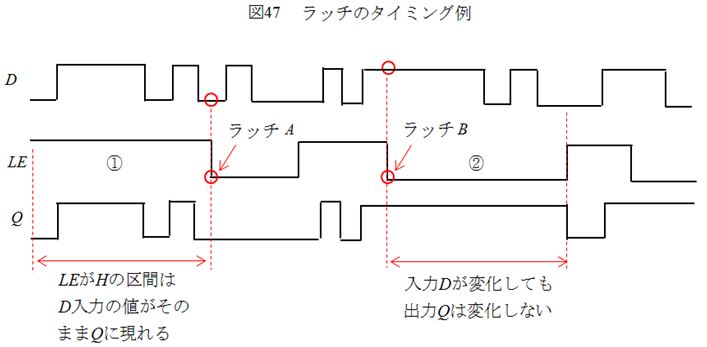

図47にタイミング例を示します。

LEがHになっている①の区間ではD入力の状態(値)がそのままQに現れています。

表現を変えると、LEがHの時、DはQに筒抜け状態になり、ゲートオープンとも言えます。

LEがLに変化するラッチのポイント(A、B)ではその時のD入力の状態が出力に固定され、D入力が変化しても影響されません。

これも別な表現をすれば最後のデータを保持し、ゲートを閉じたような状態です。

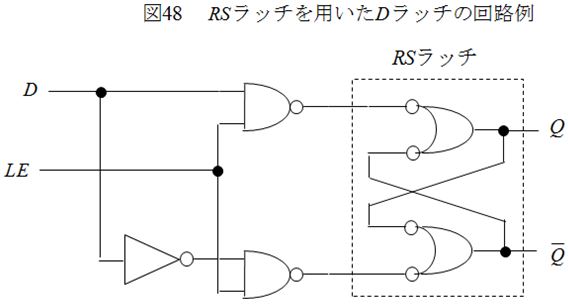

74HC373の内部はどのような構成なのか分かりませんが、個別のゲートICで構成したDラッチの回路例を図48に示します。

負論理入力のRSラッチの前に制御回路を追加したものです。

74HC373のようにOEバーの機能はありませんが、出力はQとQバーの2つが得られ、真理値表は図46と同じになります。

1ビットだけDラッチが欲しい場合はこのような回路を覚えておくと便利です。

NANDゲートが4個とNOTゲートが1個の構成ですが、この回路を工夫すればNANDゲート4個で構成することができます。

★カウンタとラッチの接続

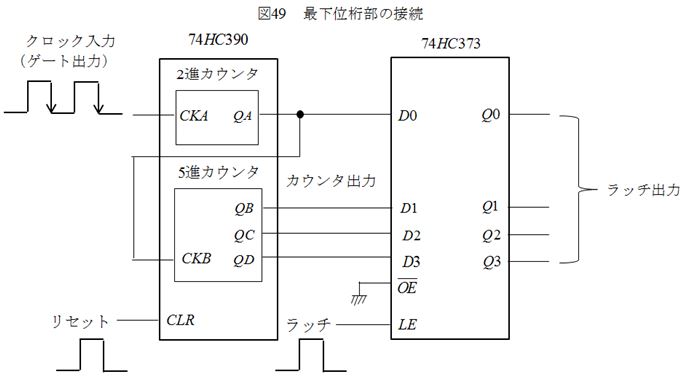

表示は4桁ですが、基本的なカウンタとラッチの接続を最下位桁(1位)を例として図49に示します。

74HC390は10進カウンタが2個、74HC373は8ビットです。

1桁は4ビットですから、それぞれ半分ずつ接続することになり、図49の74HC373は4ビットで表現しています。

カウンタ出力はQAが最下位ビットですから、この例ではQAをD0に対応し、D0の出力はQ0です。

もう一つの74HC373のOEバーは今回の場合用いないのでGNDへ接続し、常にQ出力が出ている状態にしておきます。

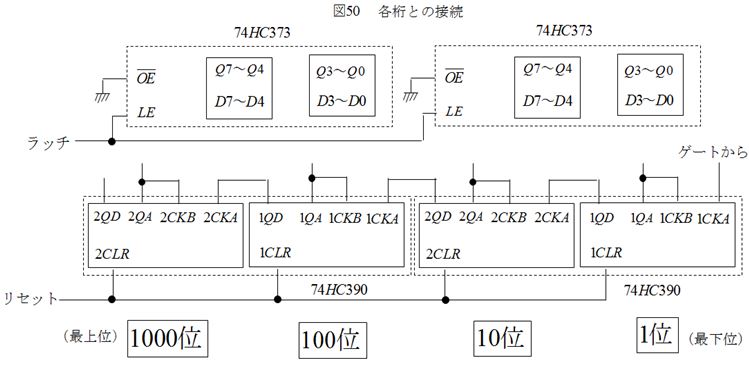

図50は各桁との接続です。

最下位桁のクロックはゲート出力ですが、上位桁は下位桁のQDを接続します。

各リセット端子(CLR)は共通に接続し、これに制御回路からのリセット信号を接続します。

ラッチも各LE端子を共通接続し、これも制御回路からのラッチ信号を接続します。

カウンタ出力(QA~QD)とD0~D7の接続はこの図では省略していますが、実際には図49のとおりです。

★タイミング詳細

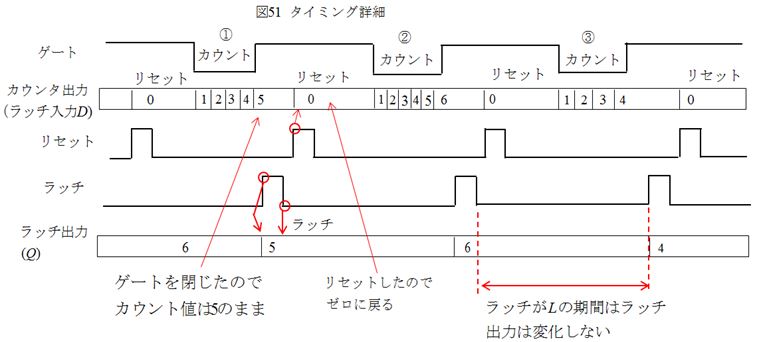

ゲート、ラッチ、リセットおおびカウンタ値がどのようになっているか分かりにくいと思いますので図51で説明します。

説明が簡単になるように最下位桁のみとし、5または6あたりのカウント値を表示するものと思って下さい。

まず、ゲートはLでオープンし、この期間にカウントされます。

①の期間では0、1、2、4,5までカウントしています。

この5をカウントした直後にゲートが閉じて(H)、カウント値は5のままです。

その後ラッチ信号がHになり、この期間のラッチ出力は5です。

この例ではラッチ前のラッチ出力が6だったのでラッチ信号Hの開始ポイントで5に変化しています。

ラッチ信号がLになった後で今度はリセット信号がHになります。

カウンタ(74HC390)はこのHでリセットされてカウンタ出力はゼロになります。

この場合、74HC373のD入力値もゼロになりますが、すでにラッチ状態になっていますので、ラッチ出力は5のままです。

次のゲートがオープンする②の期間では0、1、2、3、4、5、6までカウントしました。

同様にゲートが閉じたことによって6でカウント値が止まったままです。

今度はラッチ信号のHでラッチ出力が5から6に変化し、その後ラッチされ、リセットとなる繰り返し動作です。

この例では最下位桁で説明しましたが、その他の桁もクロック入力が下位桁からのQDになるだけなので内部の動作は同じです。

ゲート時間1sと1msは時間が異なりますが、ラッチ、リセットの順序は同じですから、同じ動作をします。

また、更新周期はラッチ信号間の時間で、それぞれ2sおよび200msです。

◎デコーダと7SEG-LED

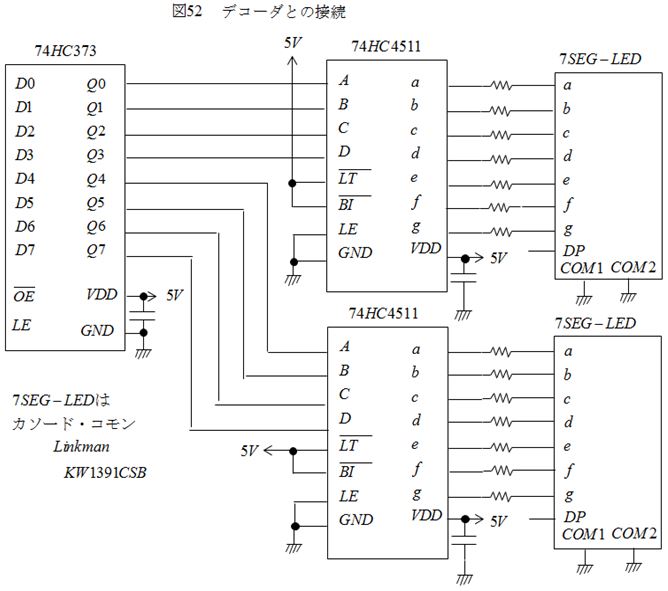

図52にラッチ(74HC373)を含めたデコーダと7SEG-LEDの接続を示します。

デコーダICは74HC4511です。

このICの詳細については資料・技術情報「アップダウンカウンタの製作 基礎編」を参照願います。

7SEG-LEDはカソード・コモンです。

電流制限抵抗の値は用いる7SEG-LEDで異なります。

4桁ありますのでかなりの消費電流になります。

なるべく最小限の電流値にしたほうが良いです。

ちなみに今回は7SEG-LEDにLinkmanのKW1391CSBを用い、制限抵抗は680Ωとしています。

7SEG-LEDのデシマルポイント(DP)は最上位桁以外は使用しません。

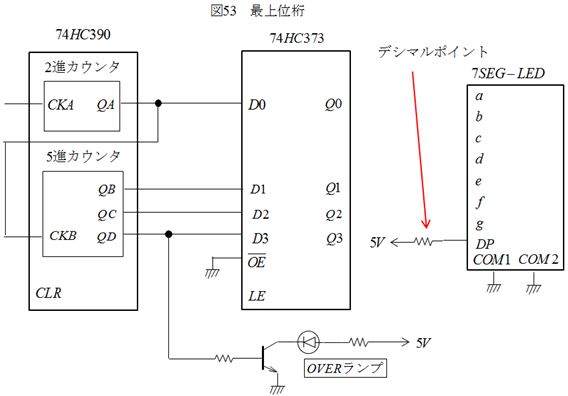

最上位桁のみ図53のように電流制限抵抗を介して電源へ接続します。

つまり、1s、1msのゲート時間によらず、常にデシマルポイントが点灯します。

また、最上位桁のカウンタ出力QDはトランジスタによるLEDスイッチング回路へ接続します。

QDはカウント値8以上でHになります。

つまり、表示が8XXX以上になったらカウントオーバーに近い状態またはカウントオーバーであることをLEDで知らせます。

QDから取ると図51のタイミング詳細のように一旦ゼロになりますのでLEDは点滅動作します。

ちなみに、74HC373のQ出力から取れば点灯動作です。

ロジックICで構成した周波数カウンタの製作 【測定原理と仕様検討編】はこちら

ロジックICで構成した周波数カウンタの製作 【設計編 その1】はこちら

ロジックICで構成した周波数カウンタの製作 【設計編 その2】はこちら

ロジックICで構成した周波数カウンタの製作 【設計編 その3】