# **HUMANDATA**.

Spartan-6 FPGA ボード (メモリ無し) XCM-110Z ユーザーズマニュアル Ver. 1.1

ヒューマンデータ

## 目 次

| <u> </u>                | I  |

|-------------------------|----|

| ● ご注意                   | 1  |

| ● 改訂記録                  | 2  |

| 1. 共通ピンについて【重要】         | 2  |

| 2. 開発環境                 | 3  |

| 3. 製品の内容について            | 3  |

| 4. 仕様                   | 4  |

| 5. 製品説明                 | 5  |

| 5.1. 各部名称               | 5  |

| 5.2. ブロック図              | 6  |

| 5.3. 電源                 |    |

| 5. 4. クロック              |    |

| 5.5. 設定スイッチ(SW3)        |    |

| 6. FPGA コンフィギュレーション     |    |

| 6.1. JTAG/バウンダリスキャン     |    |

| 6. 2. コンフィグ ROM ファイルの作成 |    |

| 6.3. コンフィグ ROM アクセス     | 9  |

| 7. FPGA ピン割付け表          | 10 |

| 7.1. ユーザ I/O (CNA)      | 10 |

| 7. 2. ユーザ I/O (CNB)     | 11 |

| 7.3. オンボードクロック          | 12 |

| 7.4. 外部クロック入力           | 12 |

| 7. 5. 汎用 LED            | 12 |

| 7.6. 汎用スイッチ             | 12 |

| 7.7. 共通ピン               | 12 |

| 8. サポートページ              | 13 |

| 9. 付属資料                 | 13 |

| 10 お問い合せについて            | 13 |

### ● はじめに

この度は Spartan-6 FPGA ボード XCM-110Z シリーズをお買い上げいただきまして、誠にありがとうございます。

XCM-110Z は、XILINX の高性能 FPGA Spartan-6 シリーズを用いた FPGA ボードで、電源回路、クロック回路、コンフィギュレーション回路などを装備した、使いやすいボードになっています。 XCM-110Z シリーズは、 XCM-110 シリーズから、 MRAM と DDR2 SDRAM を省いたものです。 どうぞご活用ください。

### ● ご注意

- 1 本製品には、民生用の一般電子部品が使用されています。 宇宙、航空、医療、原子力等、各種安全装置など人命、事故にかかわる 特別な品質、信頼性が要求される用途でのご使用はご遠慮ください。

- 2 水中、高湿度の場所での使用はご遠慮ください。

- 3 腐食性ガス、可燃性ガス等引火性のガスのあるところでの 使用はご遠慮ください。

- 4 基板表面に他の金属が接触した状態で電源を入れないでください。

- 5 定格を越える電源を加えないでください。

- 6 本書の内容は、改良のため将来予告なしに変更することがありますので、 ご了承願います。

- 7 本書の内容については万全を期して作成しましたが、万一誤りなど、お気 づきの点がございましたら、ご連絡をお願いいたします。

- 8 本製品の運用の結果につきましては、7. 項にかかわらず当社は責任を負いかねますので、ご了承願います。

- 9 本書に記載されている使用と異なる使用をされ、あるいは本書に記載されていない使用をされた場合の結果については、当社は責任を負いません。

- 10 本書および、回路図、サンプル回路などを無断で複写、引用、配布することはお断りいたします。

- 11 発煙や発火、異常な発熱があった場合はすぐに電源を切ってください。

- 12 ノイズの多い環境での動作は保障しかねますのでご了承ください。

- 13 静電気にご注意ください。

### ● 改訂記録

| 日付         | バージョン | 改訂内容                 |

|------------|-------|----------------------|

| 2011/02/28 | 1.0   | ・初版発行                |

| 2012/05/16 | 1. 1  | ・2 章「開発環境」についての記述を編集 |

|            |       | ・10 章「お問い合せについて」を追加  |

### 1. 共通ピンについて【重要】

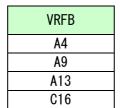

本ボードでは、下表の Vref ピンが共通になっています。

意図しないショートを避けるため、未使用ピンの設定を【Float】としておくことを推奨します。ISEでの未使用ピン処理設定の確認は下記をご参照ください。

| V09_REF |

|---------|

| K8      |

| Y1      |

| M4      |

| B3      |

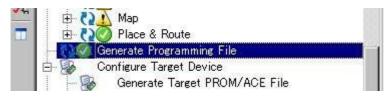

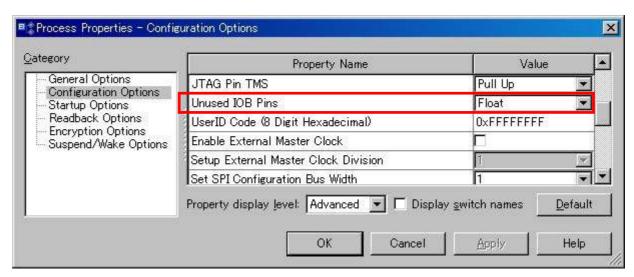

1. 【Generate Programming File】を右クリックして【Process Properties】を開きます

2. 【Configuration Options】内の【Unused IOB Pins】を確認します

### 2. 開発環境

FPGAの内部回路設計には、回路図エディタやHDL入力ツール、論理合成ツール等が必要です。 開発ツールの選択はユーザ様で行っていただくようお願いいたします。当社では開発ツール についてのサポートと搭載デバイスそのもののサポートは一切行っておりません。

本マニュアルは、マニュアル作成時に当社で使用している開発ツールを元に作成しています。

### 3. 製品の内容について

本パッケージには、以下のものが含まれています。万一、不足などがございましたら弊社宛にご連絡ください。

FPGA ボード XCM-110Z1付属品1マニュアル (本書)1 \*ユーザ登録はがき1 \*

\* オーダー毎に各1部の場合があります。(ご要望により追加請求できます)

## 4. 仕様

| 製品型番       | XCM-110Z-LX75                 | XCM-110Z-LX45         | XCM-110Z-LX100         | XCM-110Z-LX150         |  |

|------------|-------------------------------|-----------------------|------------------------|------------------------|--|

| 搭載 FPGA    | XC6SLX75<br>-2FGG484C         | XC6SLX45<br>-2FGG484C | XC6SLX100<br>-2FGG484C | XC6SLX150<br>-2FGG484C |  |

| コンフィグ ROM  | M25P32-VMF6                   | SP (32Mbit)           | M25P64-VMF6            | 6P (64Mbit)            |  |

| DDR2 SDRAM | 非搭載                           |                       |                        |                        |  |

| MRAM       | 非搭載                           |                       |                        |                        |  |

| オンボードクロック  | 50MHz、30MHz                   |                       |                        |                        |  |

| 外部クロック入力   | ユーザ 1/0 コネケ                   | クタ (CNA-11/12,        | CNB-11/12)             |                        |  |

| 電源         | DC 3.3[V]                     |                       |                        |                        |  |

| 消費電流       | N/A (詳細は FPGA データシートをご参照ください) |                       |                        |                        |  |

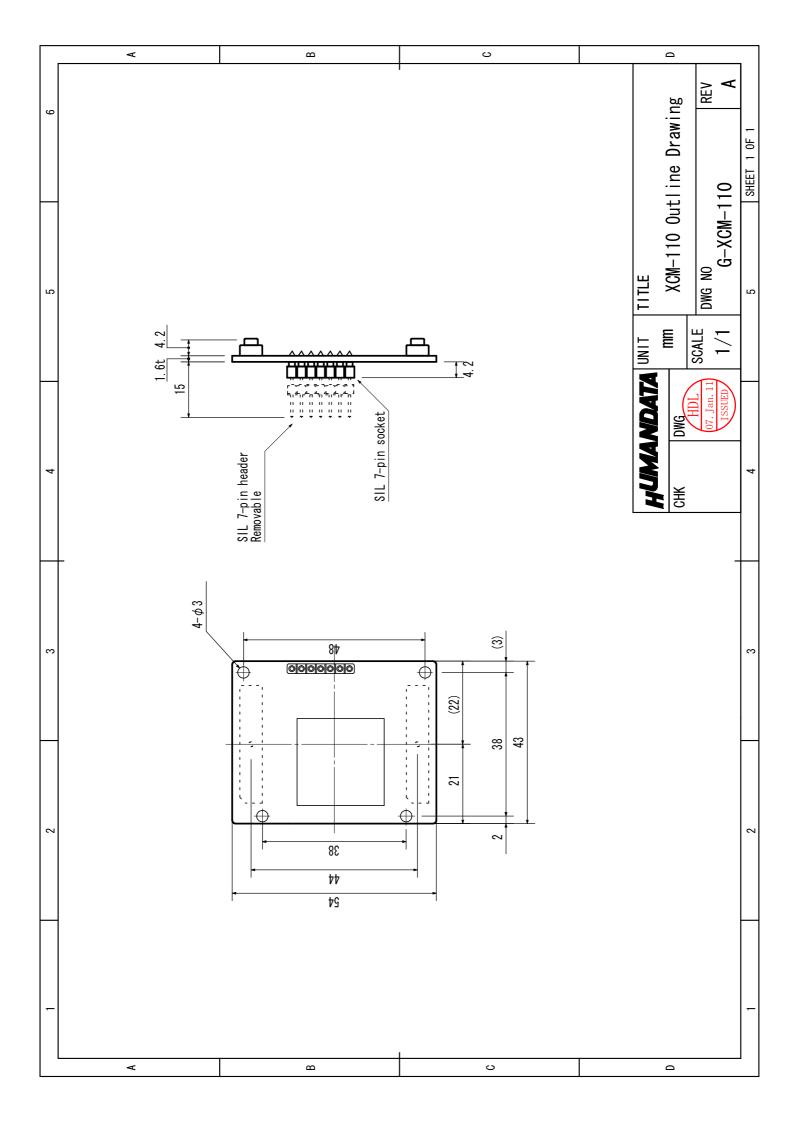

| 基板寸法       | 43 x 54 [mm]                  |                       |                        |                        |  |

| 質量         | 約 18 [g]                      |                       |                        |                        |  |

| ユーザ 1/0    | 128 本                         |                       |                        |                        |  |

| 汎用スイッチ     | 2 (Push x1, DIP x1bit)        |                       |                        |                        |  |

| 汎用 LED     | 2                             |                       |                        |                        |  |

| プリント基板     | ガラスエポキシ 8 層基板 1.6t            |                       |                        |                        |  |

| リセット信号     | コンフィグ用リセット信号(typ. 240ms)      |                       |                        |                        |  |

| JTAG コネクタ  | SIL7 ピンソケット 2.54mm ピッチ        |                       |                        |                        |  |

| ステータス LED  | POWER (赤), DONE (青)           |                       |                        |                        |  |

| 付属品        | SIL7 ピンヘッダ(本体に取付け済み)x1        |                       |                        |                        |  |

| 以局吅        | FX10A-80S/8-SV(               | 71) (ヒロセ電機)           | x2                     |                        |  |

4

#### \*これらの部品や仕様は変更となる場合がございます

## 5. 製品説明

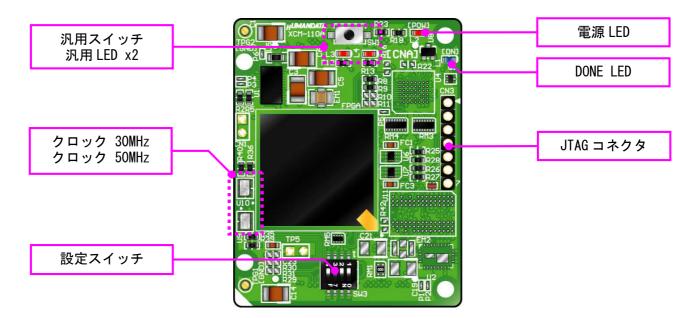

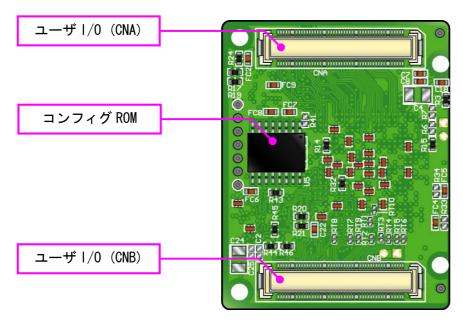

#### 5.1. 各部名称

部品面

はんだ面

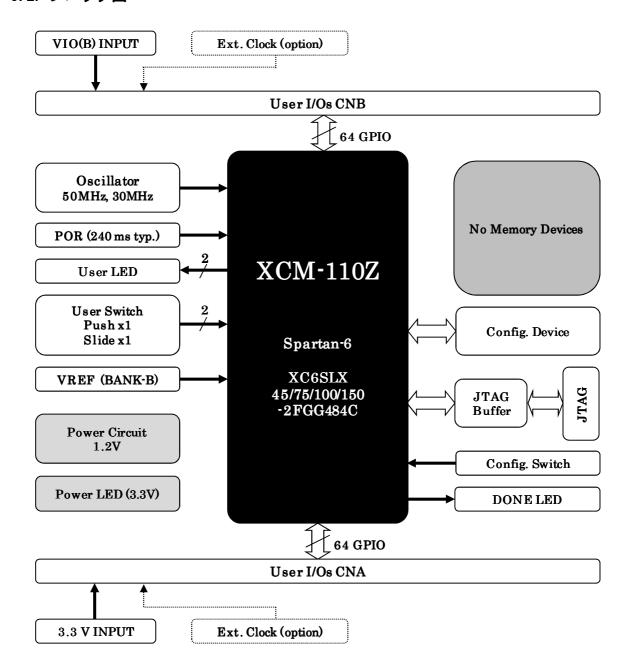

#### 5.2. ブロック図

#### 5.3. 電源

電源は CNA, CNB より 3.3V を供給してください。内部で必要になる 1.2V はオンボードレギュレータにより生成されます。

外部から供給する 3.3V 電源は充分安定して、充分な余裕のあるものをご用意ください。いずれも 3.3V を超えることはできません。

BANK Bの Vccio はボード上の 3.3V とは接続されていません。任意の値を CNB から入力してください。

詳しくは FPGA のデータシートや回路図などを参照してください。

#### 5.4. クロック

オンボードクロックとして 50MHz (U9) と 30MHz (U10) を搭載しています。CNA、CNB より外部クロックを入力することも可能です。

詳しくは回路図をご参照ください。

#### 5.5. 設定スイッチ(SW3)

設定スイッチによりコンフィギュレーションモードなどを変更することが可能です。各ピンの詳細についてはSpartan-6 コンフィギュレーションユーザガイドをご参照ください。

#### SW3

| 番号  | 4    | 3          | 2    | 1         |

|-----|------|------------|------|-----------|

| 記号  | ASWO | X_M1       | X_MO | X_HSWAPEN |

| 出荷時 | 0FF  | 0FF        | 0FF  | 0FF       |

| 説明  | 汎用   | コンフィグモード設定 |      | プルアップ設定   |

#### コンギュレーションモード

|             | X_M1 | X_MO |

|-------------|------|------|

| マスタシリアル/SPI | ON   | 0FF  |

| JTAG        | 0FF  | Х    |

ON: Low(0), OFF: High(1), X: Don't Care

#### ASWO

汎用用途としてご使用頂けます。

#### • X\_M1, X\_M0

コンフィギュレーションモードを設定します。

本来 JTAG モードにてご使用される場合の設定値は自由ですが、上記の設定値にてご使用になることを推奨致します。

#### X HSWAPEN

コンフィギュレーション前のユーザ 1/0 の状態を設定します。

ON : 内部プルアップ有り OFF : 内部プルアップ無し

### 6. FPGA コンフィギュレーション

JTAG コネクタ (CN3) よりバウンダリスキャンを行い、FPGA へのコンフィギュレーションやコンフィグ ROM のアクセスを行います。

コンフィグ ROM から FPGA へのコンフィギュレーションは、マスタシリアル/SPI モード設定時に電源投入にて自動的に行われます。十分に検査した安全性のあるデータを書き込むようにしてください。

JTAG コネクタのピン配置は下表のとおりです。ケーブル接続時は誤接続に注意してください。

| $\sim$ | N  | • |

|--------|----|---|

| U      | ١٧ | J |

| ピン番号 | 信号名       | 方向  |

|------|-----------|-----|

| 1    | GND       | I/O |

| 2    | TCK       | IN  |

| 3    | TDO       | OUT |

| 4    | TMS       | IN  |

| 5    | VCC(3.3V) | OUT |

| 6    | TDI       | IN  |

| 7    | GND       | I/O |

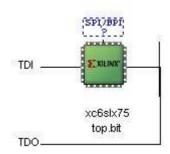

#### 6.1. JTAG/バウンダリスキャン

JTAG より FPGA を直接コンフィギュレーションするには、バウンダリスキャンにより認識されたデバイスに bit ファイルを割りつけてプログラムを実行します。

コンフィグ ROM を使用したコンフィギュレーションには下記を ご参照ください。

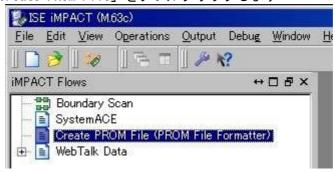

#### 6.2. コンフィグ ROM ファイルの作成

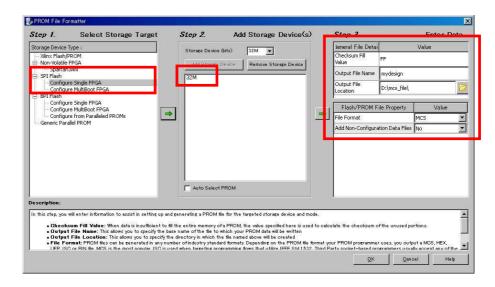

コンフィギュレーション ROM へ書き込むためには MCS ファイルが必要となります。書き込みたい bit ファイルから、iMPACT を使用して作成することができます。作成方法の一例を以下に示します。

(1) iMPACT にて「Create PROM File」をダブルクリックします

#### (2) 設定画面にて必要な項目を設定します

Storage Target: SPI Flash - Configure Single FPGA

● Storage Device: 32M または 64M (1つ)

● File Format: MCS ● その他項目:任意

- (3) 使用する bit ファイルを選択します

- (4) iMPACT Processes のタブにある「Generate File…」をダブルクリックします

- (5)「Generate Succeeded」と表記されれば完了です

#### 6.3. コンフィグ ROM アクセス

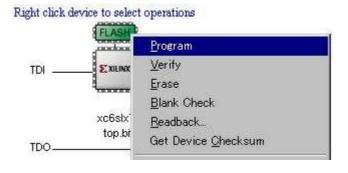

バウンダリスキャン画面にて、下図のようにコンフィグ ROM に MCS ファイルを割付けます。 デバイスには【SPI PROM - M25P32】または【SPI PROM - M25P64】を選択してください。 右クリックから各コマンドを実行できます。

コンフィギュレーションモードはマスタシリアル/SPI モードに設定してください。

## 7. FPGA ピン割付け表

### 7.1. ユーザ I/O (CNA)

| ネットラベル  | FPGA ピン   | CI     | NA     | FPGA ピン   | ネットラベル  |

|---------|-----------|--------|--------|-----------|---------|

| V33A    | 3.3V (IN) | 1, 3   | 2, 4   | 3.3V (IN) | V33A    |

| _       | Reserved  | 5, 7   | 6, 8   | Reserved  | -       |

| _       | N. C      | 9      | 10     | N. C      | -       |

| _       | GND       | _      | -      | GND       | -       |

| ECLK_AP | Y11       | 11     | 12     | AB11      | ECLK_AN |

| _       | N. C      | 13, 15 | 14, 16 | N. C      | -       |

| 10A0    | M21       | 17     | 18     | AB17      | 10A32   |

| I OA1   | M22       | 19     | 20     | Y17       | 10A33   |

| 10A2    | N22       | 21     | 22     | AB16      | 10A34   |

| 10A3    | N20       | 23     | 24     | AA16      | 10A35   |

| 10A4    | P22       | 25     | 26     | AB15      | 10A36   |

| 10A5    | P21       | 27     | 28     | Y15       | 10A37   |

| 10A6    | R22       | 29     | 30     | AB14      | 10A38   |

| -       | GND       | -      | -      | GND       | -       |

| 10A7    | T22       | 31     | 32     | AA14      | 10A39   |

| 10A8    | R20       | 33     | 34     | Y13       | 10A40   |

| 10A9    | T21       | 35     | 36     | AB12      | I0A41   |

| IOA10   | U20       | 37     | 38     | Y12       | 10A42   |

| IOA11   | U22       | 39     | 40     | AA12      | 10A43   |

| 10A12   | V21       | 41     | 42     | W11       | 10A44   |

| IOA13   | V22       | 43     | 44     | V11       | 10A45   |

| IOA14   | W22       | 45     | 46     | AA10      | 10A46   |

| 10A15   | W20       | 47     | 48     | AB10      | 10A47   |

| 10A16   | AB19      | 49     | 50     | Y9        | 10A48   |

| _       | GND       | -      | _      | GND       | _       |

| 10A17   | AA18      | 51     | 52     | AB9       | 10A49   |

| 10A18   | AB18      | 53     | 54     | AA8       | 10A50   |

| IOA19   | Y19       | 55     | 56     | AB8       | 10A51   |

| 10A20   | N19       | 57     | 58     | Y7        | 10A52   |

| 10A21   | U19       | 59     | 60     | AB7       | 10A53   |

| 10A22   | R19       | 61     | 62     | AB6       | 10A54   |

| 10A23   | P19       | 63     | 64     | AA6       | 10A55   |

| 10A24   | M19       | 65     | 66     | AB4       | 10A56   |

| 10A25   | P18       | 67     | 68     | AA4       | 10A57   |

| 10A26   | V15       | 69     | 70     | Y4        | 10A58   |

| _       | GND       | -      | -      | GND       | -       |

| 10A27   | P17       | 71     | 72     | W4        | 10A59   |

| 10A28   | M18       | 73     | 74     | AB3       | 10A60   |

| 10A29   | N16       | 75     | 76     | Y3        | 10A61   |

| 10A30   | M17       | 77     | 78     | AB2       | 10A62   |

| 10A31   | M16       | 79     | 80     | AA2       | 10A63   |

<sup>(\*)</sup>配線長は Web サポートページよりピン割付表ファイルをご参照ください

### 7.2. ユーザ I/O (CNB)

| ネットラベル  | FPGA ピン     | CI     | NB     | FPGA ピン     | ネットラベル  |

|---------|-------------|--------|--------|-------------|---------|

| V10 (B) | VIO(B) (IN) | 1, 3   | 2, 4   | VIO(B) (IN) | V10 (B) |

| _       | Reserved    | 5, 7   | 6, 8   | Reserved    | _       |

| _       | N. C        | 9      | 10     | N. C        | _       |

| _       | GND         | =      | -      | GND         | _       |

| ECLK_BP | D11         | 11     | 12     | C12         | ECLK_BN |

| _       | N. C        | 13, 15 | 14, 16 | N. C        |         |

| 10B0    | A18         | 17     | 18     | C22         | 10B32   |

| I 0B1   | B18         | 19     | 20     | B22         | 10B33   |

| 10B2    | A17         | 21     | 22     | B21         | 10B34   |

| 10B3    | C17         | 23     | 24     | A21         | 10B35   |

| 10B4    | A16         | 25     | 26     | C20         | 10B36   |

| 10B5    | B16         | 27     | 28     | A20         | 10B37   |

| 10B6    | A15         | 29     | 30     | K19         | 10B38   |

| _       | GND         | -      | -      | GND         | -       |

| 10B7    | C15         | 31     | 32     | K18         | 10B39   |

| 10B8    | A14         | 33     | 34     | J20         | 10B40   |

| 10B9    | B14         | 35     | 36     | K17         | 10B41   |

| I0B10   | C14         | 37     | 38     | K16         | 10B42   |

| I0B11   | D14         | 39     | 40     | H21         | 10B43   |

| 10B12   | A11         | 41     | 42     | J17         | 10B44   |

| I0B13   | C11         | 43     | 44     | G19         | 10B45   |

| I0B14   | A10         | 45     | 46     | E22         | 10B46   |

| 10B15   | B10         | 47     | 48     | D22         | 10B47   |

| I0B16   | <b>A</b> 8  | 49     | 50     | F21         | 10B48   |

| _       | GND         | -      | _      | GND         | _       |

| I 0B17  | B8          | 51     | 52     | D21         | 10B49   |

| I 0B18  | C10         | 53     | 54     | E20         | 10B50   |

| I 0B19  | D10         | 55     | 56     | C19         | 10B51   |

| 10B20   | D9          | 57     | 58     | D20         | 10B52   |

| I 0B21  | C8          | 59     | 60     | D19         | 10B53   |

| 10B22   | A7          | 61     | 62     | F20         | 10B54   |

| 10B23   | C7          | 63     | 64     | F19         | 10B55   |

| 10B24   | D7          | 65     | 66     | F18         | 10B56   |

| 10B25   | D8          | 67     | 68     | F17         | 10B57   |

| 10B26   | A6          | 69     | 70     | H19         | 10B58   |

| _       | GND         | -      | -      | GND         | -       |

| 10B27   | B6          | 71     | 72     | F16         | 10B59   |

| 10B28   | <b>A</b> 5  | 73     | 74     | G16         | 10B60   |

| 10B29   | C5          | 75     | 76     | H18         | 10B61   |

| 10B30   | C6          | 77     | 78     | G17         | 10B62   |

| 10B31   | D6          | 79     | 80     | J16         | 10B63   |

<sup>(\*)</sup> 配線長は Web サポートページよりピン割付表ファイルをご参照ください

### 7.3. オンボードクロック

| 周波数      | NET LABEL | FPGA Pin |

|----------|-----------|----------|

| 30MHz    | GCLK_30A  | H22      |

| JOINI 12 | GCLK_30B  | W12      |

| 50MHz    | GCLK_50A  | K20      |

| JUNITZ   | GCLK_50B  | AB13     |

### 7.4. 外部クロック入力

| コネクタ   | NET LABEL | FPGA Pin |

|--------|-----------|----------|

| CNA_11 | ECLK_AP   | Y11      |

| CNA_12 | ECLK_AN   | AB11     |

| CNB_11 | ECLK_BP   | D11      |

| CNB_12 | ECLK_BN   | C12      |

#### 7.5. 汎用 LED

| LED | NET LABEL | FPGA Pin |

|-----|-----------|----------|

| L4  | ULED4     | L20      |

| L3  | ULED3     | L22      |

### 7.6. 汎用スイッチ

| SW     | NET LABEL | FPGA Pin |

|--------|-----------|----------|

| SW1    | PSW0      | K21      |

| SW3[4] | ASW0      | K22      |

### 7.7. 共通ピン

下記の汎用ポートは、VREF機能を兼ねているため共通となっています。 出力ポートとして使用しないようにご注意ください。詳しくは1章をご参照ください。

12

| VRFB       |  |

|------------|--|

| A4         |  |

| <b>A</b> 9 |  |

| A13        |  |

| C16        |  |

| V09_REF |

|---------|

| K8      |

| Y1      |

| M4      |

| B3      |

### 8. サポートページ

改訂資料やその他参考資料は、必要に応じて各製品の資料ページに公開致します。

http://www.hdl.co.jp/ftpdata/xcm-110Z/index.html http://www.hdl.co.jp/support\_c.html

- 回路図

- ピン割付表

- 外形図

- ネットリスト

...等

また下記サポートページも合わせてご活用ください。

http://www.hdl.co.jp/spc/

### 9. 付属資料

- 1. 基板外形図 (XCM-110 と共通)

- 2. 基板回路図(別紙)

### 10. お問い合せについて

お問い合せ時は、製品型番とシリアル番号を添えて下さるようお願い致します。

e-mail の場合は、SPC2@hdl.co.jp へご連絡ください。 または、当社ホームページに設置のお問い合せフォームからお問い合せください。 技術的な内容にお電話でご対応するのは困難な場合がございます。可能な限りメール などをご利用くださるようご協力をお願いいたします。

#### おことわり

当社では、開発ツールの使用方法や FPGA などのデバイスそのものについて、サポート外とさせいただいております。あらかじめご了承下さいませ。

## Spartan-6 FPGA ボード (メモリ無し) XCM-110Z シリーズ ユーザーズマニュアル

2011/02/28 Ver. 1. 0 (初版)

2012/05/16 Ver.1.1

### 有限会社ヒューマンデータ

〒567-0034 大阪府茨木市中穂積1-2-10 ジブラルタ生命茨木ビル

TEL: 072-620-2002 FAX: 072-620-2003

URL : http://www.hdl.co.jp/