# MIXIM

### +2.7V、低電力、 12ビットシリアルADC、8ピンSOP

#### 概要

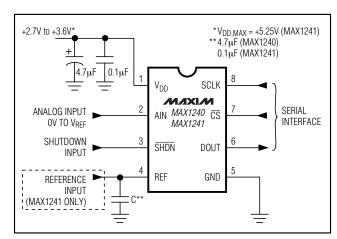

MAX1240/MAX1241は、8ピンパッケージに収められた 低電力、12ビットアナログディジタルコンバータ(ADC) です。MAX1240は単一+2.7V~+3.6V電源で動作し、 MAX1241は単一+2.7V~+5.25V電源で動作します。 どちらのICも7.5µsの逐次比較ADC、高速トラック/ホー ルド(1.5µs)、クロック及び高速3線シリアルインタ フェースを備えています。

電力消費は、73kspsの最大サンプリング速度で僅か  $37mW (V_{DD} = 3V)$ となっています。 $2\mu A$ シャットダウン モードにより、低スループットレート時の電力節減を 実現しています。

MAX1240は2.5Vリファレンスを内蔵し、MAX1241 は外部リファレンスを必要とします。MAX1241は、 0V~VRFFの信号を受け付け、リファレンス入力範囲は 正電源電圧が含まれます。外部クロックが、3線インタ フェースからデータをアクセスします。このインタ フェースは、標準マイクロコントローラI/Oポートに直 接接続しており、SPI™、QSPI™及びMICROWIRE™と コンパチブルです。

本製品は、優れたAC特性及び超低電力特性に加えて、 使いやすくパッケージが小型のため、リモートセンサ 及びデータ収集アプリケーション、あるいはその他の 省電力、小型化が必要な回路に最適です。MAX1240/ MAX1241は、8ピンDIP及びSOPパッケージで提供さ れています。

#### アプリケーション

バッテリ駆動機器

ポータブルデータロギング

絶縁データ収集

プロセス制御監視

計測器

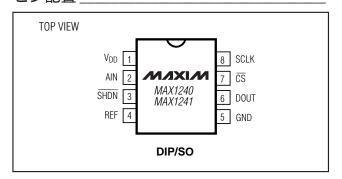

#### ピン配置

#### 特長

◆ 電源: +2.7V~+3.6V単一(MAX1240) +2.7V~+5.25V単一(MAX1241)

◆ 分解能:12ビット

◆ 2.5Vリファレンス内蔵(MAX1240)

◆ 小型パッケージ:8ピンDIP及びSOP

◆ 低電力: 3.7µW(73ksps、MAX1240) 3mW (73ksps, MAX1241) 66µW (1ksps, MAX1241) 5μW (パワーダウンモード)

◆ 内部トラック/ホールド

◆ 3線シリアルインタフェース: SPI/QSPI/MICROWIRE

◆ 内部クロック

#### 型番

| PART        | TEMP. RANGE  | PIN-          | INL   |  |

|-------------|--------------|---------------|-------|--|

|             |              | PACKAGE       | (LSB) |  |

| MAX1240ACPA | 0°C to +70°C | 8 Plastic DIP | ±1/2  |  |

| MAX1240BCPA | 0°C to +70°C | 8 Plastic DIP | ±1    |  |

| MAX1240CCPA | 0°C to +70°C | 8 Plastic DIP | ±1    |  |

| MAX1240ACSA | 0°C to +70°C | 8 SO          | ±1/2  |  |

| MAX1240BCSA | 0°C to +70°C | 8 SO          | ±1    |  |

| MAX1240CCSA | 0°C to +70°C | 8 SO          | ±1    |  |

| MAX1240BC/D | 0°C to +70°C | Dice*         | ±1    |  |

#### Ordering Information continued at end of data sheet.

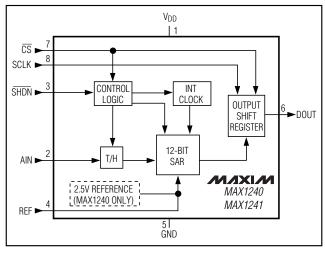

### ファンクションダイアグラム

SPI及びQSPIはMotorola,Inc.の商標です。MICROWIREはNational Semiconductor Corp.の商標です。

<sup>\*</sup>Dice are specified at  $T_A = +25$ °C, DC parameters only.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND                    | 0.3V to +6V               |

|-------------------------------------------|---------------------------|

| AIN to GND                                | 0.3V to $(V_{DD} + 0.3V)$ |

| REF to GND                                | 0.3V to $(V_{DD} + 0.3V)$ |

| Digital Inputs to GND                     | 0.3V to +6V               |

| DOUT to GND                               | 0.3V to $(V_{DD} + 0.3V)$ |

| DOUT Current                              | ±25mA                     |

| Continuous Power Dissipation ( $T_A = +1$ | 70°C)                     |

| Plastic DIP (derate 9.09mW/°C abov        | re +70°C)727mW            |

| SO (derate 5.88mW/°C above +70°C          | C)471mW                   |

| CERDIP (derate 8.00mW/°C above -          | +70°C)640mW               |

| Operating Temperature Ranges        |                |

|-------------------------------------|----------------|

| MAX1240_C_A/MAX1241_C_A             | 0°C to +70°C   |

| MAX1240_E_ A/MAX1241_E_ A           | 40°C to +85°C  |

| MAX1240_MJA/MAX1241_MJA             | 55°C to +125°C |

| Storage Temperature Range           |                |

| Lead Temperature (soldering, 10sec) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7V \text{ to } +3.6V \text{ (MAX1240)}; V_{DD} = +2.7V \text{ to } +5.25V \text{ (MAX1241)}; 73 \text{ksps, } f_{SCLK} = 2.1 \text{MHz} (50\% \text{ duty cycle}); MAX1240—4.7 \mu F capacitor at REF pin, MAX1241—external reference; <math>V_{REF} = 2.500V$  applied to REF pin;  $T_{A} = T_{MIN}$  to  $T_{MAX}$ ; unless otherwise noted.)

| PARAMETER                    | SYMBOL      | CONDITIONS                   |                                       | MIN  | TYP   | MAX              | UNITS  |  |

|------------------------------|-------------|------------------------------|---------------------------------------|------|-------|------------------|--------|--|

| DC ACCURACY (Note 1)         | 1           |                              |                                       |      |       |                  | _1     |  |

| Resolution                   |             |                              |                                       | 12   |       |                  | Bits   |  |

| Polativa Apauraay (Note 2)   | INL         | MAX124_A                     |                                       |      |       | ±0.5             | LSB    |  |

| Relative Accuracy (Note 2)   | IINL        | MAX124_B/C                   |                                       |      | ±1.0  | LOD              |        |  |

| Differential Nonlinearity    | DNL         | No missing codes ove         | r temperature                         |      |       | ±1               | LSB    |  |

| Offset Error                 |             | MAX124_A                     |                                       |      | ±0.5  | ±3.0             | LSB    |  |

| Oliset Elloi                 |             | MAX124_B/C                   |                                       |      | ±0.5  | ±4.0             | ] LSB  |  |

| Gain Error (Note 3)          |             |                              |                                       |      | ±0.5  | ±4.0             | LSB    |  |

| Gain Temperature Coefficient |             |                              |                                       |      | ±0.25 |                  | ppm/°C |  |

| DYNAMIC SPECIFICATIONS (1    | 0kHz sine-w | ave input, 0V to 2.500Vp     | o-p, 73ksps, f <sub>SCLK</sub> = 2.1N | 1Hz) |       |                  | -      |  |

| Signal-to-Noise Plus         | SINAD       | MAX124_A/B                   |                                       | 70   |       |                  | dB     |  |

| Distortion Ratio             | SINAD       | MAX124_C                     |                                       |      | 71.5  |                  | ] UB   |  |

| Total Harmonic Distortion    | THD         | I I In to the 5th harmonic — | MAX124_A/B                            |      |       | -80              | dB     |  |

| Total Harmonic Distortion    |             |                              | MAX124_C                              |      | -88   |                  |        |  |

| Spurious-Free Dynamic Range  | SFDR        | MAX124_A/B                   |                                       | 80   |       |                  | - dB   |  |

| Spurious-i ree Dynamic Hange | JI DIT      | MAX124_C                     |                                       |      | 88    |                  | ] "    |  |

| Small-Signal Bandwidth       |             | -3dB rolloff                 |                                       |      | 2.25  |                  | MHz    |  |

| Full-Power Bandwidth         |             |                              |                                       |      | 1.0   |                  | MHz    |  |

| CONVERSION RATE              | •           |                              |                                       |      |       |                  |        |  |

| Conversion Time              | tconv       |                              |                                       | 5.5  |       | 7.5              | μs     |  |

| Track/Hold Acquisition Time  | tacq        |                              |                                       |      |       | 1.5              | μs     |  |

| Throughput Rate              |             | f <sub>SCLK</sub> = 2.1MHz   |                                       |      |       | 73               | ksps   |  |

| Aperture Delay               | tapr        | Figure 8                     |                                       |      | 30    |                  | ns     |  |

| Aperture Jitter              |             |                              |                                       |      | <50   |                  | ps     |  |

| ANALOG INPUT                 | •           |                              |                                       |      |       |                  | -      |  |

| Input Voltage Range          |             |                              |                                       | 0    |       | V <sub>REF</sub> | V      |  |

| Input Capacitance            |             |                              |                                       |      | 16    |                  | pF     |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7 \text{V to } +3.6 \text{V (MAX1240}); V_{DD} = +2.7 \text{V to } +5.25 \text{V (MAX1241)}; 73 \text{ksps, } f_{SCLK} = 2.1 \text{MHz (50\% duty cycle)}; MAX1240—4.7 \mu F$  capacitor at REF pin, MAX1241—external reference;  $V_{REF} = 2.500 \text{V}$  applied to REF pin;  $T_{A} = T_{MIN}$  to  $T_{MAX}$ ; unless otherwise noted.)

| PARAMETER                                               | SYMBOL            | CONDITIONS                              | MIN                   | TYP                | MAX                       | UNITS   |  |

|---------------------------------------------------------|-------------------|-----------------------------------------|-----------------------|--------------------|---------------------------|---------|--|

| INTERNAL REFERENCE (MAX1                                | 240 only)         |                                         | l                     |                    |                           |         |  |

| REF Output Voltage                                      |                   | T <sub>A</sub> = +25°C                  | 2.480                 | 2.500              | 2.520                     | V       |  |

| REF Short-Circuit Current                               |                   |                                         |                       |                    | 30                        | mA      |  |

|                                                         |                   | MAX1240AC/BC                            |                       | ±30                | ±50                       |         |  |

| REF Temperature Coefficient                             |                   | MAX1240AE/BE                            |                       | ±30                | ±60                       | 2000/00 |  |

| NEF Temperature Coefficient                             |                   | MAX1240AM/BM                            |                       | ±30                | ±80                       | ppm/°C  |  |

|                                                         |                   | MAX1240C                                |                       | ±30                |                           | 1       |  |

| Load Regulation (Note 4)                                |                   | 0mA to 0.2mA output load                |                       | 0.35               |                           |         |  |

| Capacitive Bypass at REF                                |                   |                                         | 4.7                   |                    |                           | μF      |  |

| EXTERNAL REFERENCE (V <sub>REF</sub>                    | = 2.500V)         |                                         | •                     |                    |                           |         |  |

| Input Voltage Range                                     |                   |                                         | 1.00                  |                    | V <sub>DD</sub> +<br>50mV | V       |  |

| Input Current                                           |                   |                                         |                       | 100                | 150                       | μΑ      |  |

| Input Resistance                                        |                   |                                         | 18                    | 25                 |                           | kΩ      |  |

| REF Input Current in Shutdown                           |                   | SHDN = 0V                               |                       | ±0.01              | 10                        | μΑ      |  |

| Capacitive Bypass at REF                                |                   |                                         | 0.1                   |                    |                           | μF      |  |

| DIGITAL INPUTS: SCLK, $\overline{CS}$ , $\overline{SI}$ | HDN               |                                         |                       |                    |                           |         |  |

| SCLK, CS Input High Voltage                             |                   | V <sub>DD</sub> ≤ 3.6V                  | 2.0                   |                    |                           |         |  |

|                                                         | VIH               | V <sub>DD</sub> > 3.6V (MAX1241)        | 3.0                   |                    |                           | V       |  |

| SCLK, CS Input Low Voltage                              | VIL               |                                         |                       |                    | 0.8                       | V       |  |

| SCLK, CS Input Hysteresis                               | V <sub>HYST</sub> |                                         |                       | 0.2                |                           | V       |  |

| SCLK, CS Input Leakage                                  | I <sub>IN</sub>   | V <sub>IN</sub> = 0V or V <sub>DD</sub> |                       | ±0.01              | ±1                        | μΑ      |  |

| SCLK, CS Input Capacitance                              | CIN               | (Note 5)                                |                       |                    | 15                        | pF      |  |

| SHDN Input High Voltage                                 | VsH               |                                         | V <sub>DD</sub> - 0.4 |                    |                           | V       |  |

| SHDN Input Low Voltage                                  | V <sub>SL</sub>   |                                         |                       |                    | 0.4                       | V       |  |

| SHDN Input Current                                      |                   | SHDN = 0V or V <sub>DD</sub>            |                       |                    | ±4.0                      | μΑ      |  |

| SHDN Input Mid Voltage                                  | V <sub>SM</sub>   |                                         | 1.1                   | 1                  | V <sub>DD</sub> - 1.1     | V       |  |

| SHDN Voltage, Floating                                  | VFLT              | SHDN = float                            |                       | V <sub>DD</sub> /2 |                           | V       |  |

| SHDN Max Allowed Leakage,<br>Mid Input                  |                   | SHDN = float                            |                       |                    | ±100                      | nA      |  |

| DIGITAL OUTPUT: DOUT                                    | 1                 | 1                                       | I                     |                    |                           | 1       |  |

| Output Voltage Law                                      | \/-:              | I <sub>SINK</sub> = 5mA                 |                       |                    | 0.4                       | \/      |  |

| Output Voltage Low                                      | VoL               | ISINK = 16mA                            |                       |                    | 0.8                       | V       |  |

| Output Voltage High                                     | VoH               | ISOURCE = 0.5mA                         | V <sub>DD</sub> - 0.5 | )                  |                           | V       |  |

| Three-State Leakage Current                             | ΙL                | CS = V <sub>DD</sub>                    |                       | ±0.01              | ±10                       | μΑ      |  |

| Three-State Output Capacitance                          | Cout              | $\overline{CS} = V_{DD}$ (Note 5)       |                       |                    | 15                        | pF      |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7V \text{ to } +3.6V \text{ (MAX1240)}; V_{DD} = +2.7V \text{ to } +5.25V \text{ (MAX1241)}; 73 \text{ksps, } f_{SCLK} = 2.1 \text{MHz} (50\% \text{ duty cycle}); MAX1240—4.7 \mu F capacitor at REF pin, MAX1241—external reference; <math>V_{REF} = 2.500V$  applied to REF pin;  $T_{A} = T_{MIN}$  to  $T_{MAX}$ ; unless otherwise noted.)

| PARAMETERS         | SYMBOL          | CONDITIONS                  |            |                        | MIN | TYP  | MAX  | UNITS |

|--------------------|-----------------|-----------------------------|------------|------------------------|-----|------|------|-------|

| POWER REQUIREMENTS | '               |                             |            |                        | 11  |      |      |       |

| 0 1 1/1            | \/              | MAX1240                     |            |                        | 2.7 |      | 3.6  | V     |

| Supply Voltage     | V <sub>DD</sub> | MAX1241                     |            |                        | 2.7 |      | 5.25 | 7 v   |

|                    |                 |                             | MAX1240A/B | V <sub>DD</sub> = 3.6V |     | 1.4  | 2.0  | mA    |

|                    |                 | Operating mode              | MAX1240C   | 7 VDD = 3.6V           |     | 1.4  | 3.5  |       |

|                    |                 |                             | MAX1241A/B | V <sub>DD</sub> = 3.6V |     | 0.9  | 1.5  |       |

| Cumply Current     | lee             |                             |            | $V_{DD} = 5.25V$       |     | 1.6  | 2.5  |       |

| Supply Current     | IDD             |                             | MAX1241C   | V <sub>DD</sub> = 3.6V |     | 0.9  | 2.8  |       |

|                    |                 |                             |            | $V_{DD} = 5.25V$       |     | 1.6  | 3.8  |       |

|                    |                 | 1 ovor down, digital inpute |            | $V_{DD} = 3.6V$        |     | 1.9  | 10   |       |

|                    |                 |                             |            | $V_{DD} = 5.25V$       |     | 3.5  | 15   | - μΑ  |

| Supply Rejection   | PSR             | (Note 5)                    |            |                        |     | ±0.3 |      | mV    |

#### **TIMING CHARACTERISTICS** (Figure 8)

$(V_{DD} = +2.7 \text{V to } +3.6 \text{V (MAX1240)}; V_{DD} = +2.7 \text{V to } +5.25 \text{V (MAX1241)}; T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETERS                      | SYMBOL          | CONDITIONS                         |           | MIN | TYP | MAX | UNITS |

|---------------------------------|-----------------|------------------------------------|-----------|-----|-----|-----|-------|

| Acquisition Time                | tACQ            | CS = V <sub>DD</sub> (Note 6)      |           | 1.5 |     |     | μs    |

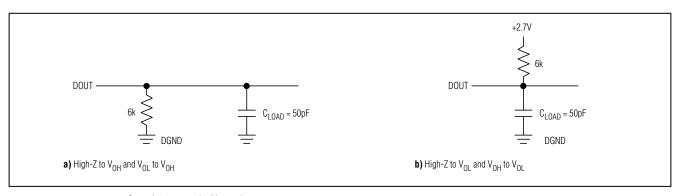

| SCLK Fall to Output Data Valid  | tno             | Figure 1,                          | MAX124C/E | 20  |     | 200 |       |

| SCLK Fall to Output Data Valid  | tDO             | C <sub>LOAD</sub> = 50pF           | MAX124M   | 20  |     | 240 | - ns  |

| CS Fall to Output Enable        | t <sub>DV</sub> | Figure 1, C <sub>LOAD</sub> = 50pF |           |     |     | 240 | ns    |

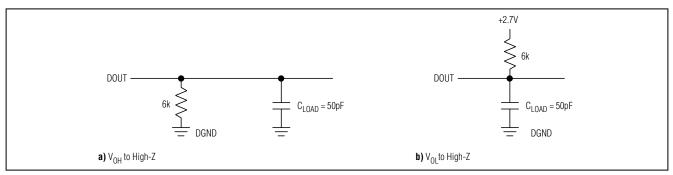

| CS Rise to Output Disable       | t <sub>TR</sub> | Figure 2, C <sub>LOAD</sub> = 50pF |           |     |     | 240 | ns    |

| SCLK Clock Frequency            | fsclk           |                                    |           | 0   |     | 2.1 | MHz   |

| SCLK Pulse Width High           | tch             |                                    |           | 200 |     |     | ns    |

| SCLK Pulse Width Low            | tCL             |                                    |           | 200 |     |     | ns    |

| SCLK Low to CS Fall Setup Time  | tcso            |                                    |           | 50  |     |     | ns    |

| DOUT Rise to SCLK Rise (Note 5) | tstr            |                                    |           | 0   |     |     | ns    |

| CS Pulse Width                  | tcs             |                                    |           | 240 |     |     | ns    |

- **Note 1:** Tested at  $V_{DD} = +2.7V$ .

- Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range and offset have been calibrated.

- Note 3: MAX1240—internal reference, offset nulled; MAX1241—external reference (V<sub>REF</sub> = +2.500V), offset nulled.

- Note 4: External load should not change during conversion for specified accuracy.

- Note 5: Guaranteed by design. Not subject to production testing.

- Note 6: Measured as [VFS(2.7V) VFS(VDD(MAX)].

- Note 7: To guarantee acquisition time, tACQ is the maximum time the device takes to acquire the signal, and is also the minimum time needed for the signal to be acquired.

#### 図1. DOUTイネーブル時間用の負荷回路

図2. DOUTディセーブル時間用の負荷回路

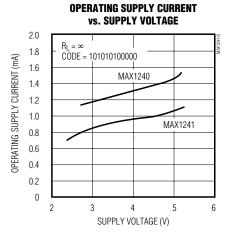

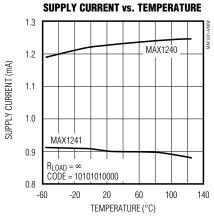

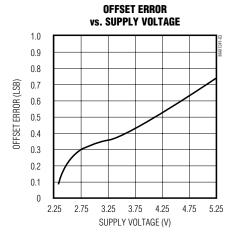

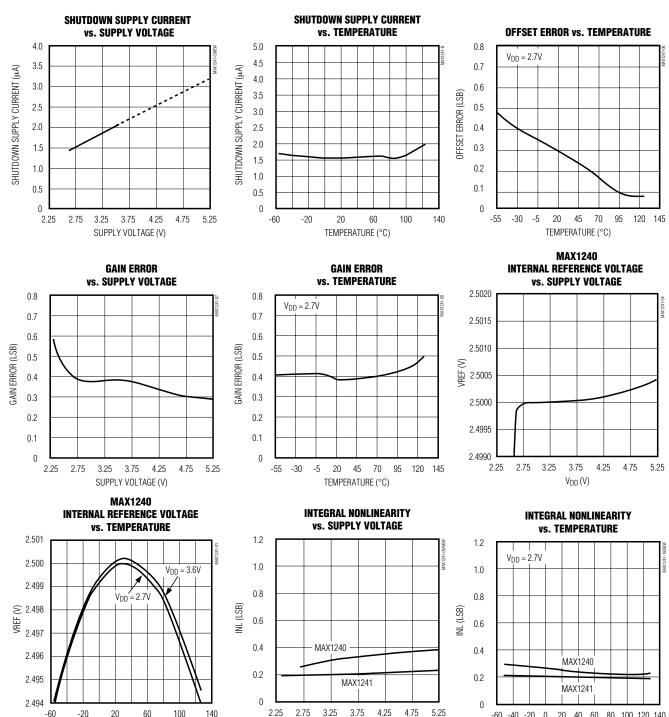

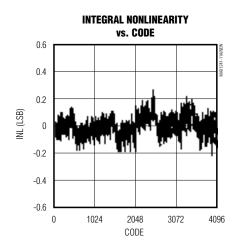

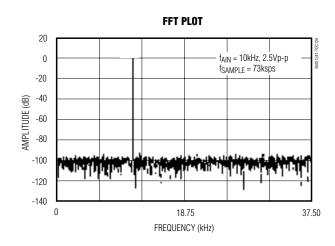

#### 標準動作特性

$(V_{DD} = 3.0V, V_{REF} = 2.5V, f_{SCLK} = 2.1MHz, C_{L} = 20pF, T_{A} = +25^{\circ}C, unless otherwise noted.)$

標準動作特性(続き)

$(V_{DD} = 3.0V, V_{REF} = 2.5V, f_{SCLK} = 2.1MHz, C_L = 20pF, T_A = +25^{\circ}C, unless otherwise noted.)$

2.25

3.25 3.75

SUPPLY VOLTAGE (V)

4.25

4.75 5.25 20 40 60 80 100 120 140

TEMPERATURE (°C)

-60 -40 -20 0

-60

-20

20

60

TEMPERATURE (°C)

100

### 標準動作特性(続き)\_

$(V_{DD} = 3.0V, REF = 2.5V, f_{SCLK} = 2.1MHz, C_L = 20pF, T_A = +25^{\circ}C, unless otherwise noted.)$

### 端子説明

| 端子 | 名称              | 機能                                                                                                                                                                                                                                                                                                              |

|----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | V <sub>DD</sub> | 正電源電圧:2.7V~3.6V(MAX1240);2.7V~5.25V(MAX1241)                                                                                                                                                                                                                                                                    |

| 2  | AIN             | サンプリングアナログ入力。範囲は0V~V <sub>REF</sub> 。                                                                                                                                                                                                                                                                           |

| 3  | SHDN            | $3$ レベルシャットダウン入力。 $\overline{SHDN}$ をローにすると、MAX1240/MAX1241は、消費電流15 $\mu$ A(max)までシャットダウンされます。 $\overline{SHDN}$ がハイ $\underline{V}$ はフローティングの場合、MAX1240とMAX1241は完全な動作状態になります。MAX1240の場合、 $\overline{SHDN}$ をハイにすると、内部リファレンスはイネーブルになります。また、 $\overline{SHDN}$ をフローティングにすると、内部リファレンスはディセーブルされ、外部電圧リファレンスを使用できます。 |

| 4  | REF             | A/D変換用のリファレンス電圧。MAX1240の場合、内部2.5V電圧リファレンス出力となり、4.7μF容量のコン<br>デンサでバイパスします。MAX1241又は内部リファレンスがディセーブルのMAX1240の場合には、外部リファ<br>レンス電圧入力となります。外部リファレンスを使用する際には、少なくとも0.1μFのコンデンサでバイパスします。                                                                                                                                 |

| 5  | GND             | アナログ及びディジタルグランド                                                                                                                                                                                                                                                                                                 |

| 6  | DOUT            | シリアルデータ出力。データの状態は、SCLKの立下がリエッジで変化します。CSがハイの時、ハイインピーダンスになります。                                                                                                                                                                                                                                                    |

| 7  | CS              | アクティブローのチップセレクトの立下がりエッジで変換が開始されます。CSがハイの時、DOUTは<br>ハイインピーダンスになります。                                                                                                                                                                                                                                              |

| 8  | SCLK            | シリアルクロック入力。SCLKにより、最大2.1MHzのレートでデータをクロックアウトします。                                                                                                                                                                                                                                                                 |

図3. 動作ダイアグラム

詳細

#### コンバータの動作

MAX1240/MAX1241は、入力トラック/ホールド(T/H)及び逐次比較レジスタ(SAR)を使用してアナログ入力信号をディジタル12ビット出力に変換します。T/Hには外部ホールドコンデンサは必要ありません。図3に、MAX1240/MAX1241の最もシンプルな構成を示します。MAX1240/MAX1241は、 $0V \sim V_{REF}$ の範囲の入力信号をT/Hアクイジション時間も含めて $9\mu$ sで変換します。MAX1240の内部リファレンスは2.5Vに設定されています。MAX1241は外部リファレンスを必要とします。どちらも $1.0V \sim V_{DD}$ の外部リファレンス電圧が必要です。シリアルインタフェースは僅か3本(SCLK、 $\overline{CS}$ 及びDOUT)のディジタルラインを必要とするだけで、マイクロプロセッサ( $\mu$ P)へのインタフェースを容易に実現できます。

MAX1240/MAX1241には、通常及びシャットダウンの2つの動作モードがあります。 $\overline{SHDN}$ をローに下げると素子がシャットダウンし、消費電流が10 $\mu$ A以下に低減します( $V_{DD}$  3.6V)。 $\overline{SHDN}$ を八イにするか、あるいはオープンのままだと、素子は通常動作モードになります。 $\overline{CS}$ をローにすると変換が開始されます。変換結果は、ユニポーラシリアルフォーマットでDOUTに出力されます。シリアルデータストリームは、変換完了(EOC)を示すハイビットの後にMSBを先頭ビットとするデータビットが続きます。

#### アナログ入力

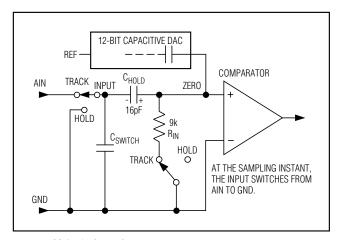

図4に、アナログディジタルコンバータ(ADC)のコンパレータのサンプリング構造を示します。フルスケール入力電圧は、REFの電圧で設定されます。

#### トラック/ホールド

トラックモードでは、アナログ信号は取り込まれて内 部ホールドコンデンサに蓄積されます。ホールドモード

図4. 等価入力回路

ではT/Hスイッチが開き、ADCのSAR部分の入力を一定に維持します。

アクイジション中は、アナログ入力(AIN)がコンデンサ $C_{HOLD}$ を充電します。 $\overline{CS}$ をローにするとアクイジション期間が終了します。この瞬間に、T/Hスイッチが $C_{HOLD}$ の入力側をGNDに切り換えます。 $C_{HOLD}$ に保持されている電荷が入力のサンプルを表し、コンパレータの入力のノードZEROを不平衡にします。

ホールドモードでは、容量性ディジタルアナログコンバータ(DAC)が、変換サイクルの残余時間内に、容量性DACがノードZEROを12ビット分解能の限界内で、0Vに調節します。この動作は、電荷をC<sub>HOLD</sub>からバイナリ重み付の容量性DACに移すのと等価であり、この結果、アナログ入力信号のディジタル表現が生成されます。変換の最後ではC<sub>HOLD</sub>の入力側がAINに再び切り換えられ、C<sub>HOLD</sub>は再び入力信号まで充電されます。

T/Hが入力信号を取り込むのに要する時間は、入力容量が充電される速さの関数です。入力信号のソースインピーダンスが高いと、アクイジション時間が長くなるため、変換と変換の間の間隔を長くする必要があります。アクイジション時間(t<sub>ACQ</sub>)は素子が信号を取込むのに要する最大時間であり、信号の取込みに必要な最小時間です。アクイジション時間は、次式で計算されます。

$$t_{ACO} = 9 (R_S + R_{IN}) \times 16pF$$

ここで、 $R_{IN}=9k$  、 $R_S=$  入力信号のソースインピーダンス、そして $t_{ACQ}$ は必ず1.5 $\mu$ s以上とします。ソースインピーダンスが1k 以下であれば、ADCのAC性能に大きな影響はありません。

アナログ入力に0.01µFのコンデンサを接続すると、これより高いソースインピーダンスも可能になります。 入力コンデンサと入力ソースインピーダンスによって RCフィルタが形成されるため、ADCの信号帯域幅が制限されることに注意してください。

#### 入力帯域幅

ADCの入力トラッキング回路の小信号帯域幅は2.25MHzであるため、アンダーサンプリング技法を使用することにより帯域幅がADCのサンプリングレートを超える周期信号を測定し、高速トランジェント現象を数値化できます。不要な高周波信号のエイリアシングが、目的の周波数帯域に入るのを防ぐため、アンチエイリアシングフィルタリングをお勧めします。

#### アナログ入力保護

内部保護ダイオードによりアナログ入力が $V_{DD}$ とGNDにクランプされているため、チャネル入力ピンは(GND - 0.3V) ~ ( $V_{DD}$  + 0.3V)の範囲で、損傷を起こすことなくスイングできます。しかし、フルスケール付近で正確な変換を行うためには、入力が $V_{DD}$ を50mV以上超えず、またGNDを50mV以上下回らないようにしてください。

アナログ入力が電源を50mV以上超えた場合は、入力電流を2mAまでに制限してください。

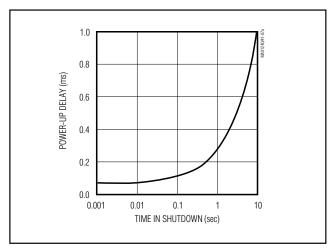

#### 内部電圧リファレンス(MAX1240)

MAX1240には2.5Vに調整されたの電圧リファレンスが内蔵されています。この内部リファレンス出力はREF出力ピンに接続され、内部容量性DACの駆動にも使用されます。この電圧出力を他の部品用のリファレンス電圧源として使用することが可能で、最大で400μAまでソースできます。REFピンは4.7μFのコンデンサでバイパスしてください。これよりも容量の高いコンデンサを使用すると、MAX1240がシャットダウンデンサを使用すると、MAX1240がシャットダウンモードからウェイクアップする時間が長くなってしまいます(「SHDN使用による消費電流の低減」の項を参照リファレンスが使用可能になります。このSHDN入力ピンをフローティング状態すると、内部リファレンスの項で説明すの動作が禁止され、「外部リファレンス」の項で説明す

るように、外部リファレンスを使用することが可能に なります。

#### 外部リファレンス

MAX1240/MAX1241は、REFピンで外部リファレンスを必要とします。仕様の精度を得るために、+1.0V~V<sub>DD</sub>の電圧範囲を超えないようにしてください。最小入力インピーダンスは、DC電流に対して18kです。MAX1240を外部リファレンスと使用する場合は、SHDNをフロートし、内部リファレンスをディセーブルにしてください。変換時のリファレンスは、最大250µAのDC負荷電流を供給できなければならず、出力インピーダンスは10以下でなければなりません。バイパスコンデンサの推奨最小値は、0.1µFです。リファレンスの出力インピーダンスがこれ以上の場合やノイズが多い場合は、4.7µFのコンデンサでREFピンの近くにバイパスしてください。

#### シリアルインタフェース

#### パワーアップ後の初期化及び変換開始

電源を最初に投入するとき、そしてSHDN入力がローでない場合には、完全に放電状態の4.7µF容量の電圧リファレンスバイパス用コンデンサを規定精度が保証されるまで十分に充電させるために、最高で20msまでの時間が必要です。 電源が安定化した後の内部リセット時間は10µsです。この期間は変換を実行しないでください。

変換は、CSをローにすることによって開始します。CSの立下がリエッジでT/Hはホールドモードに入り、変換が開始されます。内部で決められた変換期間が過ぎると、DOUTがハイになることにより変換の完了が表示されます。その後、データは、外部クロックによってシリアルにシフトアウトされます。

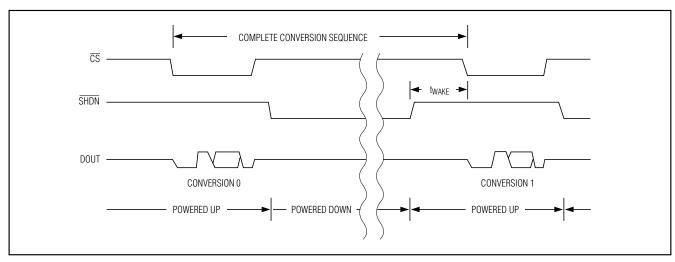

図5. シャットダウンシーケンス

#### SHDN使用による消費電流の低減

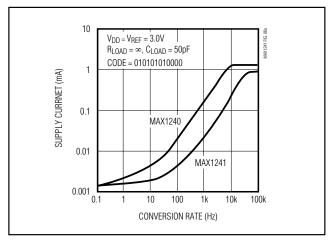

MAX1240/MAX1241を変換と変換の間でシャットダウンすることによって、消費電力を大幅に低減できます。これは図6の平均消費電流対変換レートのグラフに示されています。MAX1241では外部リファレンス電圧を使用するので(リファレンス電圧が連続的に出力されると仮定)、シャットダウン動作モードから短時間( $4\mu$ s)でウェイクアップします。したがって、平均的な消費電流がより低い値に抑えられます。ウェイクアップ時間( $t_{WAKE}$ )は、 $\overline{SHDN}$ が解除されてから変換を開始できるようになるまでの時間です(図5)。シャットダウン中、外部4.7 $\mu$ Fリファレンスバイパスコンデンサはゆっくりとチャージを失うため、MAX1240のウェイクアップ時間はシャットダウン時間に依存します(図7)。

#### 外部クロック

実際の変換には外部クロックは必要ありません。このため、変換結果はµPに合わせて2.1MHzまでの任意のクロックレートで読み取ることができます。各クロック位相が少なくとも200nsであれば、クロックのデューティサイクルには制限がありません。変換中には、クロックを動作させないでください。

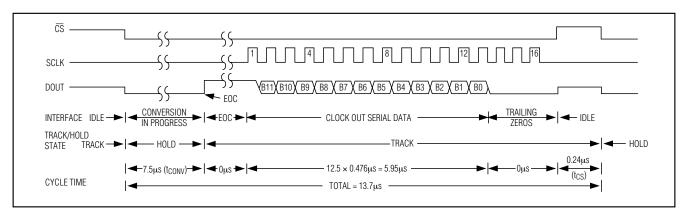

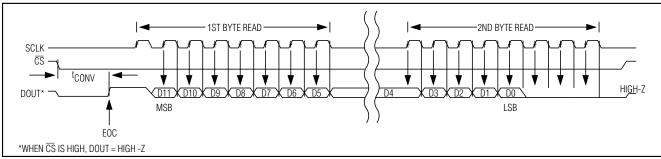

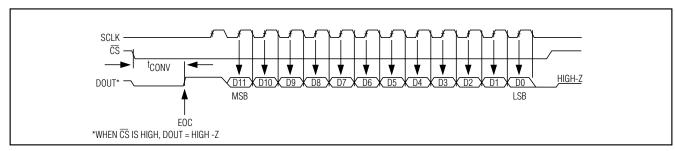

#### タイミングと制御

変換開始及びデータ読み取り動作は、CS及びSCLKディジタル入力によって制御されます。図8及び図9のタイミングダイアグラムにシリアルインタフェースの動作がまとめられています。

CSの立下がりエッジにより変換シーケンスが開始されます。T/H段により入力電圧が保持され、ADCが変換を開始し、DOUTがハイインピーダンスからロジックローに変わります。変換中は、SCLKをローに維持しておくことが必要です。変換の進行中は、内部レジスタによりデータが保存されます。

図6. 平均消費電流対変換レート

図7. リファレンスパワーアップ遅延対シャットダウン 時間(typ)

図8. インタフェース時間シーケンス

図9. シリアルインタフェースタイミングの詳細図

変換の完了(EOC)は、DOUTがハイになることによって判定できます。DOUTの立上がリエッジをフレーミング信号として使用できます。変換完了後、任意の時間にSCLKによって、データをこのレジスタからシフトアウトします。DOUTは、SCLKの立下がリエッジで遷移します。その次のクロックの立下がリエッジでその変換のMSBがDOUTに出力され、残りのビットがそれに続きます。データビットが12個、先頭のハイビットが1個存在するため、これらのビットをシフトアウトするには、少なくとも13個のクロック立下がリエッジが必要です。変換結果がクロックアウトされた後及びCSの立上がリエッジの前における余分のクロックパルスは、DOUTにゼロの列を生成するだけで、コンバータの動作には影響しません。

サイクル時間を最小にするためには、DOUTの立上がりエッジをEOC信号として使用します。データをフルスピードの12.5クロックサイクルでクロックアウトします。変換のLSB読込みの後に、CSをハイにします。仕様で指定された最小時間(t<sub>CS</sub>)の後、CSを再びローにして次の変換を開始できます。

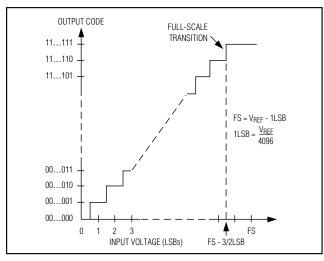

図10. ユニポーラ伝達関数(フルスケール(FS) = V<sub>RFF</sub>-1LSB、ゼロスケール(ZS) = GND)

#### 出力コーディング及び伝達関数

MAX1240/MAX1241のデータ出力は、バイナリです。 図10は、公称伝達関数を示しています。 コード遷移は、 隣接する整数LSB値同士の中間点で起こります。  $V_{REF}$  = +2.500Vである場合、1 LSB = 610 $\mu$ V (即ち2.500V/4096)です。

#### アプリケーション情報

#### 標準インタフェースへの接続

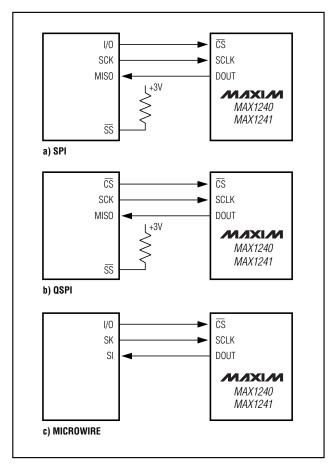

MAX1240/MAX1241は、SPI、QSPI及びMICROWIRE 標準シリアルインタフェースと完全にコンパチブルです (図11)。

シリアルインタフェースが使用できる場合は、CPUのシリアルインタフェースをマスターモードに設定し、CPUがシリアルクロックを発生できるようにしてください。選択できるクロック周波数は、2.1MHzまでとなっています。

- 1) CPUの汎用I/Oラインを使用して、CSをローにします。SCLKは、ローに維持します。

- 2) SCLKを作動させる前に、仕様で指定された最大変換時間待ちます。あるいは、DOUTの立上がリエッジで変換の完了を判定することもできます。

- 3) SCLKを少なくとも13クロックサイクル作動させます。最初の立下がりエッジでDOUT変換のMSBが生成されます。DOUTの出力データは、SCLKの立下がりエッジで遷移し、MSBを先頭にしたフォーマットで出てきます。SCLKからDOUTへの有効タイミング特性を守ってください。SCLKの立上がりエッジでデータをµPにクロックインできます。

- 4) 13番目の立下がリクロックエッジ以後にCSをハイにします。CSがローに留まると、LSBの後にゼロの列がクロックアウトされます。

5) CS = ハイの状態で、仕様で指定された最小時間t<sub>CS</sub> 待った後でCSをローにし、新しい変換を開始します。 変換が完了する前にCSをハイにして変換を中断した 場合は、新しい変換を開始する前に最小アクイジション時間t<sub>ACO</sub>待ちます。

CSは全てのデータビットがクロックアウトするまでローでなければなりません。図8に示すように、データは2バイトずつ、又は連続的に出力できます。これらのバイトは、1の先頭ビットと後に続く0の列が付加された変換結果となります。

#### SPI及びMICROWIRE

SPI又はMICROWIREを使用する場合は、CPOL = 0及び CPHA = 0に設定してください。変換は、CSの立下がリエッジで開始されます。DOUTがローになって変換が進行中であることを知らせます。DOUTがハイになるか、あるいは仕様で指定された最大変換時間7.5μsが経過するまで待ってください。ADCから完全な12ビットを取り出すには、2つの連続した1バイト読取り動作が必要です。DOUTの出力データは、SCLKの立下がリエッジで遷移し、SCLKの立上がリエッジでμPにクロックインされます。

最初のバイトには、先頭ビットの1及び7ビットの変換結果が含まれます。2番目のバイトには、残りの5ビット及び後に続く3つのゼロが含まれます。接続については図11、タイミングについては図12を参照してください。

#### **QSPI**

CPOL = CPHA = 0に設定してください。SPIは、ADC から12ビットのデータを取り込むために2つの1バイト 読取り動作を必要としますが、QSPIではデータをクロック インするために必要なクロックサイクル数を最小限に 抑えられます。MAX1240/MAX1241は、12ビットの データ(後に続くゼロはなし)をクロックアウトするため に $\mu$ Pからのクロックを13サイクル分必要とします (図13)。QSPIとのコンパチビリティが保証される最大 クロック周波数は、2.097MHzです。

#### レイアウト、グランド及びバイパス

最高の性能を得るには、プリント回路基板を使用してください。ワイヤラップボードはお勧めできません。ボードレイアウトは、ディジタル信号ラインとアナログ信号ラインが分離されるようにします。アナログとディジタル(特にクロック)ラインを互いに並行に走らせないでください。又、ディジタルラインがADCパッケージの下に来ないようにしてください。

図11. MAX1241への一般的なシリアルインタ フェース接続

図14に、推奨されるシステムグランド接続法を示します。一点アナロググランド(スターグランドポイント)をGNDのところで設定し、ロジックグランドとは分離します。ノイズをさらに減らすために、その他全てのアナロググランド及びDGNDをスターグランドに接続してください。このグランドに他のディジタルシステムグランドを接続しないでください。ノイズを排除するためにスターグランドから電源へのグランドリターンはできるだけ短くし、また、低インピーダンスにしてください。

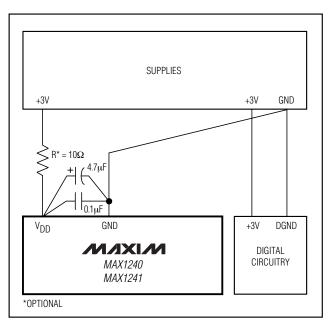

V<sub>DD</sub>電源内の高周波ノイズがADC内の高速コンパレータに影響を与える可能性があります。この電源は、0.1µF及び4.7µFコンデンサでスターグランドにバイパスしてください。最高の電源ノイズ除去比を得るには、コンデンサのリード線をできるだけ短くしてください。電源のノイズが特に大きい場合は、電源ノイズを減衰させるために10 抵抗をローパスフィルタとして接続してください(図14)。

図12. SPI/MICROWIREシリアルインタフェースタイミング(CPOL = CPHA = 0)

図13. QSPIシリアルインタフェースタイミング(CPOL = CPHA = 0)

図14. 電源接地条件

### 型番(続き) \_\_\_\_\_

| PART        | TEMP. RANGE     | PIN-<br>PACKAGE | INL<br>(LSB) |

|-------------|-----------------|-----------------|--------------|

| MAX1240AEPA | -40°C to +85°C  | 8 Plastic DIP   | ±1/2         |

| MAX1240BEPA | -40°C to +85°C  | 8 Plastic DIP   | ±1           |

| MAX1240CEPA | -40°C to +85°C  | 8 Plastic DIP   | ±1           |

| MAX1240AESA | -40°C to +85°C  | 8 SO            | ±1/2         |

| MAX1240BESA | -40°C to +85°C  | 8 SO            | ±1           |

| MAX1240CESA | -40°C to +85°C  | 8 SO            | ±1           |

| MAX1240AMJA | -55°C to +125°C | 8 CERDIP**      | ±1/2         |

| MAX1240BMJA | -55°C to +125°C | 8 CERDIP**      | ±1           |

| MAX1240CMJA | -55°C to +125°C | 8 CERDIP**      | ±1           |

| MAX1241ACPA | 0°C to +70°C    | 8 Plastic DIP   | ±1/2         |

| MAX1241BCPA | 0°C to +70°C    | 8 Plastic DIP   | ±1           |

| MAX1241CCPA | 0°C to +70°C    | 8 Plastic DIP   | ±1           |

| MAX1241ACSA | 0°C to +70°C    | 8 SO            | ±1/2         |

| MAX1241BCSA | 0°C to +70°C    | 8 SO            | ±1           |

| MAX1241CCSA | 0°C to +70°C    | 8 SO            | ±1           |

| MAX1241BC/D | 0°C to +70°C    | Dice*           | ±1           |

| MAX1241AEPA | -40°C to +85°C  | 8 Plastic DIP   | ±1/2         |

| MAX1241BEPA | -40°C to +85°C  | 8 Plastic DIP   | ±1           |

| MAX1241CEPA | -40°C to +85°C  | 8 Plastic DIP   | ±1           |

| MAX1241AESA | -40°C to +85°C  | 8 SO            | ±1/2         |

| MAX1241BESA | -40°C to +85°C  | 8 SO            | ±1           |

| MAX1241CESA | -40°C to +85°C  | 8 SO            | ±1           |

| MAX1241AMJA | -55°C to +125°C | 8 CERDIP**      | ±1/2         |

| MAX1241BMJA | -55°C to +125°C | 8 CERDIP**      | ±1           |

| MAX1241CMJA | -55°C to +125°C | 8 CERDIP**      | ±1           |

<sup>\*</sup>Dice are specified at  $T_A = +25$ °C, DC parameters only.

### チップ情報 \_\_\_\_\_

TRANSISTOR COUNT: 2558

SUBSTRATE CONNECTED TO GND

<sup>\*\*</sup> Contact factory for availability and processing to MIL-STD-883.

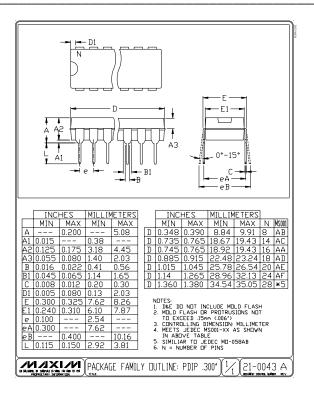

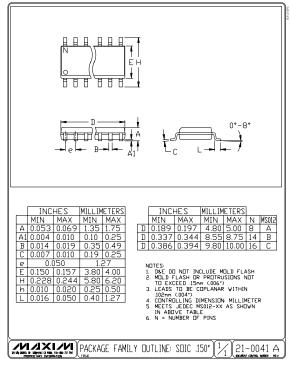

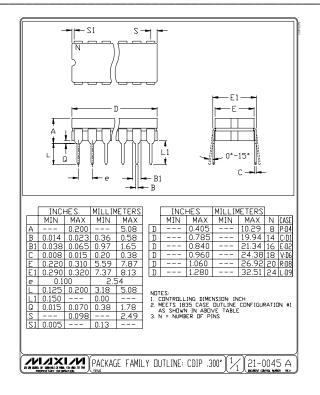

パッケージ

パッケージ(続き) \_\_\_

販売代理店

## マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

16 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600