データシート

SPI インターフェイス付き スタンドアロン イーサネット コントローラ

© 2006 Microchip Technology Inc. Preliminary DS39662B\_JP

#### マイクロチップ デバイスのコード保護についての詳細

- マイクロチップ製品は、マイクロチップが発行するデータシートに記載された仕様を満たしています。

- マイクロチップの製品ファミリは、正常かつ通常条件下で使用される限り、現在の半導体市場で最も確実で安全な製品です。

- コード保護を侵害する不正または不法な行為、または、マイクロチップが発効するデータシートに記載されている仕様範囲外でマイクロチップ 製品を使用し不正または不法な行為を行った場合は、知的財産の侵害となります。

- マイクロチップは、コードの完全性について懸念されるカスタマをサポートします。

- マイクロチップおよびその他の半導体メーカは、コードのセキュリティを保証しておりません。コード保護機能は、製品が破損しないことを保証するものではありません。

コード保護機能は常に改善されています。マイクロチップでは、弊社の製品のコード保護機能に対して不断な努力を重ねております。弊社のコード保護機能を侵害する行為は、デジタル ミレニアム著作権法 (DMCA) に違反します。カスタマのソフトウェアまたはその他の著作物への不正アクセスが生じた場合は、この著作権法に則り訴訟を起こす場合があります。

この文書に含まれるデバイス アプリケーションに関する情報は、ユーザーが任意で入手可能できるため、入手した文書が常に最新版であるとは限りません。したがって、ユーザーアプリケーションが製品仕様を満たしているかの判断はユーザー側の責任とします。

マイクロチップは、条件、品質、パフォーマンス、市場性または適合性を含む関連情報(この限りではない)が、明示または暗示、書面または口頭、制定内またはそうでない場合でもいかなる種類の保証を致しかねます。

マイクロチップは、この情報とその使用に起因する全ての責任を負いかねます。生命維持装置の重要な構成要素としてマイクロチップ製品を使用する場合は、マイクロチップによる正式な書面での承認以外は認可されません。いかなる知的所有権の下でも、明示的またはその他のライセンスの譲渡は認められません。

#### 商標

マイクロチップの名前およびロゴ (Microchip logo、Accuron、dsPIC、KEELOQ、microID、MPLAB、PIC、PICmicro、PICSTART、PRO MATE、PowerSmart、rfPIC、およびSmartShunt) は、米国およびその他の国において登録された、Microchip Technology Incorporatedの商標です。

AmpLab、FilterLab、Migratable Memory、MXDEV、MXLAB、PICMASTER、SEEVAL、SmartSensor、およびEmbedded Control Solutions Company は、米国において登録された、Microchip Technology Incorporated の商標です。

Analog-for-the-Digital Age、Application Maestro、dsPICDEM、

Analog-for-the-Digital Age、Application Maestro、dsPICDEM、dsPICDEM.net、dsPICworks、ECAN、ECONOMONITOR、FanSense、FlexROM、fuzzyLAB、In-Circuit Serial Programming、ICSP、ICEPIC、Linear Active Thermistor、MPASM、MPLIB、MPLINK、MPSIM、PICkit、PICDEM、PICDEM.net、PICLAB、PICtail、PowerCal、PowerInfo、PowerMate、PowerTool、rfLAB、rfPICDEM、Select Mode、Smart Serial、SmartTel、Total Endurance、およびWiperLockは、米国およびその他の国における、Microchip Technology Incorporatedの商標です。SQTPは、米国における、Microchip Technology Incorporatedのサービス商標です。

ここに示されるその他の商標はそれぞれの企業の著作物です。 © 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

マイクロチップ社は、2003 年 10 月に本社、設計およびウエハ工場 (アリゾナ州チャンドラーおよびテンピー、カリフォルニア州マウンテンビュー)品質システムが、ISO/TS-16949:2002 の認証を取得しました。マイクロチップの品質システムプロセスおよび手順は、PICmicro®8 ビット MCU、KeeLoQ®コード ホッピング デバイス、シリアル EEPROM、マイクロペリフェラル、不揮発性メモリ、およびアナログ製品を使用しています。また、マイクロチップの開発システムの設計および製造は、ISO 9001:2000 の認定を取得しています。

### SPI インターフェイス付きスタンドアロン イーサネット コントローラ

#### イーサネット コントローラの特徴

- IEEE 802.3 に準拠したイーサネット コントローラ

- MAC および 10BASE-T 対応の PHY を内蔵

- 自動極性検知および補正機能付き 10BASE-Tポートを1つサポート

- 全二重および半二重モードに対応

- 衝突時の自動再送信が設定可能

- パッディングおよび CRC 生成が設定可能

- エラーパケットの自動破棄が設定可能

- SPI インターフェイスの最大クロック スピード は 20MHz

#### バッファ

- 8K バイト送信/受信パケット デュアル ポート SRAM

- 送受信バッファ サイズがコンフィギュレーション可能

- ハードウェアで管理される循環受信 FIFO

- 自動インクリメント 機能付きバイト 幅ランダム/シーケンシャルアクセス

- 内蔵 DMA による高速データ転送

- さまざまなネットワークプロトコルに対応するハードウェア管理によるチェックサム計算機能

#### 媒体アクセス制御 (MAC) 機能

- ユニキャスト、マルチキャスト、ブロードキャストをサポート

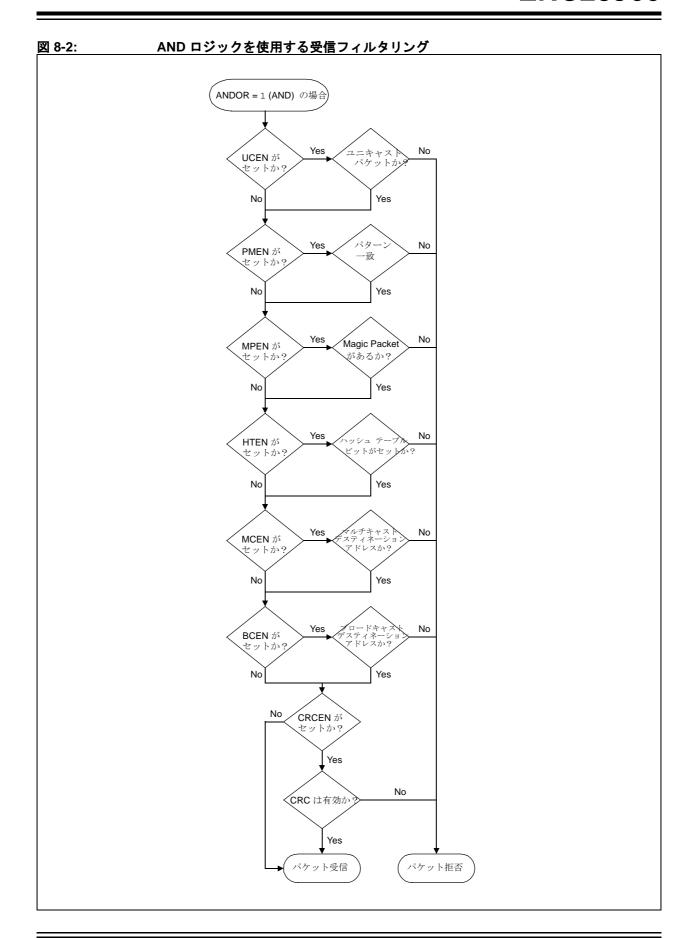

- 受信フィルタ機能と下記の AND または OR 条件によるホスト ウェイク アップ機能

- ユニキャスト デスティネーション アドレス

- マルチキャスト アドレス

- ブロードキャストアドレス

- Magic Packet<sup>TM</sup>

- 64ビットのハッシュ テーブルで指定されるグ ループ デスティネーション アドレス

- ユーザー指定のオフセット 値を使用して、最 大64バイトまでのプログラマブルパターン マッチ

#### 物理層 (PHY) 機能

- ループバック モード

- LINK、TX、RX、衝突、および全/半二重ステータス用の2つのプログラマブル LED 出力

#### 動作条件

- 6つの割り 込みソースおよび1つの割り 込み出力ピン

- 25 MHz クロック入力

- プログラマブルなプレスケーラ付きクロック出 カピン

- 動作電圧 3.1V ~ 3.6V (3.3V 標準)

- 5V トレラント入力

- 温度範囲: -40 ℃ ~ +85 ℃ 工業用温度、0 ℃ ~ +70 ℃ 一般用温度 (SSOP のみ)

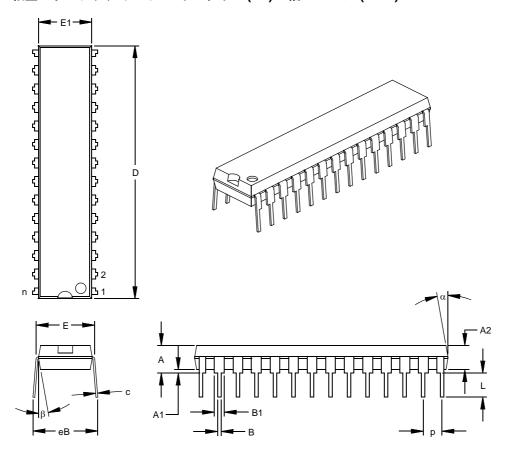

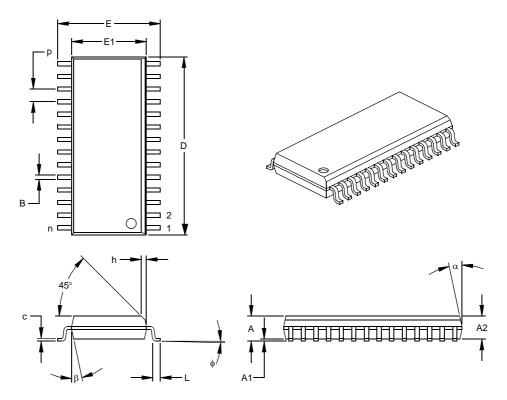

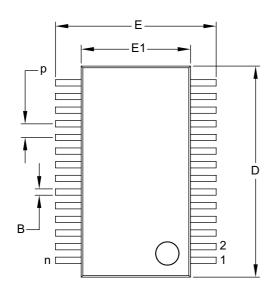

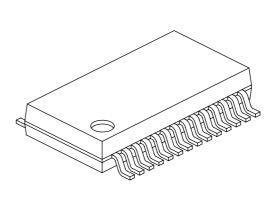

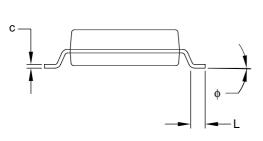

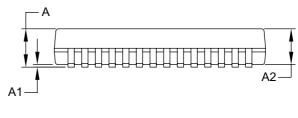

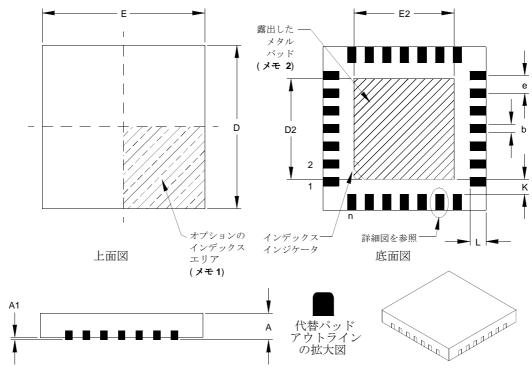

- 28 ピン SPDIP、SSOP、SOIC、QFN パッケージ

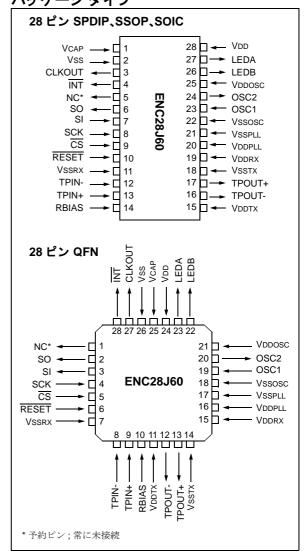

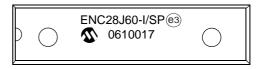

#### パッケージ タイプ

#### 目次

| 1.0  | 概要                         | . 3 |

|------|----------------------------|-----|

| 2.0  | 外部接続                       | . 5 |

| 3.0  | メモリ構成                      | 11  |

| 4.0  | シリアル ペリフェラル インターフェイス (SPI) | 25  |

| 5.0  | イーサネットの概要                  |     |

| 6.0  | 初期化                        | 33  |

| 7.0  | パケットの送受信                   | 39  |

| 8.0  | 受信フィルタ                     | 47  |

| 9.0  | 二重モードの設定およびネゴシエーション        | 53  |

| 10.0 | フロー制御                      | 55  |

| 11.0 | リセット                       | 59  |

|      | 割り込み                       |     |

|      | ダイレクト メモリ アクセス コントローラ      |     |

| 14.0 | パワー ダウン                    | 73  |

| 15.0 | 内蔵セルフテスト コントローラ            | 75  |

| 16.0 | 電気的特性                      | 79  |

| 17.0 | パッケージ情報                    | 83  |

| 索引   |                            | 91  |

| マイク  | 7ロチップのウェブ サイト              | 93  |

|      | 7マ変更通知サービス                 |     |

| カスク  | ママ サポート                    | 93  |

| 読者に  | <i>、</i> スポンス              | 94  |

| 製品記  | R職システム                     | 95  |

#### お客様へ

弊社では、マイクロチップ製品を効果的にご利用いただくために、よりよいドキュメント作成を心がけております。また、お客様のニーズに応えられるよう常に更新し、最新版を提供いたします。

本書についてリクエストまたはコメント等ございましたら、Marketing Communications Department 宛に電子メール (docerrors@microchip.com) または本書の最終ページにある「読者レスポンス」用紙をファックス ((480) 792-4150) していただきますようお願い申し上げます。

#### 最新版データ シート

最新版のデータシートを入手される場合は、弊社のウェブサイトからユーザー登録が必要です。

#### http://www.microchip.com

ドキュメントのバージョンは、フッタに記載されているドキュメント番号を確認してください。ドキュメント番号の最後のアルファベットがバージョンを示しています (例: DS30000A = DS30000 のバージョン A)。

#### エラッタ

現在のデバイスに対して、データ シートのマイナー変更および推奨されるソリューションなどを説明したエラッタが発効される場合があります。このエラッタ通知には、該当するシリコンのリビジョンおよびドキュメントのバージョンが記載されます。ご使用のデバイスに該当するエラッタを確認される場合は、次のサポートをご利用下さい。

- マイクロチップ社のウェブ サイト; http://www.microchip.com

- マイクロチップ社の営業所(最終ページ参照)

営業者へお問合わせする際は、現在ご使用のデバイス名、シリコンのリビジョン、ドキュメント番号およびバージョンが必要です。

#### カスタマ通知システム

マイクロチップ社の最新製品情報を入手希望される方は、www.microchip.com からご登録下さい。

#### 1.0 概要

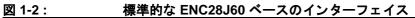

ENC28J60 は、業界標準 SPI (シリアル ペリフェラル インターフェイス) 付きスタンドアロン イーサネット コントローラです。そのため、SPI を使用できるすべてのコントローラに対するイーサネット ネットワーク インターフェイスとして使用できます。

ENC28J60 は、IEEE 802.3 仕様に準拠しています。パケットフィルタリング機能が統合されているため、入力されるパケットを制限できます。また、さまざまなネットワークプロトコルで使用されるチェックサム演算用に、内蔵 DMA による高速データ転送とハードウェアによる演算機能が用意されています。ホストコントローラとの通信には、最高 20MHz のクロック周波数の SPI が実装されています。2 つの専用ピンが、リンク用とネットワークアクティビティの確認用の LED に使用されます。

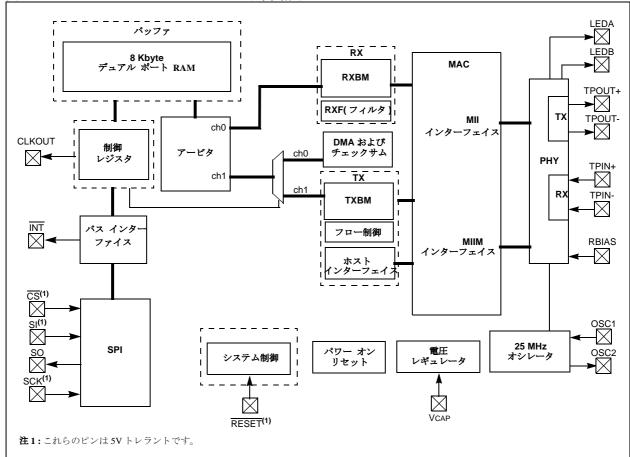

図 1-1 に、ENC28J60 のブロック 簡略図を示します。図 1-2 には、このデバイスを使用した標準的なアプリケーション回路を示します。ENC28J60 を使用する場合、マイクロコントローラとイーサネット ネットワークを接続するには、2つのパルストランスといくつかの受動コンポーネントのみ必要になります。

ENC28J60は、主に次の7つのファンクションブロックで 構成されています。

- ホスト コントローラと ENC28J60 間の通信チャネルとして機能する SPI

- 2. ENC28J60 を制御およびモニタするために使用する制御レジスタ

- 3. データ パケットの送受信用のデュアル ポート RAM バッファ

- 4. DMA、送信 / 受信ブロックからのリクエストがある場合、RAM バッファへのアクセスを制御するアービタ

- 5. SPI インターフェイスを介して受信したデータおよびコマンドを解釈するバス インターフェイス

- 6. IEEE 802.3 準拠の MAC ロジックを実装した MAC (媒体アクセス制御) モジュール

- ツイスト ペア インターフェイスに出力されたア ナログ データをエンコード/デコードする PHY (物理層) モジュール

このほかにも、オシレータ、オンチップ電圧レギュレータ、5Vトレラント I/O を提供するレベル変換器、システム制御ロジックなどのサポート ブロックがデバイスに含まれています。

<u>図 1-1: ENC28J60 のブロック簡略図</u>

表 1-1: I/O ピンの説明

| <u> </u> | ピン番                  | ᆂ   |           |             |                                                                                                 |

|----------|----------------------|-----|-----------|-------------|-------------------------------------------------------------------------------------------------|

| ピン名      | SPDIP,<br>SOIC, SSOP | QFN | ピン<br>タイプ | バッファ<br>タイプ | 説明                                                                                              |

| VCAP     | 1                    | 25  | Р         | _           | 内部レギュレータからの $2.5V$ 出力。標準値 $10\mu F$ 、最小値 $1\mu F$ でグランド接続された低 ESR (等価直列抵抗)キャパシタを、このピンに接続する必要がある |

| Vss      | 2                    | 26  | Р         | _           | グランド                                                                                            |

| CLKOUT   | 3                    | 27  | 0         | _           | プログラマブル クロック出力ピン <sup>(1)</sup>                                                                 |

| ĪNT      | 4                    | 28  | 0         | _           | NT   割り込み出力ピン <sup>(2)</sup>                                                                    |

| NC       | 5                    | 1   | 0         | _           | 予約ファンクション。常に未接続                                                                                 |

| SO       | 6                    | 2   | 0         | _           | SPI インターフェイスのデータ出力ピン <sup>(2)</sup>                                                             |

| SI       | 7                    | 3   | I         | ST          | SPI インターフェイスのデータ入力ピン <sup>(3)</sup>                                                             |

| SCK      | 8                    | 4   | I         | ST          | SPI インターフェイスのクロック入力 <sup>(3)</sup>                                                              |

| CS       | 9                    | 5   | I         | ST          | SPI インターフェイスのチップ セレクト入力ピン (3,4)                                                                 |

| RESET    | 10                   | 6   | I         | ST          | アクティブ Low デバイス リセット入力 <sup>(3, 4)</sup>                                                         |

| Vssrx    | 11                   | 7   | Р         | _           | PHY RX のグランド                                                                                    |

| TPIN-    | 12                   | 8   | I         | ANA         | 差動信号入力                                                                                          |

| TPIN+    | 13                   | 9   | I         | ANA         | 差動信号入力                                                                                          |

| RBIAS    | 14                   | 10  | I         | ANA         | PHY 用バイアス電流ピン。抵抗を使用してグランドへ接続<br>(2.4「トランス、終端、およびその他の外部コンポーネント」を参照)                              |

| VDDTX    | 15                   | 11  | Р         | _           | PHY TX 用の正の電源                                                                                   |

| TPOUT-   | 16                   | 12  | 0         | _           | 差動信号出力                                                                                          |

| TPOUT+   | 17                   | 13  | 0         | _           | 差動信号出力                                                                                          |

| Vsstx    | 18                   | 14  | Р         | _           | PHY TX 用のグランド                                                                                   |

| VDDRX    | 19                   | 15  | Р         | _           | PHY RX 用の正の 3.3V 電源                                                                             |

| VDDPLL   | 20                   | 16  | Р         | _           | PHY PLL 用の正の 3.3V 電源                                                                            |

| VSSPLL   | 21                   | 17  | Р         | _           | PHY PLL 用のグランド                                                                                  |

| Vssosc   | 22                   | 18  | Р         | _           | オシレータ用のグランド                                                                                     |

| OSC1     | 23                   | 19  | I         | ANA         | オシレータ入力                                                                                         |

| OSC2     | 24                   | 20  | 0         | _           | オシレータ出力                                                                                         |

| VDDOSC   | 25                   | 21  | Р         | _           | オシレータ用の正の 3.3V 電源                                                                               |

| LEDB     | 26                   | 22  | 0         | _           | LEDB ドライバ ピン <sup>(5)</sup>                                                                     |

| LEDA     | 27                   | 23  | 0         | _           | LEDA ドライバ ピン <sup>(5)</sup>                                                                     |

| VDD      | 28                   | 24  | Р         | _           | 正の 3.3V 電源供給                                                                                    |

**記号:** I =入力、O =出力、P =電源、DIG =デジタル入力、ANA =アナログ信号入力、ST =シュミットトリガ

注1: 最大ピン許容電流:8mA

- 2: 最大ピン許容電流: 4mA

- 3: 5V 入力可能

- 4: VDD に内部で弱プルアップされている

- 5: 最大ピン許容電流:12mA

#### 2.0 外部接続

#### 2.1 オシレータ

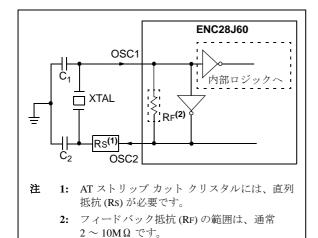

ENC28J60 は、OSC1 および OSC2 ピンへ接続した 25MHz のクリスタルで動作するように設計されています。ENC28J60 にはパラレルカット クリスタルを使用してください。シリーズカット クリスタルを使用した場合は、周波数がクリスタル製造会社の規格外になる可能性があります。図 2-1 に、標準的なオシレータ回路を示します。

なお、ENC28J60 は OSC1 ピンに接続された外部クロックソースで駆動することも可能です (図 2-2)。

#### 図 2-1: クリスタルオシレータの動作

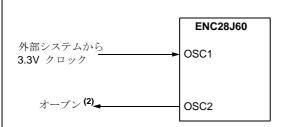

#### 図 2-2: 外部クロック ソース <sup>(1)</sup>

**注 1:** デューティ サイクル制限を確認する必要があります。

2: システム ノイズを低減させるため、抵抗で グランドへ接続する場合があります。ただ し、この場合はシステム電流が増加します。

#### 2.2 オシレータ スタートアップ タイマ

ENC28J60 には、OST (オシレータ スタートアップ タイマ) が内蔵されているため、オシレータや内蔵 PHY は使用前に必ず安定した状態になります。OST の有効期間は、POR 後またはパワー ダウン モードからウエイク アップされた後からカウント開始し、OSC1 クロックの 7500 サイクル (300μs) までとなります。この動作の遅延中、すべてのイーサネット レジスタおよびバッファメモリは、SPIバスを介して読み出し/書き込みが可能性です。しかし、この間にはソフトウェアからはパケット送信 (ECON1.TXRTS をセット)、パケット受信 (ECON1.RXEN をセット)、または MAC、MII、PHY レジスタへアクセスしてはいけません。

OST の有効期間が終了すると、ESTAT レジスタの CLKRDY ビットがセットされます。アプリケーション ソフトウェアはこのビットをポーリングし、通常デバ イスの動作を開始できるタイミングを判断する必要が あります。

メモ: POR 後または ENC28J60 がパワー ダウン モードから解除された後、CLKRDY ビットのポーリングは、パケット送信、パケット受信または MAC、MILL、PHY レジスタヘアクセスする前に CLKRDY ビットのポーリングを実行する必要があります。

#### 2.3 CLKOUTピン

クロック出力ピンは、ホスト コントローラ クロックとして使用するため、またはシステム内の他のデバイス用のクロック ソースとして使用するために提供されています。このピンには、内部プリスケール機能があり、出力を 1、2、3、4、または 8 で分周できます。ECOCONレジスタを介して、CLKOUT機能が有効になり、プリスケール機能が選択されます (レジスタ 2-1)。

正常なクロック信号を作成するには、電源投入直後は、CLKOUT ピンが Low に維持される必要があります。POR が完了後に OST がカウント を開始します。OST の有効期間が終了すると、CLKOUT ピンがデフォルト 周波数の 6.25 MHz (メイン クロックの 4 分周) で出力を開始します。その後、ENC28J60 がソフトウェアでリセット、または RESET ピンでリセットされても、CLKOUT 機能は変更されません (ECOCON の値は変更

されない)。また、パワーダウン モードに切り 替わる場合も、CLKOUT 機能は継続します。パワーダウンモードがキャンセルされると、OST はリセットされますが、CLKOUT 機能は継続します。CLKOUT 機能が無効 (ECOCON = 0) の場合、CLKOUT ピンは Low 駆動されます。

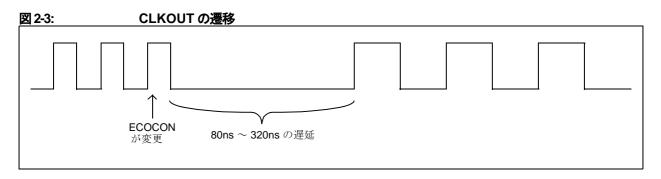

CLKOUT機能は、CLKOUTピン機能が有効、無効、またはプリスケール値が変更された場合に、最小限のタイミングを確保するように設計されています。ECOCONコンフィギュレーションで指定された周波数を超えるパルス (High/Low)は出力されません。ただし、周波数の切り替え時には、2および8OSC1クロック周期間の遅延が生じ、この間にクロックパルスは生成されません(図2-3参照)。この期間中、CLKOUTはLowに保持されます。

#### レジスタ 2-1: ECOCON: CLOCK OUTPUT 制御レジスタ

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| _     | _   |     | _   | _   | COCON2 | COCON1 | COCON0 |

| bit 7 |     |     |     |     |        |        | bit 0  |

#### 記号:

R=読み出し可能なビット W=書き込み可能なビット U=未実装ビット、0 として読み出される -n=POR 後の値 (1'=セット (0'=クリア x=不定

**bit 7-3 未実装ビット**: 0 が読み出される

bit 2-0 COCON2:COCON0:クロック出力コンフィギュレーション ビット

11x = ファクトリテスト用に予約。使用不可。グリッチ保護は保証されていない。

101 = メイン クロックを 8 分周した CLKOUT 出力 (3.125 MHz)

100 = メイン クロックを 4 分周した CLKOUT 出力 (6.25 MHz)

011 = メイン クロックを 3 分周した CLKOUT 出力 (8.333333 MHz)

010 = メイン クロックを 2 分周した CLKOUT 出力 (12.5 MHz)

001 = メイン クロックを 1 分周した CLKOUT 出力 (25 MHz)

000 = CLKOUT は無効。ピンは Low 駆動。

#### 2.4 トランス、終端、およびその他の 外部コンポーネント

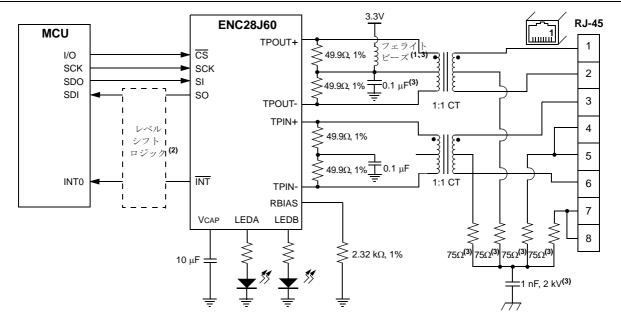

完全なイーサネット インターフェイスを構築するには、ENC28J60 に標準コンポーネントをいくつか外付けする必要があります。図 2-4 にこれらのコンポーネントの接続を示します。

PHY モジュールの内部アナログ回路には、RBIAS からグランドへ接続する抵抗 (2.32 k $\Omega$ 、1%) が必要です。この抵抗は、TPOUT+/- 信号の振幅に影響を与えます。ピンへのノイズの容量結合や伝送特性への影響を防ぐため、信号パターンを隣接せずに、チップに極力近づけてこの抵抗を配置してください。また、この抵抗は表面実装タイプを推奨します。

デバイスのデジタル ロジックの中には、2.5V で動作するものがあります。この電圧に対応するために内蔵電圧レギュレータが実装されています。必要な外部コンポーネントは、VCAP からグランドへ接続された外部フィルタコンデンサのみです。このコンデンサは、標準値  $10\,\mu F$  で最小値  $1\,\mu F$  の 低 ESR (等価直列レジスタ)が必要になります。内部レギュレータは、外部負荷を駆動するようには設計されていません。

TPIN+/TPIN- および TPOUT+/TPOUT- ピンには、イーサネット動作用の 1:1 CT パルストランスが必要です。イーサネット モジュールが有効のとき、電流が 2 つの TPOUT ピンから連続的に流れます。PHY が送信するとき、TPOUT- と TPOUT+ ピンからの電流を相対的に変化させることで、イーサネット ケーブル上に差動電圧が発生します。

TPOUT ピンとイーサネットトランス (非表示)の間に TPOUT インターフェイス用のコモンモードチョークを配置することはお勧めできません。EMI 放射を減らすためにコモンモードチョークを使用する場合は、イーサネットトランスと RJ-45 コネクタのピン 1 およびピン 2 の間に配置してください。多くのイーサネットトランスモジュールは、同デバイスパッケージ内にコモンモードチョークを内蔵しています。トランスは、静電気耐圧および IEEE 802.3 の絶縁要件を満たすため、少なくとも表 16-5 で指定される絶縁耐圧が必要です (特定トランスの要件は、16.0「電気的特性」を参照)。送信および受信インターフェイスには、さらに 2 つの抵抗と1つのコンデンサを追加して、伝送ラインを適切に終端して信号反射を抑える必要があります。

すべての電源ピンは、同一電源ソースに外部接続する必要があります。同様に、すべてのグランドピンも同一グランドノードに外部接続する必要があります。各VDDとVSSピンペアには、極力ピンに近接配置した $0.1 \mu F$ のセラミックバイパスコンデンサ(回路には非表示)が必要です。

ツイスト ペア インターフェイスを動作させるには比較的高い電流が必要なため、すべてのワイヤを短くする必要があります。抵抗ロスを低減させるためには電源配線に適切な配線幅を使用する必要があります。差動データ ラインを短くできない場合は、 $100\Omega$  の特性インピーダンスを持つように配線してください。

#### 図 2-4: ENC28J60 イーサネット終端および外部接続

- 注 1: フェライトビーズには、最低 80mA 相当品が必要です。

- 2: マイクロコントローラが 5V 動作する場合のみ必要です。詳細は、2.5 「I/O レベル」を参照してください。

- 3: これらのコンポーネントは、EMI を削減する目的で実装されています。

© 2006 Microchip Technology Inc. Preliminary DS39662B\_JP-page 7

#### 2.5 1/0 レベル

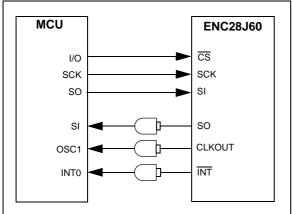

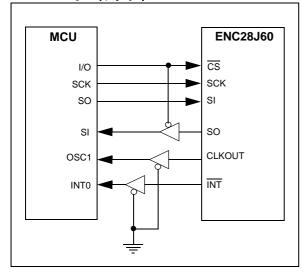

ENC28J60 は、3.3V デ<u>バ</u>イスですが、5V システムへの統合が可能です。SPI CS 入力、SCK 入力、SI 入力、および RESET ピンは、すべて 5V トレラントです。反対に、ホスト コントローラが 5 V 動作の場合には、ENC28J60 からの SPI と割り込み入力が 3.3V CMOS 出力で駆動されている場合は、ホスト コントローラが 5V 動作するため、仕様範囲外の動作になる可能性があります。この場合、単一方向のレベル変換器が必要になります。

レベル シフトには、安価な 74HCT08 (クワッド AND ゲート)、74ACT125 (クワッド トライステート バッファ)、またはその他の TTL レベル入力バッファ付き 5V CMOS チップを使用できます。トライステートバッファを使用することにより、ほかのデバイスと SPI バスを共有するシステムへの統合が容易になります。図 2-5 および図 2-6 に、変換回路例を示します。

図 2-5: AND ゲートを使用するレベルシフト

図 2-6: トライステート バッファを使用する レベルシフト

#### 2.6 LED コンフィギュレーション

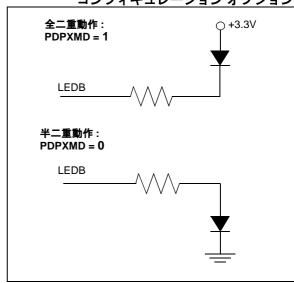

LEDA および LEDB ピンは、リセット時に極性を自動で検知する機能があります。接続方法は、ソース電流が流れた場合に LED が点灯する接続と、シンク電流が流れたときに LED が点灯する接続があります。システムリセットがかけられると、ENC28J60 は LED がどのように接続されているかを検知し、PHLCON レジスタで設定されたデフォルト ステートに駆動します。ENC28J60 の動作中に極性が変更された場合は、次にリセットがかけられるまで新しく設定された極性は検知されません。

LEDB の特徴は、リセット時に LED の接続が自動的に 読み出され、PHCON1.PDPXMD ビットをどのように 初期化するかを決定することです。ピンにソース電流 が流れると LED が点灯する場合は、リセット時にこの ビットがクリアされ、PHY は半二重モードがデフォルトになります。ピンにシンク電流が流れると LED が点 灯する場合は、リセット時にこのビットがセットされ、PHY は全二重モードがデフォルトになります。図 2-7に、この 2 つのオプションを示します。 LEDB に LED が接続されていない場合、PDPXMD ビットは不定値に リセットされます。

図 2-7: LEDB の極性およびリセットの コンフィギュレーション オプション

また、各 LED の動作極性 (アクティブのときにオン/オフ)、ブリンク レート、ブリンク ストレッチ インターバルを個別にコンフィギュレーションできます。これらのオプションは、LACFG3:LACFG0 およびLBCFG3:LBCFG0 ビットで制御します。表 2-1 に、ブリンク ストレッチの標準値を示します。

表 2-1: LED ブリンク ストレッチ長

| ストレッチ長       | 標準的なストレッチ (ms) |

|--------------|----------------|

| TNSTRCH (標準) | 40             |

| TMSTRCH(中)   | 70             |

| TLSTRCH(長)   | 140            |

#### レジスタ 2-2: PHLCON: PHY モジュールの LED 制御レジスタ

| R/W-0  | R/W-0 | R/W-1 | R/W-1 | R/W-0  | R/W-1  | R/W-0  | R/W-0  |

|--------|-------|-------|-------|--------|--------|--------|--------|

| r      | r     | r     | r     | LACFG3 | LACFG2 | LACFG1 | LACFG0 |

| bit 15 |       |       |       |        |        |        | bit 8  |

| R/W-0  | R/W-0  | R/W-1  | R/W-0  | R/W-0 | R/W-0 | R/W-1 | R/W-x |

|--------|--------|--------|--------|-------|-------|-------|-------|

| LBCFG3 | LBCFG2 | LBCFG1 | LBCFG0 | LFRQ1 | LFRQ0 | STRCH | r     |

| bit 7  |        |        |        |       |       |       | bit 0 |

記号:

R = 読み出し可能なビット W = 書き込み可能なビット U = 未実装ビット、0 として読み出される -n = POR 後の値 (1' = t - v) (0' = f - v) x = T定

bit 15-14予約:0 として書き込まれるbit 13-12予約:1 として書き込まれる

bit 11-8 LACFG3:LACFG0: LEDA コンフィギュレーション ビット

1111 = 予約

1110 = 二重ステータスおよび衝突アクティビティを表示する(常にストレッチ)

1101 = リンク ステータスおよび送信/受信アクティビティを表示する(常にストレッチ)

1100 = リンク ステータスおよび受信アクティビティを表示する (常にストレッチ)

1011 = 低速ブリンク

1010 = 高速ブリンク

1001 = オフ

1000 = オン

0111 = 送信 / 受信アクティビティを表示する (ストレッチ可能)

0110 = 予約

0101 = 二重ステータスを表示する

0100 = リンク ステータスを表示する

0011 = 衝突アクティビティを表示する(ストレッチ可能)

0010 = 受信アクティビティを表示する(ストレッチ可能)

0001 = 送信アクティビティを表示する(ストレッチ可能)

0000 = 予約

bit 7-4 LBCFG3:LBCFG0: LEDB コンフィギュレーション ビット

1110 = 二重ステータスおよび衝突アクティビティを表示する(常にストレッチ)

1101 = リンク ステータスおよび送信 / 受信アクティビティを表示する (常にストレッチ)

1100 = リンク ステータスおよび受信アクティビティを表示する(常にストレッチ)

1011 = 低速ブリンク

1010 = 高速ブリンク

1001=オフ

1000 = オン

0111 = 送信 / 受信アクティビティを表示する (ストレッチ可能)

0110 = 予約

0101 = 二重ステータスを表示する

0100 = リンク ステータスを表示する

0011 = 衝突アクティビティを表示する(ストレッチ可能)

0010 = 受信アクティビティを表示する(ストレッチ可能)

0001 = 送信アクティビティを表示する(ストレッチ可能)

0000 = 予約

bit 3-2 LFRQ1:LFRQ0: LED パルス ストレッチ タイム コンフィギュレーション ビット (表 2-1 を参照)

11 = 予約

10 = TLSTRCH で LED イベントをストレッチする

01 = TMSTRCH で LED イベントをストレッチする

00 = TNSTRCH で LED イベントをストレッチする

bit 1 STRCH: LED パルス ストレッチ イネーブル ビット

1= LFRQ1:LFRQ0 コンフィギュレーションに基づいてストレッチされた LED パルスを表示する

0= ストレッチ可能な LED イベントが発生している間のみ表示する

**bit 0 予約:** 0 が書き込まれる

メモ:

#### 3.0 メモリ構成

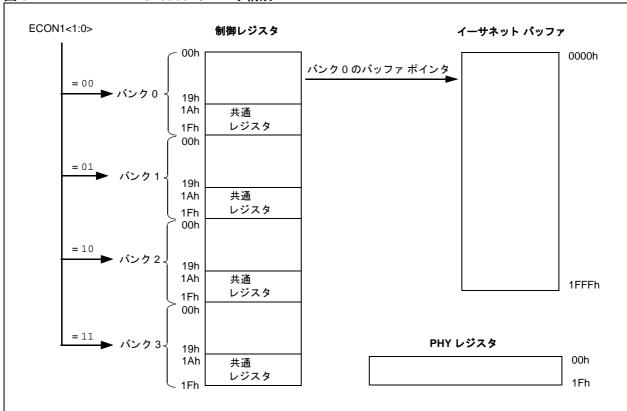

ENC28J60 のすべてのメモリは、スタティック RAM としてインプリメントされています。 メモリ タイプは、次の3つです。

- 制御レジスタ

- イーサネット バッファ

- PHY レジスタ

制御レジスタのメモリには、ENC28J60のコンフィギュレーション、制御、ステータス読み出しに使用されるレジスタがあります。制御レジスタは SPI インターフェイスを介して直接読み出し / 書き込みされます。

イーサネット バッファは、イーサネット コントローラで使用される送信および受信メモリが 含まれ、この 2 つは 1 つのメモリ空間にあります。メモリのサイズは、SPI インターフェイスを介してホスト コントローラで設定できます。 イーサネット バッファへのアクセスは、読み出しバッファメモリ/書き込みバッファメモリの SPI コマンドでのみ可能です。詳細は、4.2.2「バッファメモリ請み出しコマンド」および 4.2.4「バッファメモリ書き込みコマンド」を参照してください。

PHY レジスタは、PHY モジュールのコンフィギュレーション、制御、およびステータス読み出しに使用されます。 SPI インターフェイス経由で直接アクセスできません。 MAC モジュールに組み込まれた MIIM (Media Independent Interface Management) を介してアクセスします。

図 3-1 に、ENC28J60 のデータ メモリ構成を示します。

#### 図 3-1: ENC28J60 のメモリ構成

メモ: メモリ領域は、実際の比率で示していません。制御レジスタのサイズは、詳細を示すため拡大しています。

#### 3.1 制御レジスタ

制御レジスタは、ホストコントローラとオンチップイーサネットコントローラロジック間の重要なインターフェイスとなります。これらのレジスタに書き込みを実行すると、インターフェイスの動作を制御します。一方、読み出しを実行すると、ホストコントローラが動作をモニタできるようになります。

制御レジスタメモリは4つのバンクに分割され、ECON1レジスタのバンクセレクトビット(BSEL1:BSEL0)で選択できます。各バンクは32バイトであり、5ビットのアドレス値でアドレスを指定します。

すべてのバンクの最後の5ビット ( $1Bh \sim 1Fh$ ) は、共通レジスタ セット (EIE、EIR、ESTAT、ECON2、および ECON1) を指します。これらのレジスタは、デバイス動作を制御およびモニタリングする上で非常に重要です。この共通マッピングにより、バンクを切り替えず

にこれらのレジスタ〜アクセスできます。ECON1 および ECON2 レジスタの詳細は、このセクションの後半で説明します。

実装されていないアドレスがいくつかあります。これらのアドレスに書き込みを実行すると無視され、読み出されるビットはすべて0となります。各バンクのアドレス1Ah は予約されており、このレジスタへは読み出しおよび書き込みが実行されません。その他の予約レジスタは、読み出される場合がありますが、これらのレジスタコンテンツは変更されません。予約ビットを含むレジスタへの読み出しおよび書き込みを実行する場合は、レジスタの定義に記述された規則に従う必要があります。ENC28J60の制御レジスタは、一般的に ETH、MAC、および MII にグループ分けされます。レジスタ名が「E」で始まっている場合は ETH グループとなり、「MA」で始まっている場合は MAC グループとなり、「MI」で始まっている場合は MII グループとなり、「MI」で始まっている場合は MII グループとなります。

表 3-1: ENC28J60 制御レジスタのマップ

| 4X J-1. | LNC2030   | Մ արդագությ | A 700 ( ) 2 |       |          |        |         |

|---------|-----------|-------------|-------------|-------|----------|--------|---------|

| パンク 0   |           | パンク1        |             | パンク 2 |          | パンク3   |         |

| アドレス    | レジスタ名     | アドレス        | レジスタ名       | アドレス  | レジスタ名    | アドレス _ | レジスタ名   |

| 00h     | ERDPTL    | 00h         | EHT0        | 00h   | MACON1   | 00h    | MAADR5  |

| 01h     | ERDPTH    | 01h         | EHT1        | 01h   | 予約       | 01h    | MAADR6  |

| 02h     | EWRPTL    | 02h         | EHT2        | 02h   | MACON3   | 02h    | MAADR3  |

| 03h     | EWRPTH    | 03h         | EHT3        | 03h   | MACON4   | 03h    | MAADR4  |

| 04h     | ETXSTL    | 04h         | EHT4        | 04h   | MABBIPG  | 04h    | MAADR1  |

| 05h     | ETXSTH    | 05h         | EHT5        | 05h   | _        | 05h    | MAADR2  |

| 06h     | ETXNDL    | 06h         | EHT6        | 06h   | MAIPGL   | 06h    | EBSTSD  |

| 07h     | ETXNDH    | 07h         | EHT7        | 07h   | MAIPGH   | 07h    | EBSTCON |

| 08h     | ERXSTL    | 08h         | EPMM0       | 08h   | MACLCON1 | 08h    | EBSTCSL |

| 09h     | ERXSTH    | 09h         | EPMM1       | 09h   | MACLCON2 | 09h    | EBSTCSH |

| 0Ah     | ERXNDL    | 0Ah         | EPMM2       | 0Ah   | MAMXFLL  | 0Ah    | MISTAT  |

| 0Bh     | ERXNDH    | 0Bh         | EPMM3       | 0Bh   | MAMXFLH  | 0Bh    | _       |

| 0Ch     | ERXRDPTL  | 0Ch         | EPMM4       | 0Ch   | 予約       | 0Ch    | _       |

| 0Dh     | ERXRDPTH  | 0Dh         | EPMM5       | 0Dh   | 予約       | 0Dh    | _       |

| 0Eh     | ERXWRPTL  | 0Eh         | EPMM6       | 0Eh   | 予約       | 0Eh    | _       |

| 0Fh     | ERXWRPTH  | 0Fh         | EPMM7       | 0Fh   | _        | 0Fh    | _       |

| 10h     | EDMASTL   | 10h         | EPMCSL      | 10h   | 予約       | 10h    | _       |

| 11h     | EDMASTH   | 11h         | EPMCSH      | 11h   | 予約       | 11h    | _       |

| 12h     | EDMANDL   | 12h         | _           | 12h   | MICMD    | 12h    | EREVID  |

| 13h     | EDMANDH   | 13h         | _           | 13h   | _        | 13h    | _       |

| 14h     | EDMADSTL  | 14h         | EPMOL       | 14h   | MIREGADR | 14h    | _       |

| 15h     | EDMADSTH  | 15h         | EPMOH       | 15h   | 予約       | 15h    | ECOCON  |

| 16h     | EDMACSL   | 16h         | 予約          | 16h   | MIWRL    | 16h    | 予約      |

| 17h     | EDMACSH   | 17h         | 予約          | 17h   | MIWRH    | 17h    | EFLOCON |

| 18h     | _         | 18h         | ERXFCON     | 18h   | MIRDL    | 18h    | EPAUSL  |

| 19h     | _         | 19h         | EPKTCNT     | 19h   | MIRDH    | 19h    | EPAUSH  |

| 1Ah     | 予約        | 1Ah         | 予約          | 1Ah   | 予約       | 1Ah    | 予約      |

| 1Bh     | EIE       | 1Bh         | EIE         | 1Bh   | EIE      | 1Bh    | EIE     |

| 1Ch     | EIR       | 1Ch         | EIR         | 1Ch   | EIR      | 1Ch    | EIR     |

| 1Dh     | 1Dh ESTAT |             | ESTAT       | 1Dh   | ESTAT    | 1Dh    | ESTAT   |

| 1Eh     | 1Eh ECON2 |             | ECON2       | 1Eh   | ECON2    | 1Eh    | ECON2   |

| 1Fh     | ECON1     | 1Fh         | ECON1       | 1Fh   | ECON1    | 1Fh    | ECON1   |

|         |           | _           |             | -     |          |        |         |

表 3-2: ENC28J60 の制御レジスタのサマリ

| 表 3-2:   | ENCZ                                                                             | <b>中へいりり</b>    | 一個レンス          | タのサマ          | <u>'</u>       | 1           | 1       | 1                     | 1         |           |

|----------|----------------------------------------------------------------------------------|-----------------|----------------|---------------|----------------|-------------|---------|-----------------------|-----------|-----------|

| レジスタ名    | ピット7                                                                             | ピット6            | ピット 5          | ピット4          | ピット3           | ピット2        | ピット1    | ピット0                  | Reset の値  | 参照<br>ページ |

| EIE      | INTIE                                                                            | PKTIE           | DMAIE          | LINKIE        | TXIE           | r           | TXERIE  | RXERIE                | 0000 0000 | 67        |

| EIR      | _                                                                                | PKTIF           | DMAIF          | LINKIF        | TXIF           | r           | TXERIF  | RXERIF                | -000 0000 | 68        |

| ESTAT    | INT                                                                              | BUFER           | r              | LATECOL       | _              | RXBUSY      | TXABRT  | CLKRDY <sup>(1)</sup> | 0000 -000 | 66        |

| ECON2    | AUTOINC                                                                          | PKTDEC          | PWRSV          | r             | VRPS           | _           | _       | _                     | 1000 0    | 16        |

| ECON1    | TXRST                                                                            | RXRST           | DMAST          | CSUMEN        | TXRTS          | RXEN        | BSEL1   | BSEL0                 | 0000 0000 | 15        |

| ERDPTL   | Read Pointer                                                                     | Low Byte ER     | DPT<7:0>)      |               |                |             |         |                       | 1111 1010 | 17        |

| ERDPTH   | _                                                                                | _               | _              | Read Pointer  | High Byte (E   | RDPT<12:8>) |         |                       | 0 0101    | 17        |

| EWRPTL   | Write Pointer                                                                    | Low Byte (EV    | /RPT<7:0>)     |               |                |             |         |                       | 0000 0000 | 17        |

| EWRPTH   | _                                                                                | _               | _              | Write Pointer | High Byte (E   | WRPT<12:8>) |         |                       | 0 0000    | 17        |

| ETXSTL   | TX Start Low                                                                     | Byte (ETXST-    | <7:0>)         |               |                |             |         |                       | 0000 0000 | 17        |

| ETXSTH   | _                                                                                | _               | _              | TX Start High | Byte (ETXST    | <12:8>)     |         |                       | 0 0000    | 17        |

| ETXNDL   | TX End Low                                                                       | Byte (ETXND-    | <7:0>)         |               |                |             |         |                       | 0000 0000 | 17        |

| ETXNDH   | _                                                                                | _               | _              | TX End High   | Byte (ETXND    | <12:8>)     |         |                       | 0 0000    | 17        |

| ERXSTL   | RX Start Low                                                                     | Byte (ERXST     | <7:0>)         |               |                |             |         |                       | 1111 1010 | 17        |

| ERXSTH   | _                                                                                | _               | _              | RX Start High | n Byte (ERXS   | Γ<12:8>)    |         |                       | 0 0101    | 17        |

| ERXNDL   | RX End Low                                                                       | Byte (ERXND     | <7:0>)         |               |                |             |         |                       | 1111 1111 | 17        |

| ERXNDH   | _                                                                                | _               | _              | RX End High   | Byte (ERXND    | 0<12:8>)    |         |                       | 1 1111    | 17        |

| ERXRDPTL | RX RD Point                                                                      | er Low Byte (E  | RXRDPT<7:0     | 0>)           |                |             |         |                       | 1111 1010 | 17        |

| ERXRDPTH | _                                                                                | _               | _              | RX RD Point   | er High Byte ( | ERXRDPT<12  | 2:8>)   |                       | 0 0101    | 17        |

| ERXWRPTL | RX WR Point                                                                      | ter Low Byte (I | RXWRPT<7       | :0>)          |                |             |         |                       | 0000 0000 | 17        |

| ERXWRPTH | _                                                                                | _               | _              | RX WR Point   | er High Byte ( | ERXWRPT<1   | 2:8>)   |                       | 0 0000    | 17        |

| EDMASTL  | DMA Start Lo                                                                     | w Byte (EDM/    | AST<7:0>)      |               |                |             |         |                       | 0000 0000 | 73        |

| EDMASTH  | _                                                                                | _               | _              | DMA Start Hi  | gh Byte (EDN   | IAST<12:8>) |         |                       | 0 0000    | 73        |

| EDMANDL  | DMA End Lo                                                                       | w Byte (EDMA    | ND<7:0>)       |               |                |             |         |                       | 0000 0000 | 73        |

| EDMANDH  | _                                                                                | _               | _              | DMA End Hig   | gh Byte (EDM   | AND<12:8>)  |         |                       | 0 0000    | 73        |

| EDMADSTL | DMA Destina                                                                      | tion Low Byte   | (EDMADST<      | 7:0>)         |                |             |         |                       | 0000 0000 | 73        |

| EDMADSTH | _                                                                                | _               | _              |               | tion High Byte | e (EDMADST< | :12:8>) |                       | 0 0000    | 73        |

| EDMACSL  | DMA Checks                                                                       | sum Low Byte    | (EDMACS<7:     | 0>)           |                |             |         |                       | 0000 0000 | 74        |

| EDMACSH  |                                                                                  | um High Byte    | `              | 5:8>)         |                |             |         |                       | 0000 0000 | 74        |

| EHT0     |                                                                                  | Byte 0 (EHT<7:  |                |               |                |             |         |                       | 0000 0000 | 53        |

| EHT1     | +                                                                                | Byte 1 (EHT<1   |                |               |                |             |         |                       | 0000 0000 | 53        |

| EHT2     |                                                                                  | Byte 2 (EHT<2   |                |               |                |             |         |                       | 0000 0000 | 53        |

| EHT3     |                                                                                  | Byte 3 (EHT<3   |                |               |                |             |         |                       | 0000 0000 | 53        |

| EHT4     |                                                                                  | Byte 4 (EHT<3   |                |               |                |             |         |                       | 0000 0000 | 53        |

| EHT5     |                                                                                  | Byte 5 (EHT<4   |                |               |                |             |         |                       | 0000 0000 | 53        |

| EHT6     |                                                                                  | Byte 6 (EHT<5   |                |               |                |             |         |                       | 0000 0000 | 53        |

| EHT7     | 1                                                                                | Byte 7 (EHT<6   |                | `             |                |             |         |                       | 0000 0000 | 53        |

| EPMM0    | Pattern Match Mask Byte 0 (EPMM<7:0>)                                            |                 |                |               |                |             |         |                       | 0000 0000 | 52        |

| EPMM1    | Pattern Match Mask Byte 1 (EPMM<15:8>)  Pattern Match Mask Byte 2 (EPMM<23:16>)  |                 |                |               |                |             |         |                       | 0000 0000 | 52        |

| EPMM2    | 1                                                                                |                 | •              |               |                |             |         |                       | 0000 0000 | 52        |

| EPMM3    | Pattern Match Mask Byte 3 (EPMM<31:24>)  Pattern Match Mask Byte 4 (EPMM<39:32>) |                 |                |               |                |             |         |                       |           | 52        |

| EPMM4    | Pattern Match Mask Byte 4 (EPMM<39:32>)  Pattern Match Mask Byte 5 (EPMM<47:40>) |                 |                |               |                |             |         |                       |           | 52        |

| EPMM5    |                                                                                  |                 | -              |               |                |             |         |                       | 0000 0000 | 52        |

| EPMM6    |                                                                                  | h Mask Byte 6   |                |               |                |             |         |                       | 0000 0000 | 52        |

| EPMM7    | Pattern Matc                                                                     | h Mask Byte 7   | (EPIVIIVI<63:5 | (<סו          |                |             |         |                       | 0000 0000 | 52        |

$x = \pi H$ 、 $u = \overline{x}$  変更なし、 $u = \overline{x}$  まなれていない、 $u = \overline{x}$  条件に依存する値、 $u = \overline{x}$  で  $u = \overline{x}$  ないない、 $u = \overline{x}$  で  $u = \overline{x}$  にリセットしますが、その他のリセットの影響は受けません。 記号:

注

2: EREVID は読み出し専用レジスタです。

3: ECOCON は、POR で '-----100' にリセットし、その他のリセットでは '-----uuu' にリセットします。

ENC28J60 の制御レジスタのサマリ (続き) 表 3-2:

| 表 3-2:                | ENG                                                  | なりもの の事          | 仰レンス           | タのサマ          | <u>リ(杬さ)</u>  |             |             |        |           |           |

|-----------------------|------------------------------------------------------|------------------|----------------|---------------|---------------|-------------|-------------|--------|-----------|-----------|

| レジスタ名                 | ピット7                                                 | ピット6             | ピット 5          | ピット4          | ピット3          | ピット2        | ピット1        | ピット 0  | Reset の値  | 参照<br>ページ |

| EPMCSL                | Pattern Matc                                         | h Checksum L     | ow Byte (EPN   | MCS<7:0>)     |               |             |             |        | 0000 0000 | 52        |

| EPMCSH                | Pattern Matc                                         | h Checksum F     | ligh Byte (EPI | MCS<15:0>)    |               | 0000 0000   | 52          |        |           |           |

| EPMOL                 | Pattern Matc                                         | h Offset Low E   | Byte (EPMO<7   | <b>'</b> :0>) |               |             |             |        | 0000 0000 | 52        |

| ЕРМОН                 | _                                                    | _                | _              | Pattern Match | h Offset High | Byte (EPMO< | 12:8>)      |        | 0 0000    | 52        |

| ERXFCON               | UCEN                                                 | ANDOR            | CRCEN          | PMEN          | MPEN          | HTEN        | MCEN        | BCEN   | 1010 0001 | 48        |

| EPKTCNT               | Ethernet Pac                                         | ket Count        |                |               |               |             |             |        | 0000 0000 | 43        |

| MACON1                | _                                                    | _                | _              | r             | TXPAUS        | RXPAUS      | PASSALL     | MARXEN | 0 0000    | 34        |

| MACON3                | PADCFG2                                              | PADCFG1          | PADCFG0        | TXCRCEN       | PHDREN        | HFRMEN      | FRMLNEN     | FULDPX | 0000 0000 | 35        |

| MACON4                | _                                                    | DEFER            | BPEN           | NOBKOFF       | _             | _           | r           | r      | -00000    | 36        |

| MABBIPG               | _                                                    | Back-to-Back     | Inter-Packet   | Gap (BBIPG<   | 6:0>)         | •           |             | •      | -000 0000 | 36        |

| MAIPGL                | _                                                    | Non-Back-to-     | -Back Inter-Pa | cket Gap Low  | Byte (MAIPG   | L<6:0>)     |             |        | -000 0000 | 34        |

| MAIPGH                | _                                                    | Non-Back-to-     | -Back Inter-Pa | cket Gap High | Byte (MAIPG   | iH<6:0>)    |             |        | -000 0000 | 34        |

| MACLCON1              | _                                                    | _                | _              | _             | Retransmissi  | on Maximum  | (RETMAX<3:0 | )>)    | 1111      | 34        |

| MACLCON2              | _                                                    | _                | Collision Win  | dow (COLWIN   | l<5:0>)       |             |             |        | 11 0111   | 34        |

| MAMXFLL               | Maximum Fra                                          | ame Length Lo    | w Byte (MAN    | IXFL<7:0>)    |               |             |             |        | 0000 0000 | 34        |

| MAMXFLH               | Maximum Fra                                          | ame Length H     | igh Byte (MAN  | //XFL<15:8>)  |               |             |             |        | 0000 0110 | 34        |

| MICMD                 | _                                                    | _                | _              | _             | _             | _           | MIISCAN     | MIIRD  | 00        | 21        |

| MIREGADR              | _                                                    | _                | _              | MII Register  | Address (MIR  | EGADR<4:0>) | )           | •      | 0 0000    | 19        |

| MIWRL                 | MII Write Dat                                        | ta Low Byte (N   | 1IWR<7:0>)     | •             |               |             |             |        | 0000 0000 | 19        |

| MIWRH                 | MII Write Dat                                        | ta High Byte (N  | MIWR<15:8>)    |               |               |             |             |        | 0000 0000 | 19        |

| MIRDL                 | MII Read Da                                          | ta Low Byte (N   | /IRD<7:0>)     |               |               |             |             |        | 0000 0000 | 19        |

| MIRDH                 | MII Read Da                                          | ta High Byte(N   | /IRD<15:8>)    |               |               |             |             |        | 0000 0000 | 19        |

| MAADR5                | MAC Addres                                           | s Byte 5 (MAA    | DR<15:8>)      |               |               |             |             |        | 0000 0000 | 34        |

| MAADR6                | MAC Addres                                           | s Byte 6 (MAA    | DR<7:0>)       |               |               |             |             |        | 0000 0000 | 34        |

| MAADR3                | MAC Addres                                           | s Byte 3 (MAA    | DR<31:24>),    | OUI Byte 3    |               |             |             |        | 0000 0000 | 34        |

| MAADR4                | MAC Addres                                           | s Byte 4 (MAA    | DR<23:16>)     |               |               |             |             |        | 0000 0000 | 34        |

| MAADR1                | MAC Addres                                           | s Byte 1 (MAA    | DR<47:40>),    | OUI Byte 1    |               |             |             |        | 0000 0000 | 34        |

| MAADR2                | MAC Addres                                           | s Byte 2 (MAA    | DR<39:32>),    | OUI Byte 2    |               |             |             |        | 0000 0000 | 34        |

| EBSTSD                | Built-in Self-1                                      | Геst Fill Seed ( | EBSTSD<7:0     | >)            |               |             |             |        | 0000 0000 | 78        |

| EBSTCON               | PSV2                                                 | PSV1             | PSV0           | PSEL          | TMSEL1        | TMSEL0      | TME         | BISTST | 0000 0000 | 78        |

| EBSTCSL               | Built-in Self-Test Checksum Low Byte (EBSTCS<7:0>)   |                  |                |               |               |             |             |        | 0000 0000 | 78        |

| EBSTCSH               | Built-in Self-Test Checksum High Byte (EBSTCS<15:8>) |                  |                |               |               |             |             |        | 0000 0000 | 78        |

| MISTAT                | _                                                    | _                | _              | _             | r             | NVALID      | SCAN        | BUSY   | 0000      | 21        |

| EREVID <sup>(2)</sup> | _                                                    | _                | _              | Ethernet Rev  | ision ID (ERE | VID<4:0>)   | •           |        | d dddd    | 22        |

| ECOCON <sup>(3)</sup> | _                                                    | _                | _              | _             | _             | COCON2      | COCON1      | COCON0 | 100       | 6         |

| EFLOCON               | _                                                    | _                | _              | _             | _             | FULDPXS     | FCEN1       | FCEN0  | 000       | 58        |

| EPAUSL                | Pause Timer                                          | Value Low By     | te (EPAUS<7    | 0>)           |               | l .         | ı           | ı      | 0000 0000 | 59        |

| EPAUSH                | Pause Timer                                          | Value High By    | /te (EPAUS<1   | 5:8>)         |               |             |             |        | 0001 0000 | 59        |

x=不明、u=変更なし、--=実装されていない、q=条件に依存する値、r=予約、変更不可 記号:

1: CLKRDY は、POR で 0 にリセットしますが、その他のリセットの影響は受けません。

#### 3.1.1 ECON1 レジスタ

レジスタ 3-1 で示す ECON1 レジスタは、ENC28J60 の主要ファンクションを制御します。受信イネーブル、送信リクエスト、DMA 制御、バンク セレクト ビットは、この ECON1 レジスタに含まれます。

#### レジスタ 3-1: ECON1: イーサネット制御レジスタ 1

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|-------|-------|-------|-------|

| TXRST | RXRST | DMAST | CSUMEN | TXRTS | RXEN  | BSEL1 | BSEL0 |

| bit 7 |       |       |        |       |       |       | bit 0 |

記号:

R=読み出し可能なビット W=書き込み可能なビット U=未実装ビット、0 として読み出される -n=POR 後の値 (1'=セット (0'=クリア x=不定

bit 7 TXRST: 送信ロジック リセット ビット

1 = 送信ロジックは Reset を保持

0 = 通常動作

bit 6 RXRST: 受信ロジック リセット ビット

1 = 受信ロジックは Reset を保持

0 = 通常動作

bit 5 DMAST: DMA スタートおよびビジー ステータス ビット

1 = DMA コピー中か、チェックサム計算中

0 = DMA アイドル中

bit 4 CSUMEN: DMA チェックサム イネーブル ビット

1 = DMA ハードウェアがチェックサム計算する

0 = DMA ハードウェアがバッファ メモリをコピーする

bit 3 TXRTS: 送信リクエストを送るビット

1 = 送信ロジックがパケットを送信する

0 = 送信ロジックはアイドル状態

bit 2 **RXEN:** 受信イネーブル ビット

1= 現在のフィルタ コンフィギュレーションを通ったパケットが受信バッファへ書き込まれる

0 = すべての受信パケットが無視される

bit 1-0 **BSEL1:BSEL0:** バンク選択ビット

11 = SPI がバンク 3 のレジスタヘアクセスする

10 = SPI がバンク 2 のレジスタヘアクセスする

01 = SPI がバンク 1 のレジスタヘアクセスする

00 = SPI がバンク 0 のレジスタヘアクセスする

#### 3.1.2 ECON2 レジスタ

レジスタ 3-2 に示す ECON2 は、ENC28J60 の主要ファ ンクションの制御に使用されます。

#### レジスタ 3-2: ECON2: イーサネット制御レジスタ 2

| R/W-1   | R/W-0 <sup>(1)</sup> | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|---------|----------------------|-------|-------|-------|-----|-----|-------|

| AUTOINC | PKTDEC               | PWRSV | r     | VRPS  | _   | _   | _     |

| bit 7   |                      |       |       |       |     |     | bit 0 |

記号:

R=読み出し可能なビット W=書き込み可能なビット U=未実装ビット、0 として読み出される -n=POR 後の値 1'=セット 0'=クリア x=不定

bit 7 AUTOINC: 自動バッファ ポインタ インクリメント イネーブル ビット

1 = EDATA から読み出し/EDATA へ書き込みする際に、ERDPT/EWRPT を自動インクリメント

0 = バッファヘアクセス後、ERDPT/ EWRPT を自動で変更しない

bit 6 **PKTDEC:** パケット デクリメント ビット

1 = EPKTCNT レジスタを 1 つデクリメントする

0 = EPKTCNT を変更しない

bit 5 **PWRSV:** パワー セーブ イネーブル ビット

1 = MAC、PHY、および制御ロジックは、低電力スリープ モード

0 = 通常動作

**bit 4 予約:**0 を保持する

bit 3 VRPS: 電圧レギュレータ パワー セーブ イネーブル ビット

PWRSV = 1 の場合:

1 = 内部レギュレータは低電力モード

0 = 標準モード

PWRSV = 0 の場合:

ビットは無視される;レギュレータは、常にデバイスが要求する電流量を出力する

**bit 2-0 未実装ビット:**0 が読み出される

注 1: このビットはセットされると、自動でクリアされます。

#### 3.2 イーサネット バッファ

イーサネットバッファには、イーサネットコントローラで使用される送信メモリと受信メモリが含まれます。バッファの総容量は8Kバイトで、受信バッファ空間と送信バッファ空間に分かれています。この2つのメモリ空間のサイズとロケーションは、ホストコントローラからSPIインターフェイスを介してプログラム可能です。

図 3-2 に、バッファ空間の関係を示します。

#### 3.2.1 受信バッファ

受信バッファは、ハードウェアで制御される循環 FIFO バッファで構成されています。2 つのレジスタ (ERXSTH:ERXSTL および ERXNDH:ERXNDL) がポインタとして機能し、メモリ内のバッファのサイズおよびロケーションを定義します。ERXST で指定されるバイトと ERXND で指定されるバイトは両方とも FIFO バッファ内に含まれます。

イーサネット インターフェイスからバイト データを受信し、そのデータが順番に受信バッファへ書き込まれます。ただし、ERXND が指定するメモリ が書き込まれると、ハードウェアは自動的に次のデータをERXND が指定するメモリへ書き込みます。したがって、受信ハードウェアは、FIFO の境界を超えて書き込みを実行することはありません。

受信ロジックが無効の場合は、ホスト コントローラが ERXST および ERXND ポインタをプログラムできます。受信ロジックが有効のときに (ECON1.RXENが セットされている)、これらのポインタを変更してはいけません。変更した場合は、ポインタのメモリ範囲が 1FFFh から 0000h となり、1 つの FIFO として機能します。

ERXWRPTH:ERXWRPTL レジスタは、ハードウェアが 受信したバイトが書き込まれる FIFO 内の場所を示します。このポインタは読み出し専用で、新しいパケットが正常受信されるたびに自動的にアップデートされます。また、FIFO 内の空きスペースを確認するときにも使用されます。

ERXRDPT レジスタは、受信ハードウェアが書き込みを禁止される FIFO 内の場所を示します。通常動作の場合、受信ハードウェアは ERXRDPT で指定されるメモリ位置 (ERXRDPT が指定するアドレス は含まない)まで書き込みを実行します。 FIFO がフル状態のときに新しいデータが受信された場合、前のデータは上書きされません。その代わり、新しいデータを破棄して前のデータのみ保存します。新しいデータを継続的に受信する場合は、特定数のデータ受信プロセスが終了後に、ホストコントローラがこのポインタを定期的に移動させるように設定する必要があります。

#### 3.2.2 送信バッファ

8K バイトのメモリ内にあり、受信 FIFO バッファとしてプログラムされていない部分はすべて送信バッファ 領域となります。ホストコントローラが送信バッファ内のパケット配置を管理します。ホストコントローラがパケットを送信するとき、ETXST および ETXND ポインタを送信バッファ内のアドレスに配置します。ハードウェアには、開始アドレスと終了アドレスが受信バッファとオーバーラップしているかのチェック機能はありません。バッファの競合を回避するたットが出まび ETXND ポインタが受信バッファク接近した場合に、パケットを送信がないようにホストコントローラで制御する必要があります。詳細は、

**7.1** 「パケット送信」を参照してください。

#### 3.2.3 バッファの読み出しおよび書き込み

イーサネット バッファへのアクセスは、バッファ メモリの読み出し SPI コマンドおよび書き込み SPI コマンドを使用し、読み出しおよび書き込みごとのポインタ (ERDPT および EWRPT) を介してホストコントローラから行います。受信バッファからシーケンシャルに読み出しを続けると、受信バッファの最後で折り返しが生じます。一方、バッファへシーケンシャルに書き込みを実行する場合、折り返しは生じません。詳細は、4.2.2「バッファメモリ読み出しコマンド」および 4.2.4「バッファメモリ書き込みコマンド」を参照してください。

#### 3.2.4 バッファへの DMA アクセス

内蔵 DMA コントローラは、チェックサム計算する際にバッファから読み出しを実行し、メモリへコピーする際には、バッファへ書き込みおよび読み出しを実行する必要があります。 DMA の折り返し規則は、SPI アクセスと同様です。つまり、シーケンシャルに読み出しを続けると、受信バッファの最後で折り返しが生じます。すべての書き込み動作では、折り返しは生じません。詳細は、13.0「ダイレクトメモリアクセスコントローラ」を参照してください。

## イーサネット バッファの構成 図 3-2: 送信バッファの始点 0000h (ETXSTH:ETXSTL) バッファ書き込みポインタ 送信バッファ データ (EWRPTH:EWRPTL) AAh (WBM AAh) 送信 バッファ 送信バッファの終点 (ETXNDH:ETXNDL) 受信バッファの始点 (ERXSTH:ERXSTL) 受信 パッファ (循環 FIFO) バッファ読み出しポインタ 受信バッファ データ (ERDPTH:ERDPTL) 55h (RBM 55h) 受信バッファの終点 1FFFh (ERXNDH:ERXNDL)

#### 3.3 PHY レジスタ

PHY レジスタは、PHY モジュールのコンフィギュレーション、制御、および動作状態をモニタするレジスタです。すべての PHY レジスタは 16 ビット幅であり、合計 32 PHY アドレスあります。ただし、実装されているロケーションは9ビットのみです。実装されていないロケーションに書き込みを実行すると無視され、これらのロケーションから読み出しを実行すると0 だ読み出されます。すべての予約ロケーションは0として書き込みされています。これらのロケーションから読み出しを実行すると無視されます。

ETH、MAC、および MII 制御レジスタ、またはバッファメモリとは異なり、PHY レジスタへは、SPI 制御インターフェイスを介して直接アクセスできません。その代わり、MIIM (Media Independent Interface Management) として実装した特殊な MAC 制御レジスタセットからアクセスします。これらの制御レジスタは、MII レジスタと呼ばれています。レジスタ 3-3 およびレジスタ 3-4 に、PHY レジスタへのアクセス制御を行うレジスタを示します。

#### 3.3.1 PHY レジスタの読み出し

PHY レジスタを読み出す場合、全 16 ビットを取得します。

PHY レジスタから読み出しを実行する際のプロセスは、次のとおりです。

- 1. 読み出しを開始する PHY レジスタのアドレス を MIREGADR レジスタへ書き込む。

- 2. MICMD.MIIRD ビットをセットする。読み出し 動作が開始し、MISTAT.BUSY ビットがセット される。

- 3. 10.24μs 待機する。動作が完了したことを確認するため、MISTAT.BUSY ビットをポーリングする。ビジー状態の場合、ホスト コントローラは、MIISCAN 動作を始めたり MIWRH レジスタへの書き込みを実行してはいけません。

MAC がレジスタ コンテンツを取得すると、BUSY ビットが自動的にクリアされます。

- 4. MICMD.MIIRD ビットをクリアします。

- 5. MIRDL および MIRDH レジスタから任意の データを読み出します。これらのバイトへアク セスする順序は重要ではありません。

#### 3.3.2 PHY レジスタへの書き込み

PHY レジスタへ書き込みを実行する場合、全 16 ビットが一度に書き込まれます。選択したビットへの書き込みはできません。レジスタ内の特定ビットのみを再プログラムする必要がある場合は、まず、PHY レジスタの読み出しを実行し、出力データを編集した後、PHY レジスタへそのデータを書き戻します。

PHY レジスタへの書き込みを実行する際のプロセスは、次のとおりです。

- 1. 書き込みを開始する PHY レジスタのアドレス を MIREGADR レジスタへ書き込む。

- 書き込みデータの下位 8 ビットを MIWRL レジスタへ書き込む。

- 3. 書き込みデータの上位 8 ビットを MIWRH レジスタへを書き込む。このレジスタへの書き込み動作によって、MIIM 転送が自動的に開始され、MIWRL の後に書き込まれるので、MIWRL より後で書き込みを行わなければなりません。MISTAT.BUSY ビットがセットされる。

PHY レジスタの書き込みは、MIIM 動作が完了後に実行され、 $10.24\,\mu$  sec かかります。書き込み動作が完了すると、BUSY ビットが自動的にクリアされます。BUSY 状態のとき、ホストコントローラは、MIISCANを開始したり MIIRD 動作を実行してはいけません。

#### 3.3.3 PHY レジスタのスキャン

PHY レジスタで自動的に連続読み出し動作を実行するように、MAC で設定できます。これにより、定期的なステータス情報の更新が必要な場合、ホストコントローラでの負担を大幅に軽減できます。スキャン動作を実行する際のプロセスは次のとおりです。

- 1. 読み出しを実行する PHY レジスタのアドレス を MIREGADR レジスタへ書き込む。

- 2. MICMD.MIISCAN ビットをセットする。スキャン動作が開始し、MISTAT.BUSY ビットがセットされる。10.24μs 後に最初の読み出し動作が完了する。この動作がキャンセルされるまで、同じインターバルで順次に読み出し動作が実行される。最初の読み出し動作が完了した時点を確認するためには、MISTAT.NVALID ビットをポーリングする。

MIISCAN ビットを設定すると、MIRDL および MIRDH レジスタは自動的に  $10.24\mu s$  毎に更新されます。 MIRD レジスタが更新されたときを示すステータス情報はありません。 ホスト コントローラは、SPI を介して一回に 1 個の MII レジスタしか読み出しを実行しないため、PHY から同時に MIRDL と MIRDH の値が読み出されることはありません。

MIISCAN の動作中、ホスト コントローラは MIWRH への書き込み、または MIIRD 動作を開始してはいけません。 MIISCAN 動作をキャンセルする場合は、 MICMD.MIISCAN ビットをクリアして MISTAT.BUSY ビットをポーリングします。 BUSY ビットがクリアされると、新しい動作が開始できます。

表 3-3: ENC28J60 PHY レジスタのサマリ

| アドレス | レジスタ名   | ピット 15     | ピット 14        | ピット 13             | ピット 12 | ピット 11   | ピット 10 | ピット 9                  | ピット8                  | ピット7   | ピット6    | ピット 5  | ピット4   | ピット3                             | ピット 2  | ピット1   | ピット 0 | リセット値               |

|------|---------|------------|---------------|--------------------|--------|----------|--------|------------------------|-----------------------|--------|---------|--------|--------|----------------------------------|--------|--------|-------|---------------------|

| 00h  | PHCON1  | PRST       | PLOOPBK       | _                  | _      | PPWRSV   | r      | _                      | PDPXMD <sup>(1)</sup> | r      | _       | _      | _      | _                                | _      | 1      | _     | 00 00-q 0           |

| 01h  | PHSTAT1 | _          | _             | _                  | PFDPX  | PHDPX    | _      | ı                      | -                     | _      | _       | _      | _      | _                                | LLSTAT | JBSTAT | _     | 1 100-              |

| 02h  | PHID1   | PHY Identi | fier (OUI3:O  | UI18) = 008        | 3h     |          |        |                        |                       |        |         |        |        |                                  |        |        |       | 0000 0000 1000 0011 |

| 03h  | PHID2   | PHY Identi | fier (OUI19:0 | <b>OUI24)</b> = 00 | 00101  |          |        | PHY P/N (PP            | N5:PPN0) =            | = 00h  |         |        |        | PHY Revision (PREV3:PREV0) = 00h |        |        |       | 0001 0100 0000 0000 |

| 10h  | PHCON2  | _          | FRCLNK        | TXDIS              | r      | r        | JABBER | r                      | HDLDIS                | r      | r       | r      | r      | r                                | r      | r      | r     | -000 0000 0000 0000 |

| 11h  | PHSTAT2 | _          | _             | TXSTAT             | RXSTAT | COLSTAT  | LSTAT  | DPXSTAT <sup>(1)</sup> | _                     | _      | _       | PLRITY | _      | _                                | _      | _      | _     | 00 00d0             |

| 12h  | PHIE    | r          | r             | r                  | r      | r        | r      | r                      | r                     | r      | r       | r      | PLNKIE | r                                | r      | PGEIE  | r     | 0000 0000 0000 0000 |

| 13h  | PHIR    | r          | r             | r                  | r      | r        | r      | r                      | r                     | r      | r       | r      | PLNKIF | r                                | PGIF   | r      | r     | xxxx xxxx xx00 00x0 |

| 14h  | PHLCON  | r          | r             | r                  | r      | LACFG3:L | ACFG0  |                        |                       | LBCFG3 | :LBCFG0 | )      |        | LFRQ1:                           | LFRQ0  | STRCH  | r     | 0011 0100 0010 001x |

x= 不明、u = 変更なし、-- = 実装されていない、q = 条件に依存する値、r = 予約、変更不可 1: 二重モード / ステータス ビットの Reset 値は、LEDB ピンへの LED 接続によって異なります。詳細は、2.6 「LED コンフィギュレーション」を参照してください。

#### レジスタ 3-3: MICMD: MII コマンド レジスタ

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   | R/W-0 |

|-------|-----|-----|-----|-----|-----|---------|-------|

| _     | _   | _   | _   | _   | _   | MIISCAN | MIIRD |

| bit 7 |     |     |     |     |     |         | bit 0 |

記号:

R=読み出し可能なビット W=書き込み可能なビット U=未実装ビット、0 として読み出される -n=POR 後の値 1'=セット 0'=クリア x=不定

bit 7-2 **未実装ビット:** 0 が読み出される

bit 1 MIISCAN: MII スキャン イネーブル ビット

1 = MIREGADR の PHY レジスタが連続的に読み出され、データは MIRD に配置される

0 = MII スキャン動作なし

bit 0 MIIRD: MII 読み出しイネーブル ビット

1 = MIREGADR の PHY レジスタが 1 度読み出され、データは MIRD に配置される

0 = **MII** 読み出し動作なし

#### レジスタ 3-4: MISTAT: MII ステータス レジスタ

| U-0   | U-0 | U-0 | U-0 | R-0 | R-0    | R-0  | R-0   |

|-------|-----|-----|-----|-----|--------|------|-------|

| _     | _   | _   | _   | r   | NVALID | SCAN | BUSY  |

| bit 7 |     |     |     |     |        |      | bit 0 |

記号:

R=読み出し可能なビット W=書き込み可能なビット U=未実装ビット、0 として読み出される -n=POR 後の値 (1'=セット (0'=クリア x=不定

bit 7-4 **未実装ビット**:0 が読み出される

**bit 3 予約:** 0 を保持

bit 2 NVALID: MII マネージメント読み出しデータ無効ビット

1 = MIRD のコンテンツはまだ無効

0 = MII 読み出しサイクルが完了し、MIRD が更新された

bit 1 SCAN: MII マネージメント スキャン動作中ビット

1 = MII スキャン動作中 0 = MII スキャン停止中

bit 0 BUSY: MII マネージメント ビジー ビット

1 = PHY レジスタが読み出しまたは書き込み中

0 = MII インターフェイスはアイドル状態

#### 3.3.4 PHSTAT レジスタ

PHSTAT1 および PHSTAT2 レジスタには、読み出し専用ビットがあり、PHY モジュールの現在の動作ステータス (特に、ネットワークとのリンクが休止中のときの条件)を示します。

PHSTAT1 レジスタ (レジスタ 3-5) には、LLSTAT ビットがあります。レジスタの最後の読み出しが実行されてから物理層リンクが DOWN した場合に、このビットはクリアされて Low をラッチします。ホストコントローラで定期的なポーリングを使用して実行すれば、リンクエラーが生じた正確なタイミングを確認できます。特に、リンク変更割り込みを使用しない場合に有効です。

さらに、PHSTAT1 レジスタには、ジャバーステータスビットがあります。連続的にデータ送信を続けながらで停止せずその他のノードが媒体を共有することを許さないイーサネットコントローラのことを「ジャバリング (jabbering)」と言います。ジャバー状態とは、IEEE 規格で定義されている最大パケットサイズを大幅に超えていることを示します。このビットが High を保持しているときは、最後のレジスタ読み出しを実行後、ジャバー状態になったことを示します。

PHSTAT2 レジスタ (レジスタ 3-6) には、ステータス ビットがあり、PHY モジュールがネットワークに接続 して送信/受信が実行中であるかを示します。

#### 3.3.5 PHID1 および PHID2 レジスタ

PHID1 および PHID2 レジスタは、読み出し専用レジスタであり、定数データを保持してイーサネットコントローラの認識ができるためデバッグ用に使用されます。このレジスタに含まれる情報は次のとおりです。

- PHY モジュールの型番 (PPN5:PPN0)

- PHY モジュールのリビジョン レベル (PREV3:PREV0);

- PHY 識別コード、 マイクロチップ社の OUI (OUI3:OUI24)

PHY の型番およびリビジョンは、PHID2 に含まれます。PHY 識別コードの上位 2 バイトは、PHID1 に含まれ、残りのバイトは、PHID2 に含まれます。表 3-3 に、レジスタ内の正確なロケーションを示します。PHY 識別コードに含まれる 22 ビットの OUI (OUI3:OUI24、PHID1<15:0> および PHID2<15:10> に相当する )の先頭に、OUI1 および OUI2 として 2 文字の 「00」が結合され、全 OUI が生成されます。この結合した 24 ビットの文字列は、通常 16 進数で表されます。つまり、マイクロチップ テクノロジー社の OUI は、「0004A3h」となります。

リビジョン情報は、EREVID に含まれます。これは、 読み出し専用の制御レジスタで、5 ビットの識別コードでデバイスの特定シリコンのリビジョン レベルを 表します。表 3-2 に、このレジスタの詳細を示します。

#### レジスタ 3-5: PHSTAT1: 物理層ステータス レジスタ 1

| U-0    | U-0 | U-0 | R-1   | R-1   | U-0 | U-0 | U-0   |

|--------|-----|-----|-------|-------|-----|-----|-------|

| _      | _   | _   | PFDPX | PHDPX | _   | _   | _     |

| bit 15 |     |     |       |       |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/LL-0 | R/LH-0 | U-0   |

|-------|-----|-----|-----|-----|--------|--------|-------|

| _     | _   | _   | _   | _   | LLSTAT | JBSTAT | _     |

| bit 7 |     |     |     |     |        |        | bit 0 |

記号: '1'=セット

R = 読み出し専用ビット '0' = クリア U = 未実装ビット、0 として読み出される

-n = POR 後の値 RL=読み出し専用ラッチ ビット LL = Low をラッチするビット LH = High をラッチするビット

bit 15-13 **未実装ビット:** 0 が読み出される

bit 12 **PFDPX:** PHY 全二重可能ビット

1 = PHY は全二重通信で 10Mbps 動作が可能 (このビットは常にセット)

bit 11 PHDPX: PHY 半二重可能ビット

1 = PHY は半二重通信で 10Mbps 動作が可能 (このビットは常にセット)

bit 10-3 **未実装ビット**:0 が読み出される

bit 2 LLSTAT: PHY ラッチ リンク ステータス ビット

1 = PHSTAT1 の最後の読み出しから、リンクは継続的に正常動作状態

0 = PHSTAT1 の最後の読み出しから、リンクは切断しているか、していた状態

bit 1 JBSTAT: PHY ジャバー ステータス保持ビット

1 = PHSTAT1 の最後の読み出しから、送信はジャバー状態を検出した

0 = PHSTAT1 の最後の読み出しから、送信はジャバー状態を検出していない

bit 0 **未実装ビット:**0 が読み出される

#### レジスタ 3-6: PHSTAT2: 物理層ステータス レジスタ 2

| U-0    | U-0 | R-0    | R-0    | R-0     | R-0   | R-x                    | U-0   |

|--------|-----|--------|--------|---------|-------|------------------------|-------|

| _      | _   | TXSTAT | RXSTAT | COLSTAT | LSTAT | DPXSTAT <sup>(1)</sup> | _     |

| bit 15 |     |        |        |         |       |                        | bit 8 |

| U-0   | U-0 | R-0    | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|--------|-----|-----|-----|-----|-------|

| _     | _   | PLRITY | _   | _   | _   | _   | _     |

| bit 7 |     |        |     |     |     |     | bit 0 |

記号:

R=読み出し可能なビット W=書き込み可能なビット U=未実装ビット、0 として読み出される -n=POR 後の値 (1'=セット (0'=クリア x=不定

bit 15-14 **未実装ビット:**0 が読み出される

bit 13 TXSTAT: PHY 送信ステータス ビット

1 = PHY はデータを送信中

0 = PHY はデータを送信中ではない

bit 12 RXSTAT: PHY 受信ステータス ビット

1 = PHY はデータを受信中

0 = PHY はデータを受信中ではない

bit 11 COLSTAT: PHY 競合ステータス ビット

1 = 競合が発生 0 = 競合なし

bit 10 **LSTAT:** PHY リンク ステータス ビット (ラッチなし)

1 = リンクは正常0 = リンクは切断

bit 9 DPXSTAT: PHY 二重ステータス ビット (1)

1 = PHY は、全二重通信として設定 (PHCON1<8> をセット) 0 = PHY は、半二重通信として設定 (PHCON1<8> をクリア)

bit 8-6 **未実装ビット:**0 が読み出される

bit 5 **PLRITY:** 極性ステータス ビット

1 = TPIN+/TPIN- の信号極性は逆 0 = TPIN+/TPIN- の信号極性は正しい

bit 4-0 **未実装ビット:** 0 が読み出される

注 1: 二重モード / ステータス ビットの Reset 値は、LEDB ピンへの LED 接続によって異なります。詳細は、2.6 「LED コンフィギュレーション」を参照してください。

### 4.0 シリアル ペリフェラル インター フェイス (SPI)

#### 4.1 概要

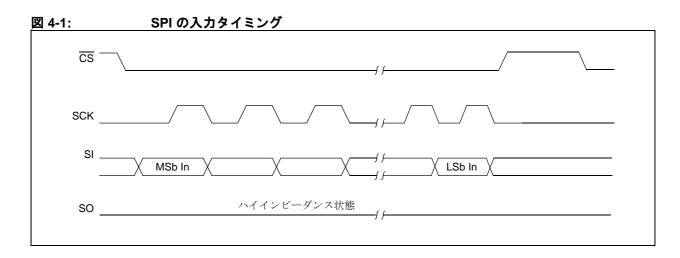

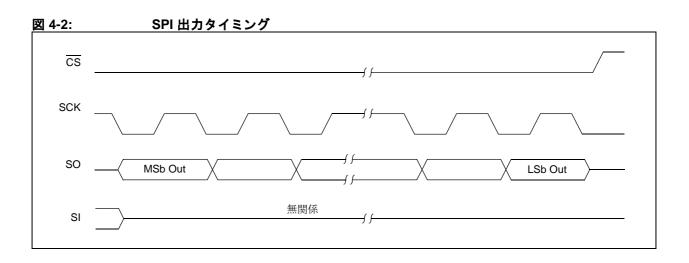

ENC28J60 は、多くのマイクロコントローラに付いているシリアルペリフェラルインターフェイス (SPI)ポートと直接インターフェイスできます。このデバイスは、SPI

モード 0,0 にのみ対応しています。また、SPI ポートでは、SCK ピンが Low ステートでアイドルになる必要があります。クロック極性の選択はできません。

コマンドおよびデータは、SIピンを介して入力され、SCK クロックの立ち上がりエッジでデータを取得します。 ENC28J60 からの出力データは、SOピンを介して、SCK の立ち下がりエッジで出力されます。動作中、CSピンは Low 駆動し、動作が完了したら High に戻します。

© 2006 Microchip Technology Inc. Preliminary DS39662B\_JP-page 25

#### 4.2 SPI 命令セット

ENC28J60 の動作は、SPI で接続されている外部ホストコントローラから与えられるコマンドに依存します。 これらのコマンドは 1 バイト以上で構成され、制御メモリおよびイーサネット バッファ空間へアクセスするのに使用されます。通常、3 ビットの Opcode およびレ ジスタ アドレスまたはデータ定数を特定する 5 ビットの引数で構成されています。書き込みおよびビットフィールド命令も 1 バイト以上のデータが続きます。合計 7 つの命令が、ENC28J60 に実装されています。表 4-1 に、すべての動作のコマンド コードを示します。

表 4-1: ENC28J60 の SPI 命令セット

| 命令の名前と省略記号          |   | パイト 0 |    |    |    |    |   | バイト 1 およびそれ以降 |     |     |   |    |    |   |   |   |

|---------------------|---|-------|----|----|----|----|---|---------------|-----|-----|---|----|----|---|---|---|

|                     |   | рсо   | de |    |    | 引数 |   |               |     |     |   | デー | -タ |   |   |   |

| 制御レジスタ読み出し (RCR)    | 0 | 0     | 0  | а  | a  | a  | а | a             |     | N/A |   |    |    |   |   |   |

| バッファ メモリ読み出し (RBM)  | 0 | 0     | 1  | 1  | 1  | 0  | 1 | 0             | N/A |     |   |    |    |   |   |   |

| 制御レジスタ書き込み (WCR)    | 0 | 1     | 0  | а  | a  | а  | а | a             | d   | d   | d | d  | d  | d | d | d |

| バッファ メモリ書き込み (WBM)  | 0 | 1     | 1  | 1  | 1  | 0  | 1 | 0             | d   | d   | d | d  | d  | d | d | d |

| ビット フィールド セット (BFS) | 1 | 0     | 0  | a  | a  | а  | a | a             | d   | d   | d | d  | d  | d | d | d |

| ビット フィールド クリア (BFC) | 1 | 0     | 1  | а  | a  | а  | а | a             | d   | d   | d | d  | d  | d | d | d |

| システム リセット コマンド      | 1 | 1     | 1  | 1  | 1  | 1  | 1 | 1             |     |     |   | N  | /A |   |   |   |

| (ソフト リセット) (SRC)    |   | 1     | 1  | Т. | т_ | Т  | Т | т             |     |     |   | IN | ^  |   |   |   |

**記号:** a=制御レジスタアドレス、d=データペイロード

#### 4.2.1 制御レジスタ読み出しコマンド

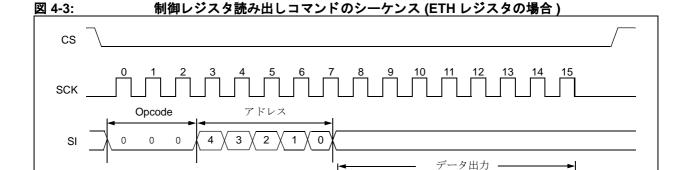

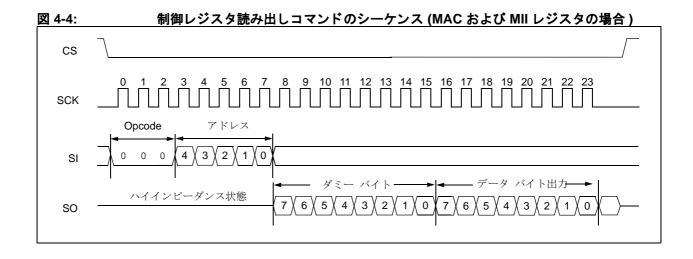

制御レジスタ読み出し (RCR) コマンドにより、ホストコントローラが ETH、MAC、および MII レジスタを任意の順序で読み出すことができます。PHY のコンテンツは、特殊な MII レジスタ インターフェイスを介して読み出されます (詳細は、3.3.1「PHY レジスタの読み出し」を参照)。

RCR コマンドは、 $\overline{\text{CS}}$  ピンを Low に駆動すると開始されます。そして RCR Opcode が ENC28J60 に送信され、続いて 5 ビットのレジスタ アドレス (A4  $\sim$  A0) が送信されます。この 5 ビット アドレスで、現在のバン

ハイインピーダンス状態

SO

クにある 32 制御レジスタのどれかを特定します。5 ビット アドレスが ETH レジスタを指定する場合は、 選択したレジスタにあるデータが直ぐ MSB 順に SO ピンからシフト アウトされます。図 4-3 に、これらの レジスタの読み出しシーケンスを示します。

このアドレスが MAC または MII レジスタを指定する場合は、最初にダミー バイトが SO ピンから出力されます。そのダミー バイトの後に、データが MSB 順にSO ピンからシフト アウトされます。 CS ピンが Highになると、RCR 動作が終了します。図 4-4 に、MAC および MII レジスタの読み出しシーケンスを示します。

2

3

0

5

6

© 2006 Microchip Technology Inc. Preliminary DS39662B\_JP-page 27

#### 4.2.2 バッファ メモリ読み出しコマンド

読み出しバッファ メモリ (RBM) コマンドにより、送信と受信バッファ メモリが統合した 8K バイトのメモリからバイト データを読み出すことができます。

ECON2 レジスタの AUTOINC ビットがセットされている場合、各バイトの最後のビットが読まれると、ERDPT ポインタが自動的に次のアドレスへインクリメントします。通常、次のアドレスとは、現在のアドレスに 1 をインクリメントしたアドレスになります。ただし、受信バッファの最後のバイトが読み出された場合 (ERDPT = ERXND) は、ERDPT ポインタが受信バッファの開始点 (ERXST) へ変更されます。この機能により、ホストコントローラは、折り返しするタイミングをモニタする必要なしに、連続的に受信バッファからパケットを読み出すことが可能です。アドレス1FFFh が読み出されるときに AUTOINC がセットされており、ERXND がこのアドレスを指定しない場合は、読み出しポインタはインクリメントして 0000h にへ折り返します。

でSピンを Low にすると、RBM コマンドが開始されます。RBM Opcode が ENC28J60 へ送信され、続いて 5 ビットの定数 1Ah が送信されます。RBM コマンドと 定数が送信された後に、ERDPT で指定されたメモリアドレスのデータが、SOピンから MSB順にシフトアウトされます。ホストコントローラが連続的に SCLピンにクロックを供給し、でSピンを High にしない限り、ERDPT で指定されたバイト データが SOピンから MSB順にシフトアウトします。このように、AUTOINCが有効の場合は、その他の SPI コマンドを使用せずに、バッファメモリから連続的にバイト データを読み出すことができます。RBM コマンドは、でSピンを Highにすると無効になります。

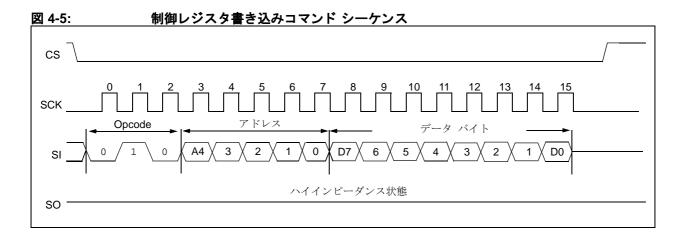

#### 4.2.3 制御レジスタ書き込みコマンド

制御レジスタ書き込み (WCR) コマンドにより、ホストコントローラが、ETH、MAC、および MII レジスタへ任意の順番で書き込みできます。PHY レジスタへの書き込みは、特殊な MII レジスタ インターフェイスを介して実行されます (詳細は、3.3.2「PHY レジスタへの書き込み」を参照)。

WCR コマンドは、 $\overline{\text{CS}}$  ピンを Low にすると開始されます。WCR Opcode が ENC28J60 へ送信され、続いて 5 ビットのレジスタ アドレス (A4  $\sim$  A0) が送信されます。この 5 ビット アドレスで、現在のバンクにある 32 制御レジスタのどれかを認識します。WCR コマンドとアドレスが送信された後、実際に書き込まれるデータが MSB 順に送信されます。このデータは、SCK の立ち上がりエッジで、アドレス指定されたレジスタへ書き込まれます。

CS ピンを High にすると WCR 動作は停止します。8 ビットがロードされる前に CS ピンを High にした場合 は、そのバイト データに対する書き込みが中断されま す。バイト書き込みシーケンスのタイミングの詳細は、 図 4-5 を参照してください。

#### 4.2.4 バッファ メモリ書き込みコマンド

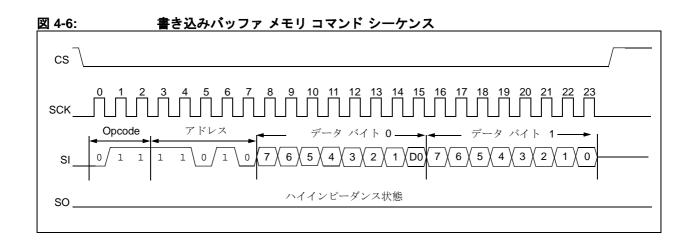

バッファメモリ書き込み (RBM) コマンドにより、送信と受信バッファメモリが統合した 8K バイトのメモリヘホスト コントローラがバイト データを書き込むことができます。

ECON2 レジスタで AUTOINC ビット がセット されている場合、各バイトの最後のビット が書き込まれた後、EWRPT ポインタが自動的にインクリメント されて次のアドレス (現在のアドレス +1)を指定します。AUTOINC がセット されていて、アドレス 1FFFh が書き込まれた場合は、書き込みポインタが 0000h ヘインクリメントされます。

でSピンを Low にすると WBM コマンド が開始されます。まず WBM Opcode が ENC28J60 へ送信され、続いて5ビットの定数 1Ah が送信されます。WBM コマンドと定数が送信された後に、EWRPT が指定するメモリに格納されるデータが、ENC28J60 へ MSB 順にシフトアウトされます。AUTOINC がセットされている場合、8ビットのデータが受信されると、書き込みポインタは自動的にインクリメントされます。CSピンを High にしない限り、ホストコントローラは SCKピンにクロックを供給し、SIピンにデータを送信すれば連続的にメモリへ書き込みを実行できます。このように、AUTOINCが有効の場合は、その他の SPIコマンドを使用することなく連続的にバッファメモリへバイト データを書き込みできます。

CS ピンを High にすると WBM コマンド は無効になります。図 4-6 に、書き 込みシーケンスの詳細を示します。

#### 4.2.5 ビット フィールド セット コマンド

ビット フィールド セット (BFS) コマンドにより、ETH 制御レジスタの中の最大 8 ビット までをセット できます。このコマンドは、MAC レジスタ、MII レジスタ、PHY レジスタ、またはバッファ メモリ では使用できません。BFS コマンドは、提供されたデータ バイトを使用し、アドレス指定されたレジスタ コンテンツとのビット OR を実行します。

CSピンを Low にすると、BFSコマンドが開始されます。まずは BFS Opcode が送信され、続いて 5ビットのアドレス  $(A4 \sim A0)$  が送信されます。この 5ビットアドレスで現在のバンク内にある ETH レジスタのどれかを認識します。BFS コマンドとアドレスが送信された後に、ビットフィールドセット情報を含むデータバイトがMSB順に送信されます。EFS DO ビットの EFS SCK 信号の立ち上がりエッジで、提供されたデータとアドレス指定されたレジスタデータの EFS OR がとられます。

8ビットがロードされる前に CS ピンが High になると、 そのバイト データに対する動作が中断されます。BFS 動作を終了するには、CS ピンを High にします。

#### 4.2.6 ビット フィールド クリア コマンド

ビット フィールド クリア (BFC) コマンドにより、ETH レジスタにある最大 8ビットをクリアできます。このコマンドは、MAC レジスタ、MII レジスタ、PHY レジスタ、またはバッファメモリでは使用できません。BFC コマンドは、提供されたデータ バイトとアドレス指定されたレジスタ コンテンツとのビット 毎の NOTAND動作をします。たとえば、あるレジスタコンテンツがFIh のとき、オペランド 17h を使用して BFC コマンドを実行すると、このレジスタコンテンツは EOh に変更されます。

$\overline{\text{CS}}$  ピンを Low にすると、BFC コマンド が開始されます。まず BFC Opcode が送信され、続いて 5 ビット のアドレス (A4  $\sim$  A0) が送信されます。この 5 ビット アドレスで、現在のバンクの中にある ETH レジスタのどれかを認識します。BFC コマンドとアドレスが送信された後、ビット フィールド クリア情報を含むデータ バイトが MSB 順に送信されます。D0 ビットの SCK 信号の立ち上がり エッジで、提供されたデータが反転され、そしてアドレス指定されたレジスタ データとの AND がとられます。

CSピンを High にすると BFC 動作が終了します。8ビットがロードされる前に CSピンが High になると、そのデータ バイト に対する動作は中断されます。

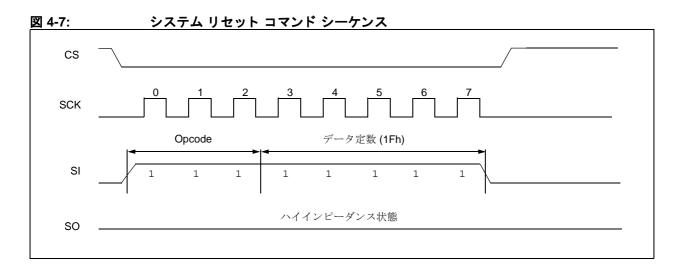

#### 4.2.7 システム リセット コマンド

システム リセット コマンド (SRC) により、ホスト コントローラがシステム ソフト リセット コマンドを実行できます。SRC は、ほかの SPI コマンドとは異なり、シングル バイトで構成され、レジスタに対しては実行できません。

$\overline{\text{CS}}$  ピンを Low にすると、SRC コマンドが開始されます。そして SRC Opcode が送信され、続いて 5 ビット 0 ソフト リセット コマンド定数 1Fh が送信されます。 $\overline{\text{CS}}$  ピンを High にすると SRC 動作が停止します。

図 4-7 に、システム リセット コマンド シーケンスの詳細を示します。 SRC のソフト リセットの詳細は、11.2「システム リセット」を参照してください。

#### 5.0 イーサネットの概要

ENC28J60 をイーサネット インターフェイスとして 使用する方法について説明する前に、標準的なデータフレーム構造について復習します。詳細情報が必要な方は、イーサネット プロトコルの基本となる IEEE 規格 802.3 を参照してください。

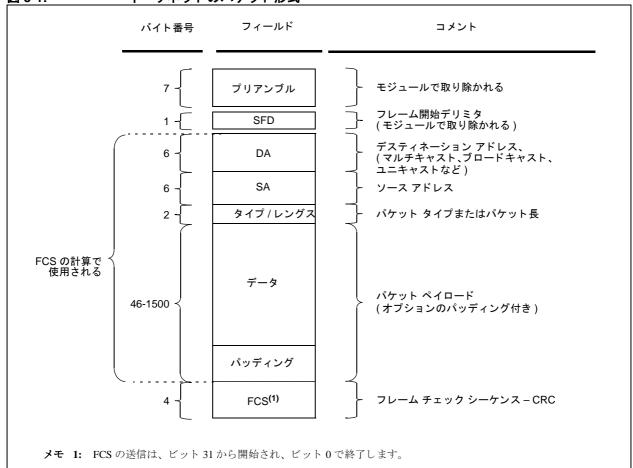

#### 5.1 パケット形式

標準的な IEEE 802.3 準拠のイーサネット フレーム長は、 $64 \sim 1518$  バイトです。これらは 5 つまたは 6 つのセクション (デスティネーション MAC アドレス、ソース MAC アドレス、タイプ / レングス フィールド、データ ペイロード、オプションのパッディングフィールド、および巡回冗長チェック (CRC)) で構成されています。さらに、イーサネット媒体で送信されるとき、7 バイトのプリアンブルおよび SFD (フレー

ム開始デリミタ)バイトがイーサネット パケットの最初に追加されます。図 5-1 に、ツイスト ペア ケーブルでのパケット形式を示します。

## 5.1.1 プリアンブル /SFD (フレーム開始デリミタ)

プリアンブル バイトおよびフレーム開始デリミタ バイトは、ENC28J60 がデータの送受信を行うときに自動で生成されます。またはこれらは送受信されるときにパケットから自動で切り離されます。ホストコントローラはこれらのバイトに関して何もする必要はありません。また、ENC28J60 は送信時にパッディングやCRC チェックも自動生成し、受信時に検証しますので、通常、ホストコントローラはこれらのバイトに関しても何もする必要はありません。ただし、パッディングおよびCRC フィールドは、パケット受信時に受信バッファに書き込まれるため、必要に応じて、ホストコントローラでこれらを検証することが可能です。

#### 図 5-1: イーサネットのパケット形式

#### 5.1.2 デスティネーション アドレス

デスティネーション アドレス フィールド は 6 バイト あり、パケット が送られるデバイスの MAC アドレスが配置されています。 MAC アドレスの最初のバイトの LSB がセットされている場合は、マルチキャスト デスティネーション アドレスです。たとえば、01-00-00-00-F0-00 および33-45-67-89-AB-CD はマルチキャスト アドレスです。一方、00-00-00-00-F0-00 および32-45-67-89-AB-CD はマルチキャスト アドレスではありません。

マルチキャスト デスティネーション アドレスを持つパケット は、特定のイーサネット ノード グループへ送信されます。デスティネーション アドレス フィールド が予約のマルチキャスト アドレス FF-FF-FF-FF-FFの場合、パケット はブロードキャスト パケットとなり、ネットワークを共有するノード グループへ送信されます。MACアドレスの最初のバイトの LSB がクリアされると、このアドレスはユニキャスト アドレスとなり、アドレス指定した1つのノードのみに送信されます。

ENC28J60には受信フィルタが内蔵されているため、マルチキャスト、ブロードキャスト、またはユニキャストデスティネーションアドレスを持つパケットを破棄/受信できます。パケット送信する場合は、ホストコントローラが相手のデスティネーションアドレスを送信バッファへ書き込む必要があります。

#### 5.1.3 ソース アドレス

ソースアドレスフィールドは6バイトあり、イーサネットパケットを作成したノードのMACアドレスが配置されています。ENC28J60ユーザーは、使用する各コントローラ用に専用のMACアドレスを生成する必要があります。

MACアドレスは2つに分けられます。始めの3バイトは、OUI (Organizationally Unique Identifier)と呼ばれる固有の番号であり、IEEEで承認されて与えられます。残りの3バイトは、OUIを購入したメーカーが任意で与えることができるアドレスバイトです。

パケット送信時に、ホストコントローラによって、割り当てられたソース MAC アドレスを送信バッファへ書き込む必要があります。ENC28J60は、ユニキャスト受信フィルタ用に使用される MAADR レジスタのコンテンツを自動送信しません。

#### 5.1.4 タイプ/レングス

タイプ / レングス フィールド は 2 バイト であり、送信されるパケット データが属するプロトコルを定義します。このフィールドに 05DCh (1500) またはそれより 小さい値が配置されている 場合、このフィールドはレングスフィールドとして考えられ、データ フィールド内にあるデータ長(パッディング データを含まない)を示しています。独自のネットワークを実装しているユーザーは、このフィールドをレングスフィールドとして使用することができます。一方、IP (インターネットプロトコル) などのプロトコルを実装しているアプリケーションの場合は、パケット送信時にプロトコルの仕様で定義されている適切なタイプをこのフィールドにプログラムする必要があります。

#### 5.1.5 データ

データフィールドは、 $0 \sim 1500$  バイトまでの可変長フィールドです。大規模データパケットは、イーサネット規格に違反し、ほとんどのイーサネットノードで破棄されます。しかしながら、ENC28J60の場合は大規模フレームイネーブルビット (MACON3.HFRMEN=1)をセットすると、大規模パケットの送受信が可能になります。

#### 5.1.6 パッディング

パッディングフィールドは、短いデータペイロードが使用されるときに、IEEE 802.3 仕様を満たすために追加される可変長フィールドです。イーサネットパケットのデスティネーション、ソース、タイプ、データ、およびパッディングは、60 バイト以上でなければなりません。4 バイトの CRCフィールドを追加すると、パケットは64 バイト以上になります。データフィールドが46 バイトに満たない長さの場合は、パッディングフィールドが必要になります。

ENC28J60 のパケット 送信で、MACON3.PADCFG<2:0> が 設定されている場合は、自動的に 0 の値のパッディング ビット を追加します。設定されていない場合は、パケット 送信前にホスト コントローラでパッディングを手動追 加する必要があります。ENC28J60 は、短いパケットを送信する際に、ホスト コントローラへ適切な措置をさせるコマンド命令を出しません。

ENC28J60 のパケット 受信では、18 バイト に満たないパケット を自動的に拒否します。つまり、このサイズのパケット は、通常必要とされる最小限のソースおよびデスティネーション アドレス、タイプ情報、FCS チェックサムが含まれていないものだと 判断されます。18 バイト以上のすべてのパケット は、標準的な受信フィルタの基準に従って受信されます。IEEE 802.3 に準拠すさせるには、すべての受信パケットをアプリケーションでチェックし、64 バイトに満たないパケットを受信拒否する必要があります。

#### 5.1.7 CRC

CRCフィールドは4バイトであり、デスティネーション、ソース、タイプ、データ、およびパディングフィールドにあるデータを計算した、業界標準の32ビット CRC が含まれています。

パケット 受信時に、ENC28J60 は入力されるパケットの CRC をチェックします。ERXFCON.CRCEN がセットされている場合、無効な CRC 値があるパケット は自動的に破棄されます。CRCEN がクリアされ、パケット がその他の 受信フィルタの基準を満たした場合、そのパケット は受信バッファへ書き込まれます。そしてホスト コントローラは受信ステータス ベクタを読み出して CRC が有効であるかを判断します(詳細は、7.2「パケット 受信」を参照)。

パケット送信時、MACON3.PADCFG<2:0>ビットがセットされている場合は、ENC28J60が自動的に有効な CRCを生成します。セットされていない場合は、ホストコントローラでCRCを生成して送信バッファ内に配置する必要があります。CRC計算の複雑性を考慮すると、ENC28J60は自動的にCRCフィールドを生成できるため、できる限り PADCFGビットをセットすることを推奨します。

#### 6.0 初期化

ENC28J60 を使用してパケットを送信および受信する前に、特定デバイスの設定を初期化する必要があります。アプリケーションによっては、コンフィギュレーション オプションを変更する必要があります。通常、これらのタスクはリセット後に1度行うだけで、その後変更する必要はありません。

#### 6.1 受信バッファ

パケットを受信する前に、ERXST および ERXND ポインタをプログラムして受信バッファを初期化する必要があります。ERXST および ERXND アドレスを含む、この 2 つのアドレス間のすべてのメモリは、受信ハードウェア用となります。ERXST ポインタは、偶数アドレスでプログラムすることを推奨します。

大容量データおよび頻繁なパケット送受信を扱うアプリケーションの場合は、大半のメモリを受信バッファとして確保します。古いパケットを保存する必要がない場合、あるいは複数の送信パケットを使うようなアプリケーションの場合は、メモリ確保を少なくします。

ERXST または ERXND ポインタをプログラミングすると、ERXWRPT レジスタの内部ハードウェア コピーが自動的に ERXST の値で更新されます。この値は、受信ハードウェアが受信データを書き込む際の開始位置として使用されます。ERXWRPT は、新しいパケットが問題なく受信されたときのみ、ハードウェアによって更新されます。

注: ERXST または ERXND への書き込み後すぐには、ERXWRPT レジスタは更新されません。ERXWRPT レジスタの内部ハードウェア コピーのみ更新されます。したがって、ファームウェアの初期化ルーチンでは、ERXWRPT = = ERXST という関係は成り立ちません。

トラッキング用として、ERXRDPT レジスタも同じ値で プログラムする必要があります。ERXRDPT をプログラ ムするには、ホストコントローラがまず ERXRDPTL へ 書き込みを実行し、次に ERXRDPTH へ書き込みます。 詳細は、7.2.4「受信バッファのスペースを開放する」を 参照してください。

#### 6.2 送信バッファ

受信バッファとして使用されないすべてのメモリは、 送信バッファとなります。送信されるデータは、未使 用スペース内に書き込まれる必要があります。パケット送信後、ハードウェアがバッファメモリに7バイト のステータス ベクタを書き込むため、ホスト コントローラは各パケットの最後と受信バッファの最初の間を7バイト以上空けておく必要があります。送信バッファの初期化は自動的に実行されます。

#### 6.3 受信フィルタ

ERXFCON レジスタを適切に設定して、受信フィルタを有効または無効にする必要があります。設定方法は、8.0「受信フィルタ」を参照してください。

#### 6.4 OST を待機する

POR 後、すぐに初期化プロセスが実行されます。MAC および PHY レジスタを編集する前に十分な時間が経過していることを確認するため、ESTAT.CLKRDY ビットをポーリングする必要があります。OST の詳細は、2.2「オシレータ スタートアップ タイマ」を参照してください。

© 2006 Microchip Technology Inc. Preliminary DS39662B\_JP-page 33

#### 6.5 MAC 初期化設定

いくつかの MAC レジスタでは、初期化中にコンフィギュレーションが必要です。これは 1 回のみ必要であり、プログラミング順序は特に指定されていません。

- 1. MACON1 の MARXEN ビットを設定して、MAC がフレームを受信できるようにします。全 二重を使用する場合、通常アプリケーションでは TXPAUS と RXPAUS も設定して、IEEE で定義されたフロー制御が機能するようにします。

- 2. MACON3 の PADCFG、TXCRCEN、および FULDPX ビットを設定します。通常のアプリケーションでは、最小 60 バイトの自動パッディングを有効にし、常に有効な CRC を追加します。便宜上、多くのアプリケーションでは FRMLNEN ビットも設定し、フレーム長のステータス レポートを有効にします。アプリケーションが全二重としてコンフィギュレーションされたリモート ノードと接続する場合は、FULDPX ビットを設定する必要があります。そうでない場合、このビットを設定する必要はありません。

- 3. MACON4 のビットを設定します。IEEE 802.3 規格に準拠するように、DEFER ビットを設定

します。

- 4. 受信 / 送信時に許容する最大フレーム長を MAMXFL レジスタにプログラムします。通常 のネットワーク ノードは、1518 バイト以下の パケットを送受信できます。

- 5. MABBIPG に連続パケット間のギャップを設定 します。通常のアプリケーションでは、全二重 を使用する場合は 15h、半二重を使用する場合 は 12h を設定します。

- 6. MAIPGL レジスタに非連続パケット間のギャップを設定します。通常のアプリケーションでは、12h を設定します。

- 7. 半二重を使用する場合は、MAIPGHを設定する 必要があります。通常のプリケーションでは、 OChを設定します。

- 8. 半二重を使用する場合は、MACLCON1 および MACLCON2 レジスタに再送と衝突の遅延を設 定します。通常のアプリケーションでは、デフォルトの Reset 値をそのまま使用しますが、特に 長いケーブルの場合は、MACLCON2 のデフォルト値を大きくする必要があります。

- 9. MAADR1:MAADR6 レジスタにローカル MAC アドレスをプログラムします。

レジスタ 6-1: MACON1: MAC 制御レジスタ 1

| U-0   | U-0 | U-0 | R-0 | R/W-0  | R/W-0  | R/W-0   | R/W-0  |

|-------|-----|-----|-----|--------|--------|---------|--------|

| _     | _   | _   | r   | TXPAUS | RXPAUS | PASSALL | MARXEN |

| bit 7 |     |     |     |        |        |         | bit 0  |

#### 記号:

R=読み出し可能なビット W=書き込み可能なビット U=未実装ビット、0 として読み出される -n=POR 後の値 '1'=セット '0'=クリア x=不定

**bit 7-5 未実装ビット**: 0 が読み出される

bit 4 **予約:**0 を保持する

bit 3 TXPAUS: ポーズ制御フレーム送信イネーブル ビット

1 = MAC がポーズ制御フレームを送信する (全二重のフロー制御に必要)

0 = ポーズ フレームを送信しない

bit 2 RXPAUS: ポーズ制御フレーム受信イネーブル ビット

1 = ポーズ制御フレームの受信時に、送信を禁止する(通常動作)

0 = 受信するポーズ制御フレームを無視する

bit 1 PASSALL: パス オール受信フレーム イネーブル ビット

1 = フィルタかけられていない場合、MAC で受信された制御フレームはすべて受信バッファへ書き 込まれる

0 = MAC で処理された後、制御フレームは破棄される (通常動作)

bit 0 MARXEN: MAC 受信イネーブル ビット

1 = MAC がパケットを受信する 0 = パケットを受信しない

#### レジスタ 6-2: MACON3: MAC 制御レジスタ 3

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0   | R/W-0  |

|---------|---------|---------|---------|--------|--------|---------|--------|

| PADCFG2 | PADCFG1 | PADCFG0 | TXCRCEN | PHDREN | HFRMEN | FRMLNEN | FULDPX |

| bit 7   |         |         |         |        |        |         | bit 0  |

#### 記号:

R =読み出し可能なビット W =書き込み可能なビット U =未実装ビット、0 として読み出される -n = POR 後の値 (1' =セット (0' = ) (0' = ) (0' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' = ) (1' =

- bit 7-5 PADCFG2:PADCFG0: 自動パッドおよび CRC コンフィギュレーション ビット

- 111 = すべての短いフレームは、60 バイトになるまで 0 値がパッディングされ、有効な CRC が追加される

- 110 = 短いフレームの自動パッディングは無効

- 101 = MAC が、8100h タイプ フィールドがある VLAN プロトコルを自動検出し、64 バイトまでの自動パッディングを行う。フレームが VLAN フレームでない場合は、そのフレームに 60 バイトまでのパッディングが行われる。パッディング後に有効な CRC が追加される

- 100 = 短いフレームの自動パッディングは無効

- 011 = すべての短いフレームは、64 バイト になるまで 0 値がパッディングされ、有効な CRC が追加される

- 010 = 短いフレームの自動パッディングは無効

- 001 = すべての短いフレームは、64 バイト になるまで 0 値がパッディングされ、有効な CRC が追加される

- 000 = 短いフレームの自動パッディングは無効

- bit 4 TXCRCEN: 送信 CRC イネーブル ビット

- 1 = PADCFG に関わらず、MAC は送信されたすべてのフレームに有効な CRC を追加する。 PADCFG で CRC が追加されるように設定している場合は、TXCRCEN を必ずセットする

- 0 = MAC は CRC を追加しない。最後の 4 バイトが有効な CRC であるかをチェックし、異常なら 送信ステータス ベクタにレポートする

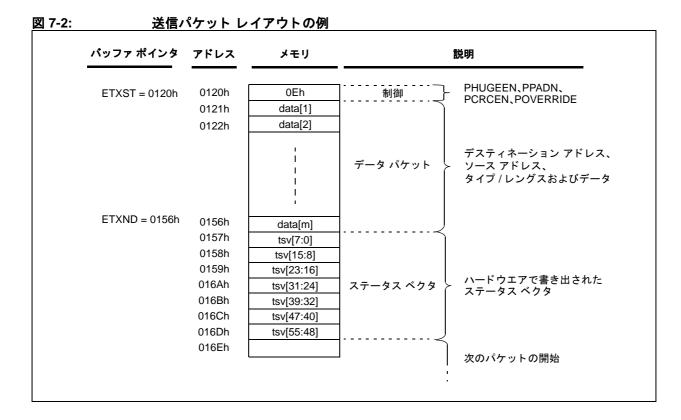

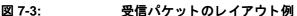

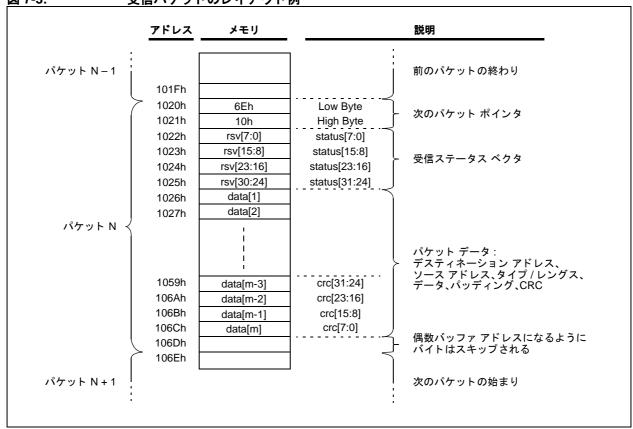

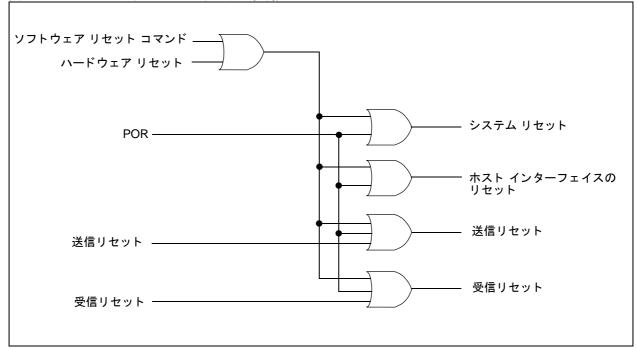

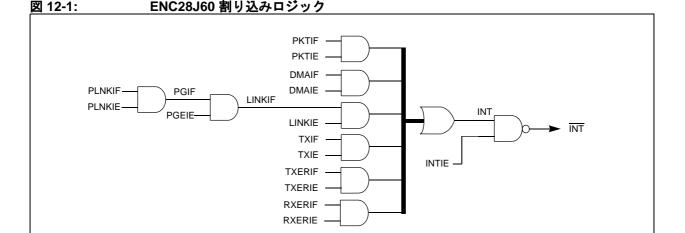

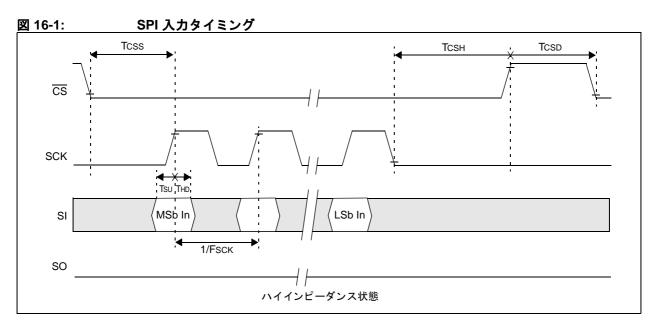

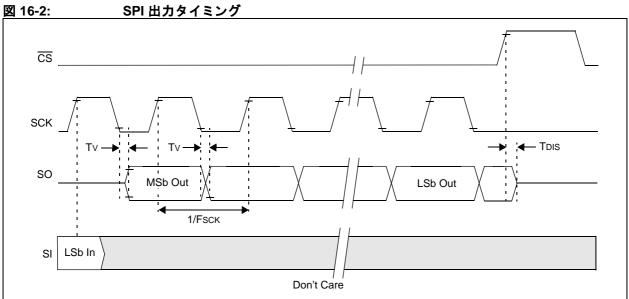

- bit 3 **PHDREN:** 独自 (Proprietary) ヘッダ イネーブル ビット