RE01 グループ (256 KB フラッシュメモリ搭載製品) ルネサスマイクロコントローラ

R01DS0369JJ0100 Rev.1.00 Apr 3, 2020

64 MHz, 32 ビット Arm® Cortex®-M0+, 256 KB フラッシュメモリ、128 KB SRAM、エナジーハーベスト制御回路、MIP 液晶 コントローラ、2D グラフィックエンジン、超低消費電力 14 ビット A/D コンバータ、VREF 回路、RTC、サブクロック補正回路(論理緩急)、セキュリティ機能(オプション)、SPI、Quad SPI

#### ■ Arm Cortex-M0+コア内蔵

- 最高動作周波数:64 MHz

- Arm®メモリプロテクションユニット:8領域 (Arm MPU)

- CoreSight<sup>™</sup>デバッグポート:SW-DP

#### ■ 消費電力低減機能

- SOTB<sup>™</sup>プロセス技術を用いたバックバイアス電圧制御機能

- 1.62 V~3.6 V の超低電圧動作が可能

- ●動作周波数に応じた3種類の電力制御モードをサポート ●4種類の低消費電力モードをサポート

- 3 種類の電源供給モードをサポート

#### ■ 内蔵コードフラッシュメモリ

- 256 KB のコードフラッシュメモリ

- 32 MHz 以下では 0 ウェイト、32 MHz より速い場合には 1 ウ

- エリアプロテクション機能により誤書き換え、改ざんを防止

#### ■ 内蔵 SRAM

● 128 KB の 0 ウェイトアクセス SRAM

#### ■ データ転送機能

DMAC: 4 チャネル DTC:1チャネル

#### ■ リセットおよび電源電圧制御

- パワーオンリセット (POR)

- 低電圧検出機能 (LVD) の設定可能

### ■ マルチクロックソース

- 外部水晶発振 (メインクロック): 8~32 MHz

- ↑ 「中の下記を扱く (ハインノレーノン)」、8 32 (MIL)

・ 外部水晶発振(サプクロック): 32.768 kHz

・ 高速オンチップオシレータ (HOCO): 24/32/48/64 MHz

- 独立ウォッチドッグタイマ用オシレータ:16 kHz

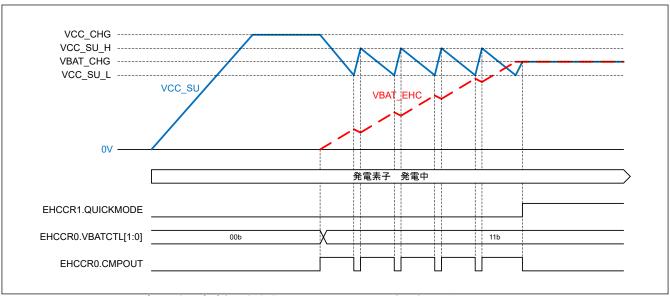

#### ■ エナジーハーベスト制御

- 発電素子との直接接続可能

- 二次電池の充電を待たずに高速起動が可能二次電池過去量性止機器

- 二次電池過充電防止機能

### ■ 独立ウォッチドッグタイマ

● 14 ビットカウンタ、16 kHz (LOCO クロックの 1/2) 動作

### ■ サブクロック補正回路

- 16 秒周期で発振精度補正が可能(論理緩急機能)● ディープソフトウェアスタンバイモード時にも 1 秒周期のイベント生成可能

#### ■ 通信機能

- SPI×2 チャネル 最大 8 コマンド/128 ビットバッファタイプ×1 チャネル 1 コマンド/32 ビットバッファタイプ×1 チャネル

Quad SPI×1 チャネル (外付けフラッシュメモリの接続が可

- 1²C バスインタフェース×2 チャネル

シリアルコミュニケーションインタフェース (SCIg)×5 チャ ネル

調歩同期式/クロック同期式/簡易 I<sup>2</sup>C/簡易 SPI/スマートカードインタフェース/IrDA インタフェース (バージョン 1.0) に対応 (SCI0 のみ)

● FIFO 付きシリアルコミュニケーションインタフェース (SCIi) × 2 チャネル (FIFO サイズは 16 バイト)

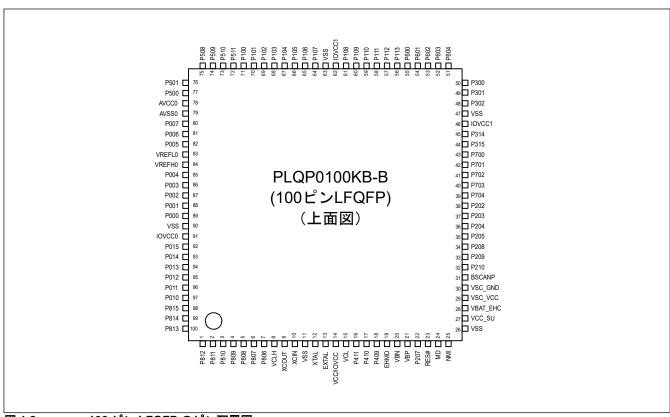

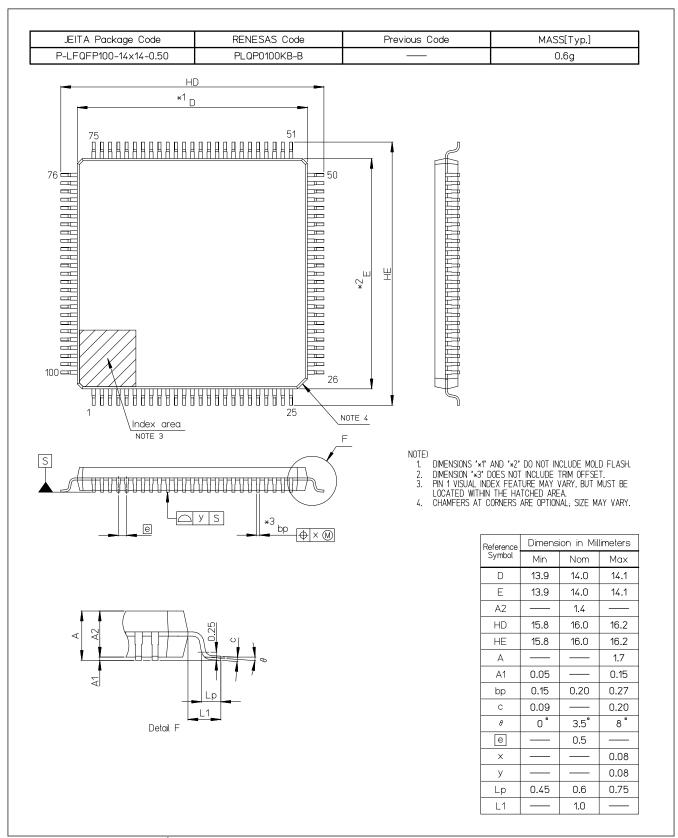

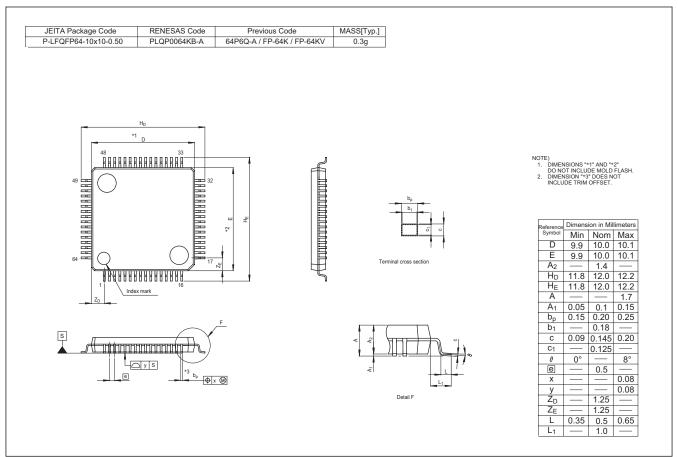

PLQP0100KB-B 14 × 14 mm, 0.5-mm ピッチ

PLOP0064KB-A 10×10 mm, 0.5-mm ピッチ

#### ■ 多種多用なアナログ回路

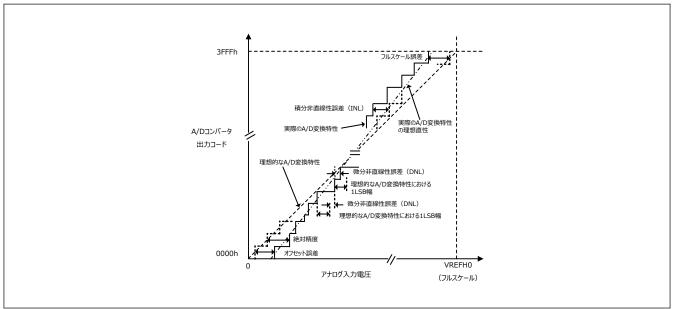

- 超低消費電力 14 ビット逐次比較型 A/D コンバータ×1 ユニ

- 高精度: 8 チャネル、標準精度: 4 チャネル チップ内部の温度を測定可能な温度センサ×1 ユニット

- 14 ビット A/D コンバータリファレンス電圧用の VREF 回路

### ■ 多種多様なタイマ回路

- 汎用 PWM タイマ (GPT)×6 チャネル 32 ビットカウントタイプ×2 チャネル 16 ビットカウントタイプ×4 チャネル

- スタンバイでも動作可能な非同期汎用タイマ (AGT)×4 チャ

- ネル

32 ビットカウントタイプ×2 チャネル

16 ビットカウントタイプ×2 チャネル

・8 ビットタイマ (TMR)×2 チャネル

・リアルタイムクロック (RTC)×1 チャネル

・ウォッチドックタイマ (WDT)×1 チャネル

・1 kHz 動作の低速クロックタイマ (LST)×1 チャネル

ストップウォッチ用 16 進数→10 進数変換回路

### ■ ヒューマンマシンインタフェース

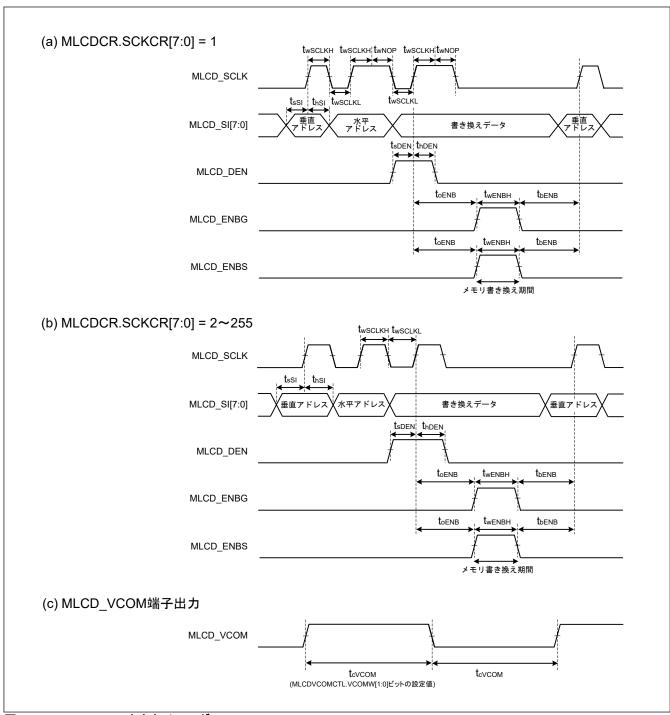

- MIP 液晶コントローラ (MLCD) × 1 ユニット (パラレルインタフェースタイプに対応)

2D グラフィックデータ変換回路 (GDT) × 1 ユニット

#### ■ セキュリティ機能(オプション)

- Trusted Secure IP Lite (TSIP) × 1 ユニット AES(鍵長 128 ビット/256 ビット ECB/CBC/CMAC/GCM 他に対応)

- Key wrapping によりユーザ暗号鍵の漏洩を防止 アクセスマネジメント回路により暗号エンジンの不正アク

- エリアプロテクション機能との併用でセキュアブート、セ キュア OTA が可能

## ■ 動作電圧·動作周囲温度

- VCC = IOVCC = IOVCCn= AVCC0 =  $1.62 \text{ V} \sim 3.6 \text{ V}$ IOVCCn、AVCC0は、1.62 V~3.6 V の範囲で独立に電圧設定

- Ta: -40°C∼+85°C

## 1. 概要

## 1.1 機能の概要

表 1.1 ~表 1.11 には最大仕様を掲載しています。周辺機能のチャネル数はパッケージのピン数によって異なります。詳細は表 1.13 を参照してください。

### 表 1.1 CPU

| 機能                                          | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm <sup>®</sup> Cortex <sup>®</sup> -M0+コア | <ul> <li>最高動作周波数: 64 MHz</li> <li>Arm Cortex-M0+コア:         <ul> <li>リビジョン: r0p1-00rel0</li> <li>Armv6-M アーキテクチャプロファイル</li> <li>シングルサイクル整数乗算器</li> </ul> </li> <li>Arm メモリプロテクションユニット (MPU):                   <ul> <li>Armv6 保護メモリシステムアーキテクチャ</li> <li>8 つの保護領域</li> </ul> </li> <li>SysTick タイマ:                         <ul> <li>SYSTICCLK (LOCO または ICLK) による駆動</li> </ul> </li> <li>Arm よモリシステムアーキテクチャ</li> <li>高の保護領域</li> <li>SysTick タイマ:                          <ul> <li>SYSTICCLK (LOCO または ICLK) による駆動</li> <li>Armve</li> <li>Armve</li></ul></li></ul> |

### 表 1.2 メモリ

| 機能          | 機能の説明                                                                                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

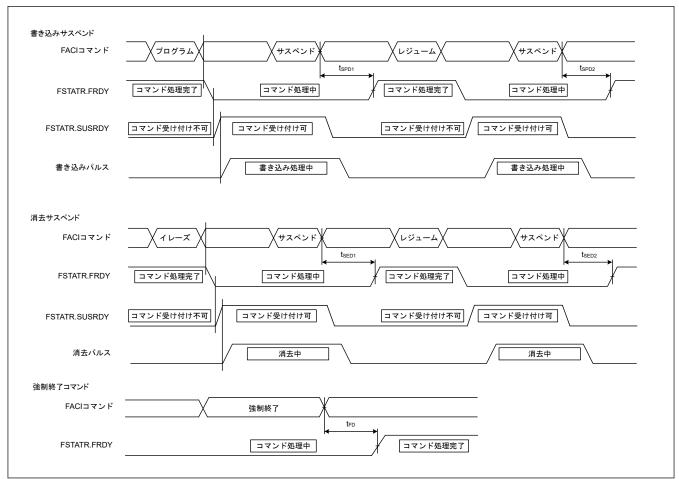

| コードフラッシュメモリ | <ul> <li>最大 256 KB のコードフラッシュメモリ。</li> <li>32 MHz 以下では 0 ウェイト、32 MHz より速い場合には 1 ウェイト</li> <li>プリフェッチ機能</li> <li>オンボードプログラミング: 3 種類         <ul> <li>シリアルプログラミングモード(SCI ブートモード)でのプログラム</li> <li>オンチップデバッグモードによるプログラム</li> <li>ユーザプログラム中のコードフラッシュメモリ書き換えルーチンによるプログラム</li> </ul> </li> </ul> |

| SRAM        | <ul> <li>最大 128 KB の SRAM<br/>SRAM0: 0x2000_0000~0x2000_7FFF<br/>SRAM1: 0x2000_8000~0x2001_FFFF<br/>上記いずれの領域も、低リーク電流モード時に使用可能</li> <li>64 MHz、0 ウェイトアクセス</li> </ul>                                                                                                                      |

### 表 1.3 システム (1/2)

| 機能         | 機能の説明                                                                                                                                                                                                                                                                                                                                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 起動モード      | 3 種類の起動モード:                                                                                                                                                                                                                                                                                                                                                  |

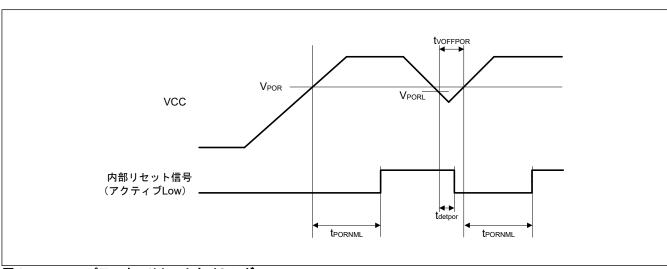

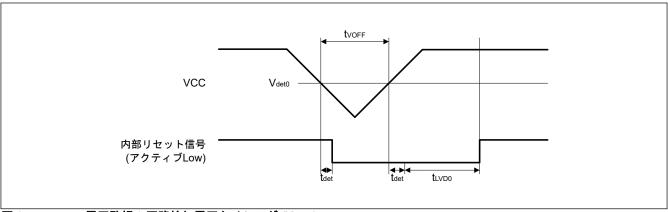

| リセット       | 本製品は 13 種類のリセットをサポートしています。リセットは MCU が初期化されるシステムリセットと、MCU が初期化されない電源遮断リセットに分類されます。                                                                                                                                                                                                                                                                            |

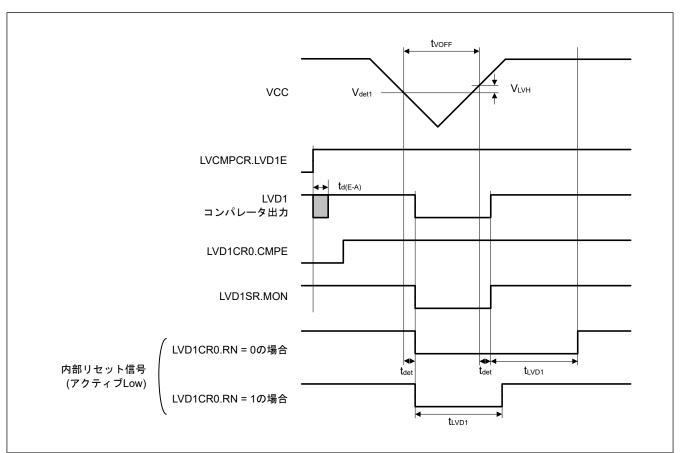

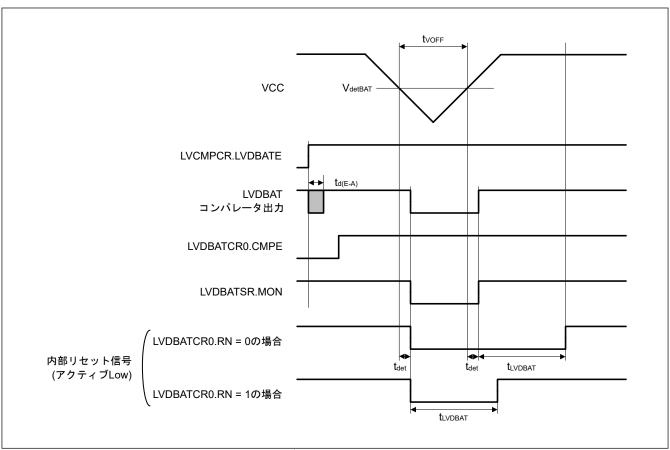

| 低電圧検出(LVD) | 低電圧検出モジュール (LVD) は、VCC 端子と VBAT_EHC 端子への入力電圧レベルを監視します。検出レベルはレジスタ設定で選択できます。LVD は、3 つの独立した電圧監視回路 (LVD0、LVD1、LVDBAT) で構成され、LVD0 と LVD1 は VCC 端子への入力電圧レベルを、LVDBAT は VBAT_EHC 端子への入力電圧レベルを監視します。LVD のレジスタを設定することにより、さまざまな電圧しきい値で VCC 端子への入力電圧および VBAT_EHC 端子への入力電圧の変動を監視できます。                                                                                     |

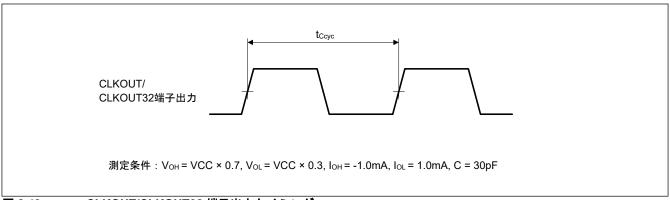

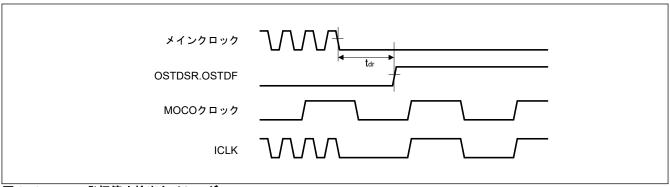

| クロック       | <ul> <li>● 以下のクロック発生回路を内蔵         <ul> <li>メインクロック発振器 (MOSC)</li> <li>サブクロック発振器 (SOSC)</li> <li>高速オンチップオシレータ (HOCO)</li> <li>中速オンチップオシレータ (MOCO)</li> <li>低速オンチップオシレータ (LOCO)</li> <li>IWDT 専用オンチップオシレータ (IWDTLOCO)</li> </ul> </li> <li>● クロック出力サポート         <ul> <li>CLKOUT 端子 (全クロック種を出力可能)</li> <li>CLKOUT32K 端子 (SOSC クロックを出力可能)</li> </ul> </li> </ul> |

## 表 1.3 システム (2/2)

| 機能                                        | 機能の説明                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| クロック周波数精度測定回路(CAC)                        | クロック周波数精度測定回路 (CAC) は、測定の対象となるクロック (測定対象クロック) に対して、測定の基準となるクロック (測定基準クロック) で生成した時間内のクロックのパルスを数え、それが許容範囲内にあるか否かで精度を判定します。測定の終了または測定基準クロックで生成した時間内のクロックのパルス数が許容範囲外の場合、割り込み要求を発生します。                                                                                                                                                                                                  |

| 割り込みコントローラユニット (ICU)                      | 割り込みコントローラユニット (ICU) は、ネスト型ベクタ割り込みコントローラ (NVIC)、DMA<br>コントローラ (DMAC)、およびデータトランスファコントローラ (DTC) モジュールにリンクされ<br>るイベント信号を制御します。ICU はノンマスカブル割り込みも制御します。                                                                                                                                                                                                                                 |

| 消費電力低減機能                                  | クロック分周器の設定、モジュールストップ設定、動作時の電力制御モード選択、低消費電力モードへの遷移、ドメイン単位の電源供給モードなど、さまざまな省電力機能があります  ● 動作周波数に応じた 3 種類の電力制御モード  - ブーストモード (~64 MHz)  - ノーマルモード  • High-speed モード (~32 MHz)  • Low-speed モード (~2 MHz)  - 低リーク電流モード (32.768 kHz)  • 5 種類の低消費電力モード  - スリープモード  - スリープモード  - スリープモード  - スヌーズモード  - ディープソフトウェアスタンバイモード  - ディープソフトウェアスタンバイモード  - 全電源供給モード (ALLPWON)  - 昆の電源供給モード (MINPWON) |

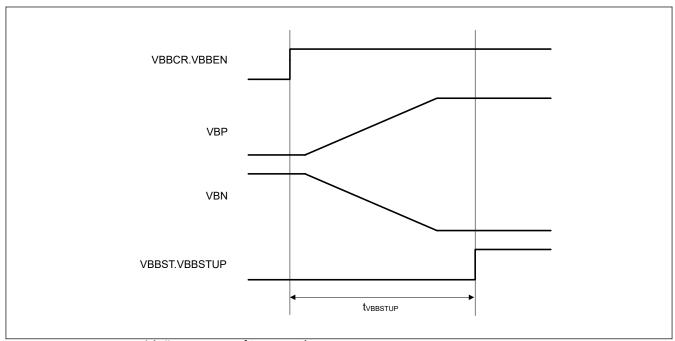

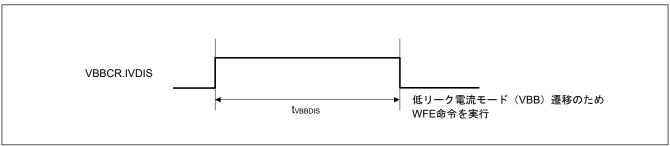

| バックバイアス電圧制御 <sup>(注1)</sup> (VBBC) 機<br>能 | バックバイアス電圧をプログラム制御することで、低リーク電流モードでの低リーク電流動作が<br>可能になります。                                                                                                                                                                                                                                                                                                                            |

| エナジーハーベスト制御回路(EHC)                        | 発電素子と、蓄電用コンデンサ、および2次電池を制御して超低消費電力状態での起動が可能に<br>なります。                                                                                                                                                                                                                                                                                                                               |

| レジスタライトプロテクション (RWP)                      | レジスタライトプロテクション機能は、ソフトウェアエラーによって重要なレジスタが書き換えられないように保護します。保護するレジスタは、プロテクトレジスタ (PRCR) で設定します。                                                                                                                                                                                                                                                                                         |

| メモリプロテクションユニット(MPU)                       | 本 MCU は、4 つのメモリプロテクションユニットと、CPU スタックポインタモニタ機能を備えています。                                                                                                                                                                                                                                                                                                                              |

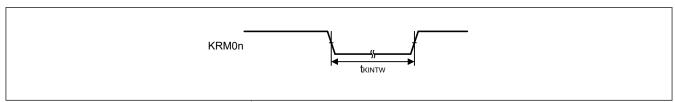

| キー割り込み機能(KINT)                            | キー割り込み機能 (KINT) は、キー割り込み機能端子の有効なエッジが検出されると、キー割り込み (KEY_INTKR) を生成します。                                                                                                                                                                                                                                                                                                              |

## 注 1. VBP/VBN 端子に充電する電圧

### 表 1.4 イベントリンク

| 機能 | 機能の説明                                                                                                                                             |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------|

|    | イベントリンクコントローラ (ELC) は、各周辺モジュールで発生する割り込み要求をイベント信号とし、モジュール間を相互に接続(リンク)することにより、CPUを介さず直接モジュール間で連携動作ができます。イベント信号は、該当する割り込み要求許可ビットの設定に関係なく出力することができます。 |

## 表 1.5 ダイレクトメモリアクセス

| 機能                       | 機能の説明                                                                                                                        |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DMA コントローラ (DMAC)        | 本 MCU は、4 チャネルの DMA コントローラ (DMAC) を内蔵しており、CPU を介さずにデータ<br>転送が可能です。DMA 転送要求が発生すると、DMAC は転送元アドレスに格納されているデー<br>タを転送先アドレスへ転送します。 |

| データトランスファコントローラ<br>(DTC) | データトランスファコントローラ (DTC) は、割り込み要求によって起動するとデータ転送を行います。                                                                           |

## 表 1.6 タイマ

| 機能                         | 機能の説明                                                                                                                                                                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 汎用 PWM タイマ(GPT)            | 本 MCU は、2 チャネルの 32 ビットタイマと、4 チャネルの 16 ビットタイマにより構成される<br>汎用 PWM タイマ (GPT) を内蔵しています。PWM 波形はアップカウンタ、ダウンカウンタ、ま<br>たはその両方を制御することにより生成が可能です。                                                                                                     |

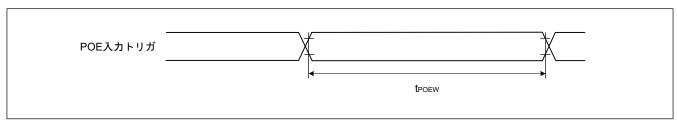

| GPT 用のポートアウトプットイネーブル (POE) | ポートアウトプットイネーブル (POE) は、以下の方法のいずれかにより、汎用 PWM タイマ (GPT) の出力端子を出力禁止状態にすることが可能です。                                                                                                                                                              |

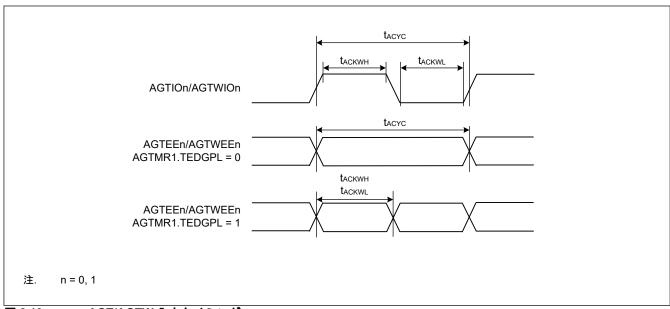

| 非同期汎用タイマ (AGT, AGTW)       | 非同期汎用タイマ (AGT、AGTW) は、パルス出力、外部パルスの幅または周期の測定、および外部イベントのカウントに利用可能な 16 ビットおよび 32 ビットのタイマです。この 16 ビットおよび 32 ビットタイマは、リロードレジスタとダウンカウンタで構成されています。これらのリロードレジスタとダウンカウンタは、同一アドレスに配置され、AGT レジスタでアクセス可能です。                                             |

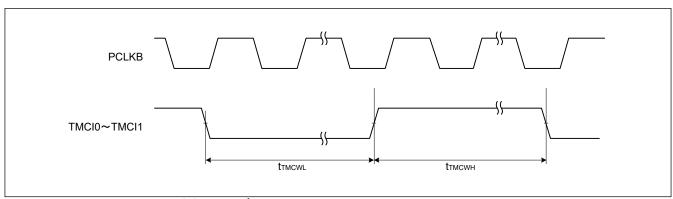

| 8 ビットタイマ (TMR)             | 8 ビットタイマ (TMR) は外部イベントをカウント可能です。また、2 つのレジスタのコンペアマッチ信号を使用して、カウンタクリア、割り込み要求出力、および任意のデューティ比のパルス出力の機能を備えています。                                                                                                                                  |

| ウェイクアップタイマ (WUPT)          | ウェイクアップタイマ (WUPT) は 32 ビットカウンタをベースにしています。また、カウントリセット、割り込み要求出力、およびオーバフロー発生時に外部端子にパルス出力の機能を備えています。                                                                                                                                           |

| リアルタイムクロック(RTC)            | リアルタイムクロック (RTC) には、カレンダカウントモード、バイナリカウントモードおよび 32 kHz カウントモードの 3 種類のカウントモードがあり、レジスタ設定を切り替えることで使 用します。カレンダカウントモードは、2000 年から 2099 年の 100 年間のカレンダを保持し、うるう年の日付を自動補正します。バイナリカウントモードでは、秒をカウントし、その情報をシリアル値として保持します。バイナリカウントモードは、西暦以外のカレンダに利用可能です。 |

| クロック補正回路 (CCC)             | サブクロック 32.768 kHz に対して、16 秒周期で発振精度補正が可能  ■ 補正後クロック出力: 2.048 kHz/512 Hz  ■ 信号出力 (CCCOUT): 512 Hz/1 Hz、および RTC 出力 (1 Hz/64 Hz) から選択可能  ■ ELC によるイベントリンク機能をサポート                                                                               |

| ウォッチドッグタイマ (WDT)           | ウォッチドッグタイマ (WDT) は 14 ビットのダウンカウンタです。システムが暴走すると WDT をリフレッシュできなくなるため、カウンタがアンダフローした際に MCU をリセットすることができます。さらに、ノンマスカブル割り込みやアンダフロー割り込み、を発生させるためにも使用できます。                                                                                         |

| 独立ウォッチドッグタイマ (IWDT)        | 独立ウォッチドッグタイマ (IWDT) は 14 ビットのダウンカウンタで、システム暴走時に MCU をリセットすることができます。IWDT は、MCU をリセットする機能や、カウンタのアンダフロー発生時に、割り込み/ノンマスカブル割り込みを発生させることが可能です。                                                                                                     |

| 低速クロックタイマ (LST)            | 低速クロックタイマ (LST) は、1 kHz のタイマカウンタと、16 進数→10 進数変換回路を内蔵しています。10 進数表示が必要なカウントとして利用可能な 13 ビットのタイマです。                                                                                                                                            |

# 表 1.7 通信インタフェース (1/2)

| 機能                               | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| シリアルコミュニケーションインタフェース (SCI)       | <ul> <li>シリアルコミュニケーションインタフェース (SCI) × 7 チャネルには調歩同期式および同期式のシリアルインタフェースがあります。</li> <li>● 調歩同期式インタフェース (UART および調歩同期式通信インタフェースアダプタ (ACIA))</li> <li>● 8 ビットクロック同期式インタフェース</li> <li>● 簡易 IIC (マスタのみ)</li> <li>● 簡易 SPI</li> <li>● スマートカードインタフェース</li> <li>スマートカードインタフェースは、電子信号と伝送プロトコルに関して ISO/IEC 7816-3 規格に準拠しています。SCIn (n = 0, 1) は FIFO バッファを内蔵しており、連続した全二重通信が可能です。また、内蔵のボーレートジェネレータを用いて、データ転送速度の個別設定が可能です。</li> </ul> |

| IrDA インタフェース (IrDA)              | IrDA インタフェースは、SCI1 と連携して IrDA (Infrared Data Association) 規格バージョン 1.0 に基づく IrDA 通信波形の送受信を行います。                                                                                                                                                                                                                                                                                                                         |

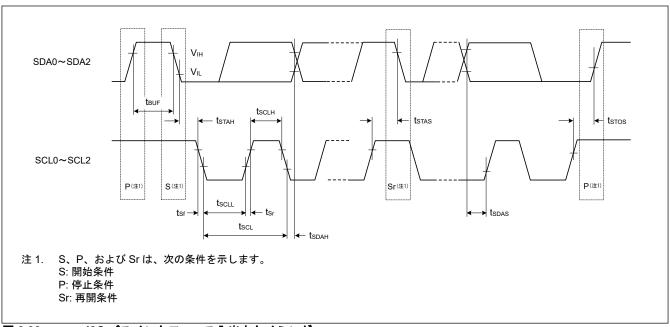

| I <sup>2</sup> C バスインターフェース(IIC) | $I^{2}$ C バスインタフェース (IIC) には $2$ チャネルあります。IIC は、NXP 社の $I^{2}$ C バス (InterIntegrated Circuit Bus) インタフェース方式に準拠しており、そのサブセット機能を備えています。                                                                                                                                                                                                                                                                                   |

## 表 1.7 通信インタフェース (2/2)

| 機能                           | 機能の説明                                                         |

|------------------------------|---------------------------------------------------------------|

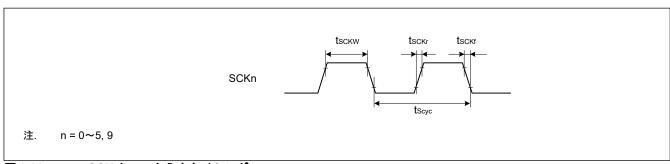

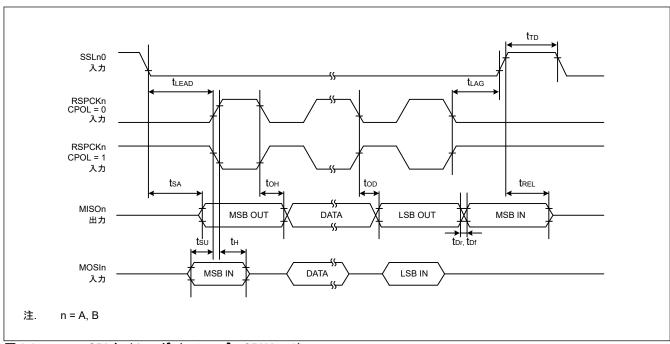

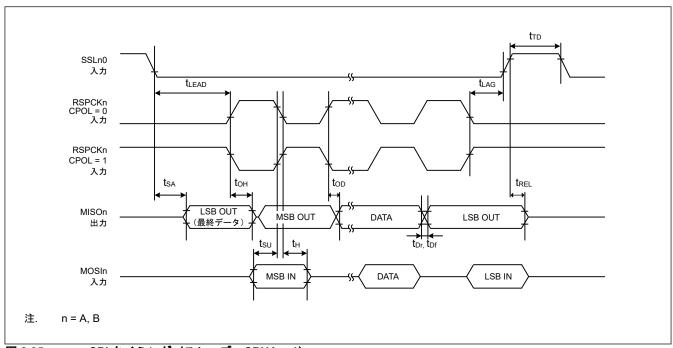

| シリアルペリフェラルインタフェース<br>(SPI)   | SPI によって、複数のプロセッサや周辺デバイスとの高速な全二重同期式のシリアル通信が可能です               |

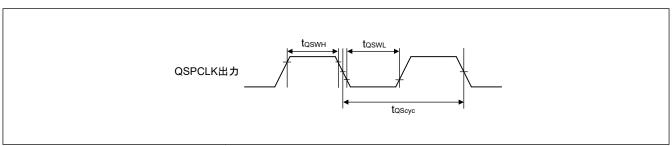

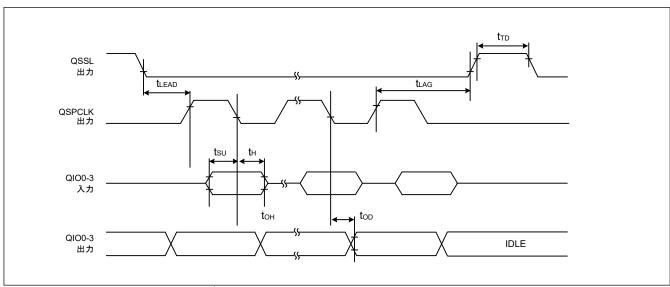

| クワッドシリアルペリフェラルインタフェース (QSPI) | SPI 互換インタフェースを持つシリアル ROM に接続することが可能                           |

| 外部バス                         | QSPI 領域: QSPI(外部デバイスインタフェース)を接続可能グループ A 優先制御動作(グループスキャンモードのみ) |

## 表 1.8 アナログ

| 機能                      | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14 ビット A/D コンバータ(ADC14) | <ul> <li>逐次比較方式の 14 ビット A/D コンバータを内蔵しています。アナログ入力チャネルは最大 12 チャネルまで選択可能です。変換にはアナログ入力、温度センサ出力を選択できます。A/D 変換精度には 12 ビット変換と 14 ビット変換が選択可能であり、デジタル値生成における速度と分解能のバランスを最適化できます。 <ul> <li>14 ビット×12 チャネル(最大値)(高精度:8 チャネル、標準精度:4 チャネル)</li> <li>分解能:14 ビット (14 ビットまたは 12 ビット変換が選択可能)</li> <li>動作モード: スキャンモード (シングルスキャンモード/連続スキャンモード/グループスキャンモード)</li> <li>グループA 優先制御動作 (グループスキャンモードのみ)</li> <li>サンプリングステート数可変機能</li> <li>A/D 変換値加算モードと平均モードが選択可能</li> <li>断線検出アシスト機能</li> <li>ダブルトリガモード (A/D 変換データ 2 重化機能)</li> <li>ELC によるイベントリンク機能をサポート</li> <li>A/D データレジスタオートクリア機能</li> <li>コンペア機能 (ウィンドウA、ウィンドウB)</li> <li>デジタルコンペア機能</li> <li>コンペアレジスタとデータレジスタとの比較、データレジスタ間の比較</li> </ul> </li> </ul> |

| 温度センサ(TSN)              | デバイス動作の信頼性確保のため、内蔵されている温度センサ (TSN) でチップの温度を測定し、監視することができます。温度センサはチップの温度と正比例する電圧を出力します。チップ温度と出力電圧はほとんどリニアの関係にあります。出力された電圧は 14 ビット A/D コンバータでデジタル値に変換することで使用できます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 基準電圧生成回路(VREF)          | 2 種類(1.25V/2.5V)の基準電圧を生成する回路です<br>ADC の基準電圧として使用可能です                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## 表 1.9 ヒューマンマシーンインタフェース

| 機能                                 | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIP 液晶コントローラ(MLCD) <sup>(注1)</sup> | MIP 方式の液晶パネルドライバ回路内蔵                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2D グラフィックデータ変換回路 (GDT)             | <ul> <li>2次元画像データを処理できるグラフィックアクセラレータ回路内蔵</li> <li>● 最大 32 パイトの画像データを処理します。フォント展開は 63 x 64 ビットまで対応可能です。</li> <li>● グルー 90°右回転、90°左回転、上下反転、左右反転</li> <li>● 平均画素法で 1/8、2/8、3/8、4/8、5/8、6/8、7/8 縮小、ビット間引き法 (1/2) に対応</li> <li>● 画像のビット反転が可能: 1 は 0 に、0 は 1 に反転されます。</li> <li>● 前景画像、背景画像、縁取り画像のモノクロ画像を合成</li> <li>● 前景画像と背景画像のカラー画像を合成、優先色と透過色の設定</li> <li>● 1 ビット単位での画像スクロール</li> <li>● フォントデータを画像データに変換可能</li> <li>● RGB 値を使用したモノクロ画像のカラー化</li> <li>● カラーデータ整列により、メモリ内の独立した R/G/B 画像を単一領域に RGB の順で並べ替え可能</li> <li>● エンディアン変換</li> </ul> |

注 1. 一般的な 3線式 MIP は、SPIO と GDT を組み合わせることで対応可能。

## 表 1.10 データ処理

| 機能             | 機能の説明                                                                                                                                                                                                                                                                                        |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 巡回冗長検査(CRC)演算器 | 巡回冗長検査(CRC:Cyclic Redundancy Check)演算器は、CRC コードを生成してデータエラーを検出します。LSB ファーストまたは MSB ファーストでの通信用に、CRC 演算結果のビットオーダを切り替えることができます。さらに、さまざまな CRC 生成多項式を使用できます。スヌープ機能により、特定のアドレスに対する読み出しおよび書き込みをモニタできます。この機能は、シリアル送信バッファへの書き込みとシリアル受信バッファからの読み出しをモニタする場合など、特定のイベントで CRC コードの自動生成が必要となるアプリケーションで役立ちます。 |

| データ演算回路(DOC)   | データ演算回路 (DOC) は、16 ビットのデータを比較、加算、または減算する機能です。選択した条件に一致する場合、割り込み要求が発生します。                                                                                                                                                                                                                     |

| 除算器 (DIV)      | 符号付き 32 ビット固定小数点データを高速除算する回路  ● 被除数:符号付き 32 ビットデータ  ● 除数:符号付き 32 ビットデータ                                                                                                                                                                                                                      |

| データ変換回路 (DIL)  | 32 ビットデータのデータ変換する回路を内蔵                                                                                                                                                                                                                                                                       |

## 表 1.11 セキュリティ

| 機能                                 | 機能の説明                                                                                                                                                                            |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trusted Secure IP Lite (TSIP-Lite) | <ul> <li>アクセスマネジメント回路搭載</li> <li>セキュリティアルゴリズム         <ul> <li>共通鍵暗号(対称暗号方式): AES 鍵長: 128 ビット/256 ビット</li> <li>暗号利用モード: GCM、ECB、CBC、CMAC、XTS、CTR、GCTR、CCM</li> </ul> </li> </ul> |

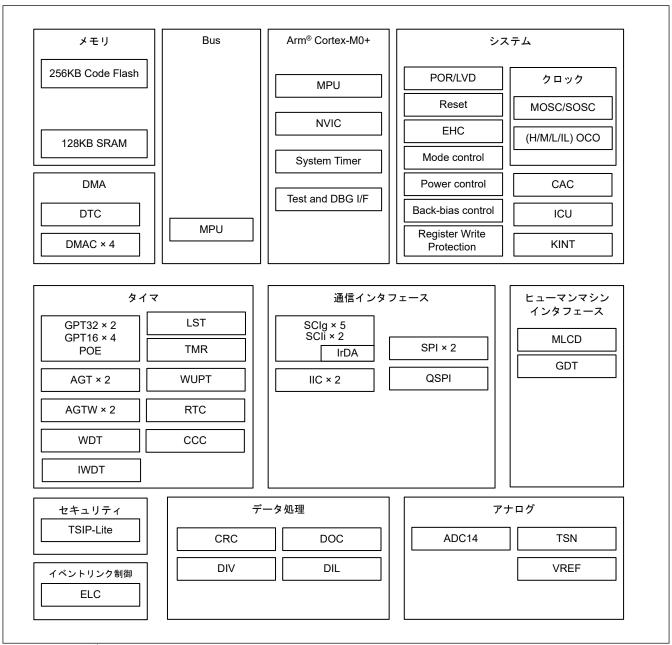

## 1.2 ブロック図

図 1.1 にスーパーセットのブロック図を示します。グループ内の個々のデバイスによっては、その機能のサブセットを持つ場合があります。

図 1.1 ブロック図

## 1.3 型名

表 1.12 に製品一覧を示します。

## 表 1.12 製品一覧

| 製品の型名         | パッケージコード        | コードフラッシ<br>ュメモリ容量 | SRAM 容量 | TSIP-Lite |

|---------------|-----------------|-------------------|---------|-----------|

| R7F0E01182CFP | PLQP0100KB-B    | 256 KB            | 128 KB  | サポートあり    |

| R7F0E01082CFP | PLQP0100KB-B    |                   |         | サポートなし    |

| R7F0E01182CFM | PLQP0064KB-A    |                   |         | サポートあり    |

| R7F0E01082CFM | PLQP0064KB-A    |                   |         | サポートなし    |

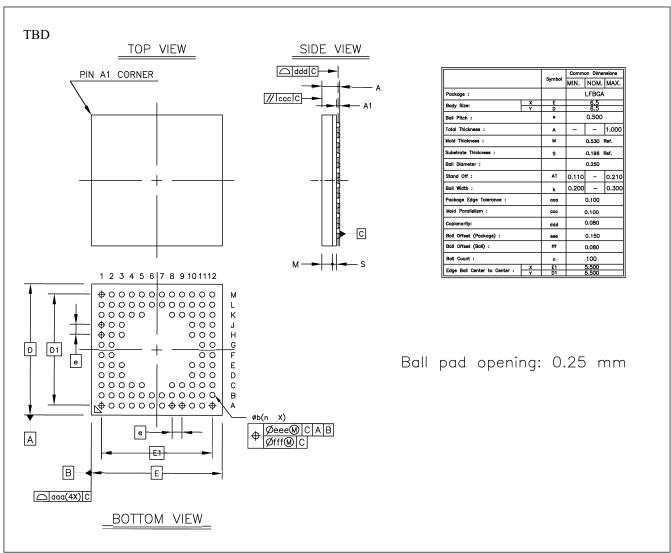

| R7F0E01182DBH | TBD (BGA100pin) |                   |         | サポートあり    |

| R7F0E01082DBH | TBD (BGA100pin) |                   |         | サポートなし    |

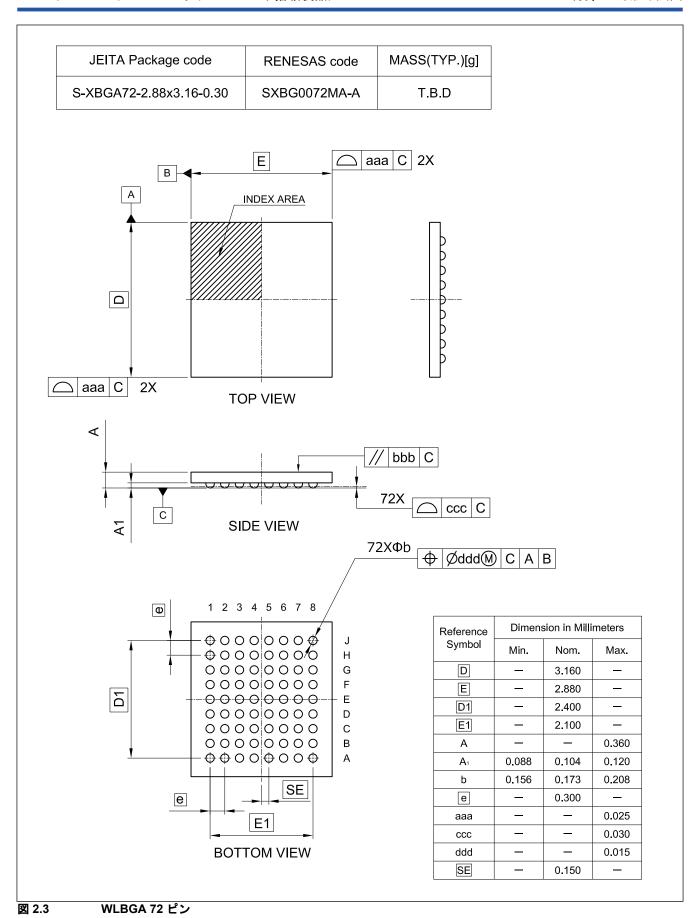

| R7F0E01182DBR | SXBG0072MA-A    |                   |         | サポートあり    |

| R7F0E01082DBR | SXBG0072MA-A    |                   |         | サポートなし    |

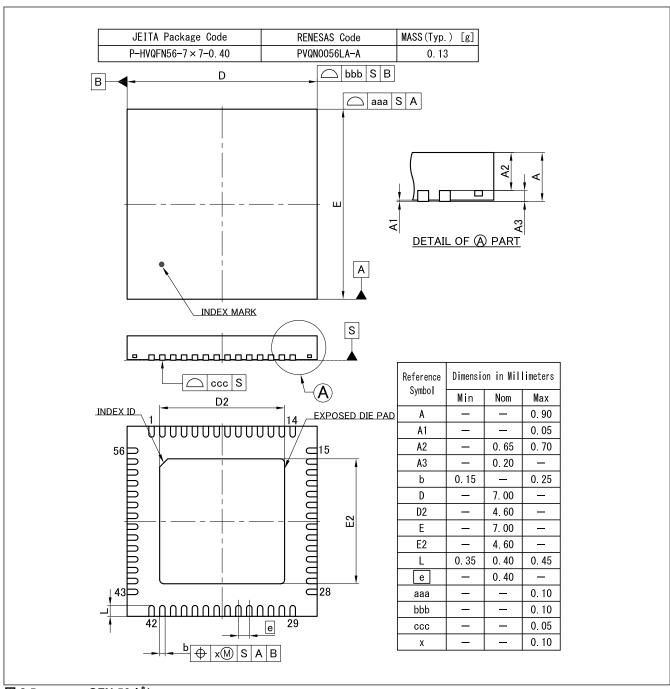

| R7F0E01182DNG | PVQN0056LA-A    |                   |         | サポートあり    |

| R7F0E01082DNG | PVQN0056LA-A    |                   |         | サポートなし    |

## 1.4 機能の比較

### 表 1.13 機能の比較 (1/4)

| 型名         |      |                     | R7F0E01182CFP                                                        | R7F0E01082CFP | R7F0E01182CFM   | R7F0E01082CFM | R7F0E01182DBH | R7F0E01082DBH |  |  |

|------------|------|---------------------|----------------------------------------------------------------------|---------------|-----------------|---------------|---------------|---------------|--|--|

| 端子総数       |      |                     | 100                                                                  |               | 6               | 64            | 10            | 00            |  |  |

| GPIO .     | 入出力ホ | <b>%</b> − <b>ト</b> | 7                                                                    | '3            | 3               | 37            | 7             | '3            |  |  |

|            | 入力ポー | - ト                 |                                                                      | 1             |                 | 1             |               | 1             |  |  |

| パッケージ      |      |                     |                                                                      | LF            | QFP             |               | BGA           |               |  |  |

| コードフラッシュメ  | モリ   |                     |                                                                      |               | 256             | 256 KB        |               |               |  |  |

| SRAM       |      |                     |                                                                      |               | 128             | 3 KB          |               |               |  |  |

| CPU 動作周波数  |      |                     | 最大 32 MHz(ノーマルモード)<br>最大 64 MHz(ブーストモード)<br>最大 32.768 kHz(低リーク電流モード) |               |                 |               |               |               |  |  |

| 割り込みコントロール |      | ICU                 | あり                                                                   |               |                 |               |               |               |  |  |

|            |      | IRQ                 | ch0                                                                  | ~ch9          | ch0~ch5、ch7~ch8 |               | ch0∼ch9       |               |  |  |

| キー割り込み     |      | KINT                |                                                                      |               | 8               | ch            |               |               |  |  |

| DMA        |      | DTC                 | あり                                                                   |               |                 |               |               |               |  |  |

|            |      | DMAC                | ch0∼ch3                                                              |               |                 |               |               |               |  |  |

| イベントコントロー  | ・ル   | ELC                 |                                                                      | あり            |                 |               |               |               |  |  |

| エナジーハーベスト  |      | EHC                 |                                                                      |               | b.              | 54            |               |               |  |  |

| バックバイアス電圧  | 制御   | VBBC                |                                                                      |               | あ               | 5 4           |               |               |  |  |

## 表 1.13 機能の比較 (2/4)

| 型名         |          |                 | R7F0E01182CFP       | R7F0E01082CFP | R7F0E01182CFM | R7F0E01082CFM   | R7F0E01182DBH | R7F0E01082DBH |  |  |  |

|------------|----------|-----------------|---------------------|---------------|---------------|-----------------|---------------|---------------|--|--|--|

| タイマ        | GPT32    |                 |                     |               | ch0           | ~ch1            |               |               |  |  |  |

| タイマ        | GPT16    |                 | ch2∼ch5             |               |               |                 |               |               |  |  |  |

|            |          | POE             |                     |               | <br>න         | , 4)            |               |               |  |  |  |

|            | AGT      | 1               | ch0∼ch1             |               |               |                 |               |               |  |  |  |

|            | AGTW     |                 |                     |               | ch0           | ~ch1            |               |               |  |  |  |

|            | TMR      |                 |                     |               | ch0           | ~ch1            |               |               |  |  |  |

|            | WUPT     |                 |                     |               | あ             | , <sup>()</sup> |               |               |  |  |  |

|            | RTC      |                 |                     |               | あ             | , <i>l</i> )    |               |               |  |  |  |

|            | ССС      |                 |                     |               | あ             | , <i>l</i> )    |               |               |  |  |  |

|            | WDT      |                 |                     |               | あ             | , <i>l</i> )    |               |               |  |  |  |

|            | IWDT     |                 |                     |               | ₽.            | , 4)            |               |               |  |  |  |

|            | LST      |                 |                     | あり            |               |                 |               |               |  |  |  |

| 通信機能       | SCIg     | FIFO なし         | ch2~ch5、ch9         |               |               |                 |               |               |  |  |  |

|            | SCIi     | FIFO あり         | ch0∼ch1             |               |               |                 |               |               |  |  |  |

|            |          | IrDA            | あり                  |               |               |                 |               |               |  |  |  |

|            | IIC      |                 | ch0~ch1 ch1 ch0~ch1 |               |               |                 |               |               |  |  |  |

|            | SPI      | 128 ビットバッフ<br>ァ | ch0                 |               |               |                 |               |               |  |  |  |

|            |          | 32 ビットバッフ<br>ァ  | ch1                 |               |               |                 |               |               |  |  |  |

|            | QSPI     |                 | あり                  |               |               |                 |               |               |  |  |  |

| アナログ       | ADC14    | 高精度             |                     |               | 8             | ch              |               |               |  |  |  |

| アナログ       |          | 標準精度            | 4ch なし 4ch          |               |               |                 |               |               |  |  |  |

|            | TSN      |                 | あり                  |               |               |                 |               |               |  |  |  |

|            | VREF     |                 | あり                  |               |               |                 |               |               |  |  |  |

| HMI グラフィック | MLCD     |                 | あり                  |               |               |                 |               |               |  |  |  |

|            | GDT      |                 | あり                  |               |               |                 |               |               |  |  |  |

| データ処理      | CRC      |                 | あり                  |               |               |                 |               |               |  |  |  |

|            | DOC      |                 |                     |               | あ             | 9               |               |               |  |  |  |

|            | DIV      |                 |                     |               | あ             | 9               |               |               |  |  |  |

|            | DIL      |                 |                     |               | あ             | 9               |               |               |  |  |  |

| セキュリティ     | TSIP-Lit | e               | あり                  | なし            | あり            | なし              | あり            | なし            |  |  |  |

## 表 1.13 機能の比較 (3/4)

|          | • •    |               |               |               |               |  |  |

|----------|--------|---------------|---------------|---------------|---------------|--|--|

| 型名       |        | R7F0E01182DBR | R7F0E01082DBR | R7F0E01182DNG | R7F0E01082DNG |  |  |

| 端子総数     |        | 7             | 72            |               | 6             |  |  |

| 汎用 I/O 数 | 入出力ポート | 入出力ポート 43 33  |               |               | 3             |  |  |

|          | 入力ポート  |               | 1             | 1             |               |  |  |

| パッケージ    | ,      | WLE           | BGA           | QFN           |               |  |  |

| コードフラッシ  | ·ュメモリ  |               | 256 KB        |               |               |  |  |

| SRAM     |        |               | 128 KB        |               |               |  |  |

## 表 1.13 機能の比較 (4/4)

| 型名         |          |             | D750504400D50 | D75050400055                                       | D7F0F04400D1:0 | DZEGEGGGGGGG |  |  |

|------------|----------|-------------|---------------|----------------------------------------------------|----------------|--------------|--|--|

|            |          |             | R7F0E01182DBR |                                                    | R7F0E01182DNG  |              |  |  |

| CPU 動作周波数  |          |             | j             | 最大 32 MHz( <i>)</i><br>最大 64 MHz()<br>32.768 kHz(( | ブーストモード        | )            |  |  |

| 割り込みコントロー  | ール       | ICU         |               | あ                                                  | Ŋ              |              |  |  |

|            |          | IRQ         | ch0~          | ~ch9                                               | ch0∼ch5、       | ch7∼ch8      |  |  |

| キー割り込み     |          | KINT        |               | 80                                                 | ch             |              |  |  |

| DMA        |          | DTC         |               | あ                                                  | Ŋ              |              |  |  |

|            |          | DMAC        | ch0∼ch3       |                                                    |                |              |  |  |

| イベントコントロ-  | ール       | ELC         |               | あ                                                  | Ŋ              |              |  |  |

| エナジーハーベス   | -        | EHC         |               | あ                                                  | Ŋ              |              |  |  |

| バックバイアス電圧  | E制御      | VBBC        |               | あ                                                  | Ŋ              |              |  |  |

| タイマ        | GPT32    |             |               | ch0                                                | ~ch1           |              |  |  |

|            | GPT16    |             |               | ch2                                                | ~ch5           |              |  |  |

|            |          | POE         |               | あ                                                  | Ŋ              |              |  |  |

|            | AGT      |             |               | ch0                                                | ∼ch1           |              |  |  |

|            | AGTW     |             |               | ch0                                                | ~ch1           |              |  |  |

|            | TMR      |             |               | ch0                                                | ∼ch1           |              |  |  |

|            | WUPT     |             |               | あ                                                  | Ŋ              |              |  |  |

|            | RTC      |             | あり            |                                                    |                |              |  |  |

|            | ccc      |             | あり            |                                                    |                |              |  |  |

|            | WDT      |             | あり            |                                                    |                |              |  |  |

|            | IWDT     |             | あり            |                                                    |                |              |  |  |

|            | LST      |             |               | あ                                                  | Ŋ              |              |  |  |

| 通信機能       | SCIg     | FIFO なし     | ch2~ch5、ch9   |                                                    |                |              |  |  |

|            | SCIi     | FIFO あり     |               | ch0                                                | ~ch1           |              |  |  |

|            |          | IrDA        |               | あ                                                  | Ŋ              |              |  |  |

|            | IIC      |             | ch0~          | ~ch1                                               | cł             | 11           |  |  |

|            | SPI      | 128 ビットバッファ | ch0           |                                                    |                |              |  |  |

|            |          | 32 ビットバッファ  |               | cł                                                 | ո1             |              |  |  |

|            | QSPI     |             |               | あ                                                  | Ŋ              |              |  |  |

| アナログ       | ADC14    | 高精度         |               | 80                                                 | ch             |              |  |  |

|            |          | 標準精度        | 40            | ch                                                 | な              | L            |  |  |

|            | TSN      |             |               | あ                                                  |                |              |  |  |

|            | VREF     |             |               | あ                                                  |                |              |  |  |

| HMI グラフィック | MLCD     |             |               | あ                                                  | Ŋ              |              |  |  |

|            | GDT      |             |               | あ                                                  |                |              |  |  |

| データ処理      | CRC      |             |               | あ                                                  |                |              |  |  |

|            | DOC      |             |               | あ                                                  |                |              |  |  |

|            | DIV      |             |               | あ                                                  |                |              |  |  |

|            | DIL      |             |               | あ                                                  | Ŋ              |              |  |  |

| セキュリティ     | TSIP-Lit | e           | あり            | なし                                                 | あり             | なし           |  |  |

## 1.5 端子機能

表 1.14 に、端子機能一覧を示します。

表 1.14 端子機能一覧 (1/5)

| 機能 | 端子名            | 入出力 | 説明                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

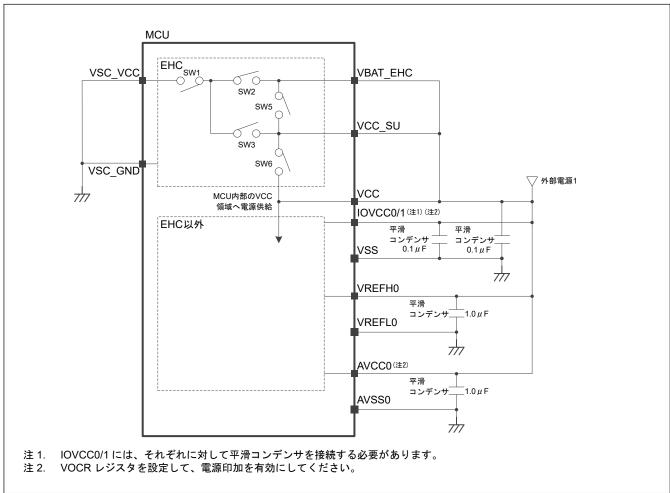

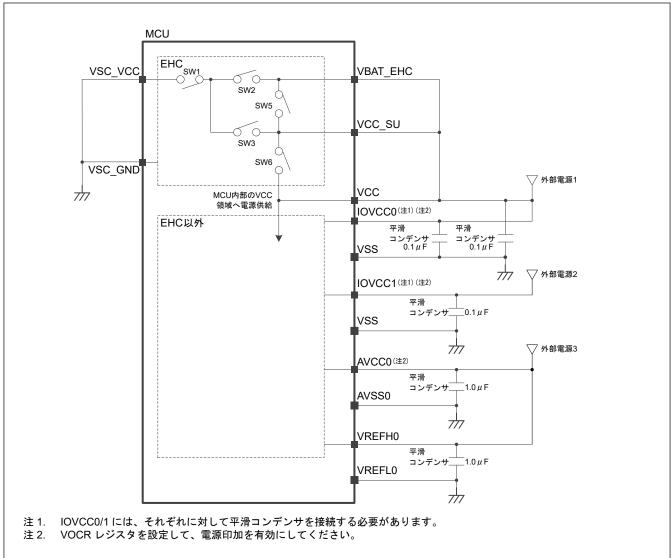

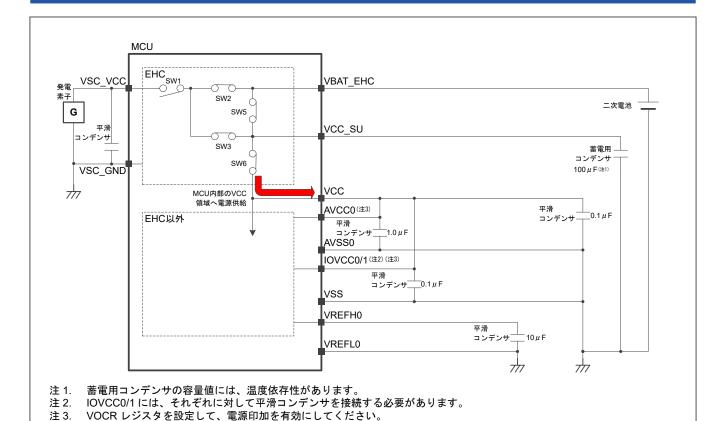

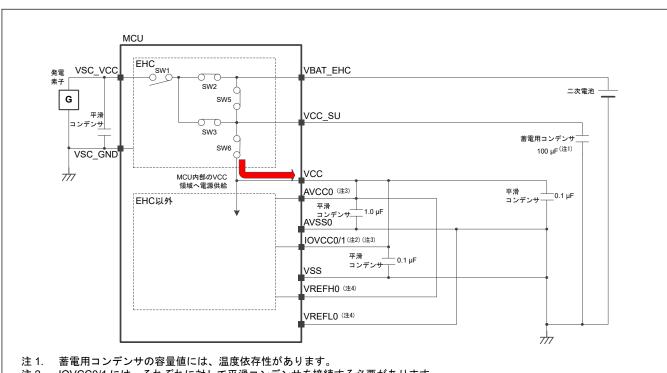

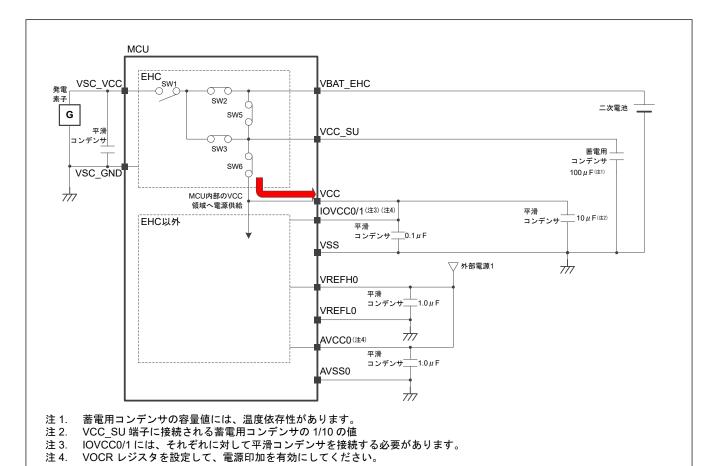

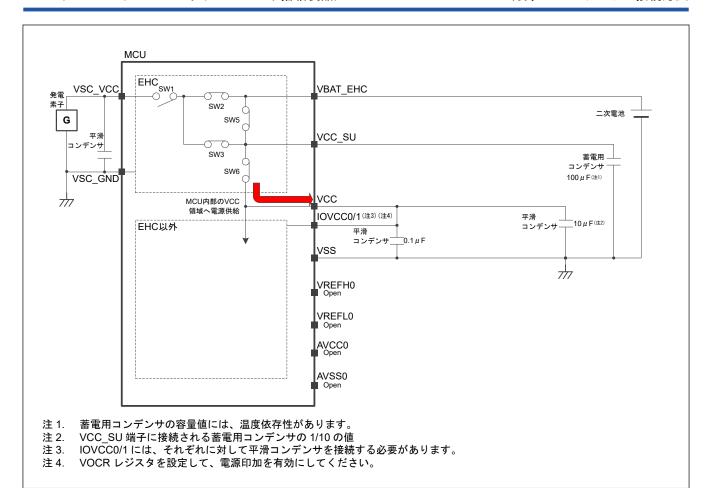

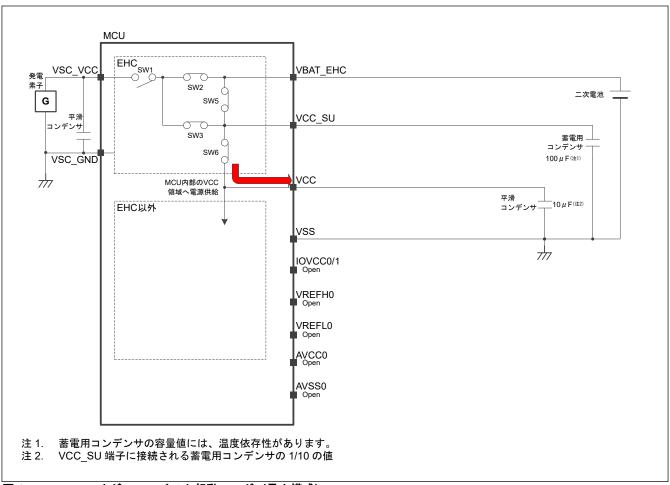

| 電源 | VCC/IOVCC      | 入力  | 通常起動モード 電源端子。システムの電源に接続してください。0.1 μF 平滑コンデンサを介して VSS に接続してください。平滑コンデンサは端子近くに配置してください。(注2)IOVCCn 端子より先に電圧を印加してください。 エナジーハーベスト起動モード 電源端子。システムの電源に接続してください。0.1 μF 平滑コンデンサ(1)を介して VSS に接続してください。平滑コンデンサは端子近くに配置してください。 上記に加えて外来ノイズへの耐性と回路の安定動作を向上させるために、VCC_SU 端子に接続する蓄電用コンデンサの 1/10 の容量の平滑コンデンサ(2)を介して VSS に接続してください。例えば、VCC_SU に 47 μF の蓄電用コンデンサを接続している場合は、4.7 μF の平滑コンデンサを接続してください。(2)の平滑コンデンサを端子近傍に配置できる場合は、(1)の平滑コンデンサを当路可能です。 |

|    | VSS            | 入力  | グランド端子。システムの電源(0V)に接続してください。                                                                                                                                                                                                                                                                                                                                                                                                    |

|    | VCL            | 入力  | 内部電源安定化端子。4.7μF の平滑コンデンサを介して VSS に接続してください。平滑コンデンサは端子近くに配置してください。                                                                                                                                                                                                                                                                                                                                                               |

|    | VCLH           | 入力  | 内部電源安定化端子。VCL 端子と別に、4.7µF の平滑コンデンサを介して VSS に接続してください。平滑コンデンサは端子近くに配置してください。                                                                                                                                                                                                                                                                                                                                                     |

|    | VBN            |     | バックバイアス電圧安定化端子。0.56µF の平滑コンデンサを介している。に対すしてください。平滑コンデンサは地ででは、東ア                                                                                                                                                                                                                                                                                                                                                                  |

|    | VBP            |     | ── て VSS に接続してください。平滑コンデンサは端子近くに配置し                                                                                                                                                                                                                                                                                                                                                                                             |

|    | VSC_VCC        | 入力  | 通常起動モード 発電素子から供給される電源端子。通常起動モードではシステムの電源 (OV) に接続してください エナジーハーベスト起動モード 発電素子から供給される電源端子。発電素子と並列に平滑コンデンサを介して VSC_GND に接続してください。平滑コンデンサは端子近くに配置してください。平滑コンデンサの容量値は4.7nF~47nFが推奨ですが、発電素子の安定度等から適切に選択ください                                                                                                                                                                                                                            |

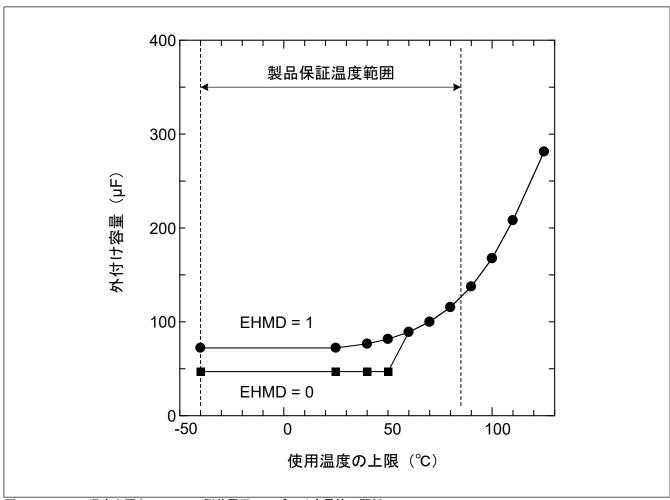

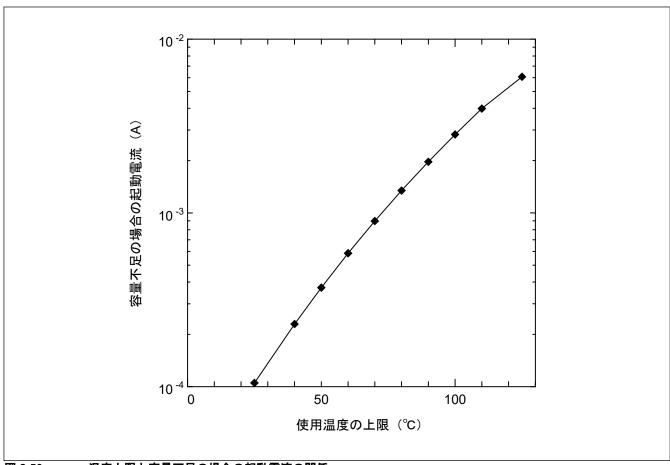

| 電源 | VCC_SU         | 入出力 | 通常起動モード<br>蓄電用コンデンサから供給される電源端子。通常起動モードでは VCC/IOVCC に短絡してください<br>エナジーハーベスト起動モード<br>蓄電用コンデンサから供給される電源端子。発電素子として太<br>陽電池を使用する場合は、接続する蓄電用コンデンサの容量値<br>は動作温度に応じたもので、かつ VCC の 10 倍以上の容量値が<br>必要です。25℃時は 47 µF が必要で、高温になるほど大きな容<br>量値が必要です。それ以外の発電素子を使用する場合は 100<br>µF の蓄電用コンデンサを接続してください。                                                                                                                                             |

|    | VSC_GND        | 入力  | VSC_VCC 用のグランド端子。システムの電源(OV)に接続してください                                                                                                                                                                                                                                                                                                                                                                                           |

|    | VBAT_EHC       | 入力  | <ul> <li>通常起動モード         <ul> <li>2次電池から供給される電源端子。通常起動モードでは VCC/IOVCC に接続してください</li> </ul> </li> <li>エナジーハーベスト起動モード         <ul> <li>2次電池から供給される電源端子。エナジーハーベスト起動モードでは 2.4 V、2.5 V、2.6 V、2.7 V、2.8 V、2.9 V、3.0 V、3.1 V の二次電池、またはスーパーキャパシタを接続します。</li> </ul> </li> </ul>                                                                                                                                                          |

|    | IOVCC0, IOVCC1 | 入力  | IO 用電源端子。0.1 µF の平滑コンデンサを介して VSS に接続してください。平滑コンデンサは端子近くに配置してください。(注2) (注3)                                                                                                                                                                                                                                                                                                                                                      |

## 表 1.14 端子機能一覧 (2/5)

| 機能          | 端子名                                 | 入出力 | 説明                                                                                                                   |

|-------------|-------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------|

| クロック        | XTAL                                | 入力  | MOSC 発振子接続端子。EXTAL は外部クロック入力端子                                                                                       |

|             | EXTAL                               | 出力  |                                                                                                                      |

|             | XCIN                                | 入力  | SOSC 発振子接続端子                                                                                                         |

|             | XCOUT                               | 出力  | 1                                                                                                                    |

|             | CLKOUT                              | 出力  | クロック出力端子                                                                                                             |

|             | CLKOUT32K                           | 出力  | SOSC クロック出力端子                                                                                                        |

| クロック周波数精度測定 | CACREF                              | 入力  | クロック周波数精度測定回路のリファレンスクロック入力端子                                                                                         |

| 起動モードコントロール | MD                                  | 入力  | モード設定端子。本端子の信号レベルは、リセット解除時の起動モ<br>ードの遷移中に変更しないでください                                                                  |

|             | EHMD                                | 入力  | エナジーハーベストモード設定端子                                                                                                     |

| システム制御      | RES#                                | 入力  | リセット信号入力端子。本端子が Low になると、MCU はリセット状態となります。                                                                           |

|             | BSCANP                              | 入力  | IOVCCn 端子電源強制入力端子<br>バウンダリスキャン機能を使用する際は、本端子を IOVCCn 端子に<br>電源供給されている状態において High レベルにすることで、全 I/O<br>ポートへの電源供給が許可されます。 |

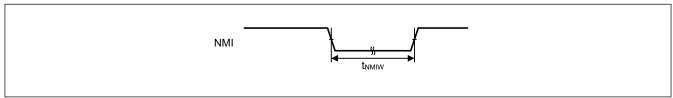

| 割り込み        | NMI                                 | 入力  | ノンマスカブル割り込み要求端子                                                                                                      |

|             | IRQ0~IRQ9,IRQ0_A_DS<br>~IRQ3_A_DS   | 入力  | マスカブル割り込み要求端子<br>端子名に"_DS"が付加されている端子は、ディープソフトウェアスタ<br>ンバイモードの解除端子として使用できます                                           |

| KINT        | KRM00~KRM07                         | 入力  | キー割り込みは、キー割り込み入力端子に立ち下がりエッジを入力<br>することで発生させることができます。                                                                 |

| オンチップデバッガ   | SWDIO                               | 入出力 | SWD データ入出力端子                                                                                                         |

|             | SWCLK                               | 入力  | SWD クロック入力端子                                                                                                         |

| バウンダリスキャン   | TMS                                 | 入力  | バウンダリスキャン端子                                                                                                          |

|             | TDI                                 | 入力  |                                                                                                                      |

|             | тск                                 | 入力  |                                                                                                                      |

|             | TDO                                 | 出力  |                                                                                                                      |

| GPT, POE    | GTIOC0A~GTIOC5A,<br>GTIOC0B~GTIOC5B | 入出力 | インプットキャプチャ、アウトプットコンペア、または PWM 出力<br>端子                                                                               |

|             | GTETRGA, GTETRGB                    | 入力  | 外部トリガ入力端子                                                                                                            |

|             | GTIU                                | 入力  | ホールセンサ入力端子 U                                                                                                         |

|             | GTIV                                | 入力  | ホールセンサ入力端子 V                                                                                                         |

|             | GTIW                                | 入力  | ホールセンサ入力端子 W                                                                                                         |

|             | GTOUUP                              | 出力  | BLDC モータ制御用 3 相 PWM 出力(正相 U 相)                                                                                       |

|             | GTOULO                              | 出力  | BLDC モータ制御用3相 PWM 出力(逆相 U 相)                                                                                         |

|             | GTOVUP                              | 出力  | BLDC モータ制御用 3 相 PWM 出力(正相 V 相)                                                                                       |

|             | GTOVLO                              | 出力  | BLDC モータ制御用 3 相 PWM 出力(逆相 V 相)                                                                                       |

|             | GTOWUP                              | 出力  | BLDC モータ制御用 3 相 PWM 出力(正相 W 相)                                                                                       |

|             | GTOWLO                              | 出力  | BLDC モータ制御用 3 相 PWM 出力(逆相 W 相)                                                                                       |

| AGT         | AGTIO0, AGTIO1                      | 入出力 | 外部イベント入力およびパルス出力端子                                                                                                   |

|             | AGTEE0, AGTEE1                      | 入力  | 外部イベント入力イネーブル信号                                                                                                      |

|             | AGTO0, AGTO1                        | 出力  | パルス出力端子                                                                                                              |

|             | AGTOA0, AGTOA1                      | 出力  | コンペアマッチ A 出力端子                                                                                                       |

|             | AGTOB0, AGTOB1                      | 出力  | コンペアマッチ B 出力端子                                                                                                       |

## 表 1.14 端子機能一覧 (3/5)

| 機能          | 端子名                                       | 入出力                   | 説明                                                    |  |  |  |

|-------------|-------------------------------------------|-----------------------|-------------------------------------------------------|--|--|--|

| AGTW        | AGTWIO0, AGTWIO1                          | 入出力                   | 外部イベント入力およびパルス出力端子                                    |  |  |  |

|             | AGTWEE0, AGTWEE1                          | 入力                    | 外部イベント入力イネーブル信号                                       |  |  |  |

|             | AGTWO0, AGTWO1                            | 出力                    | パルス出力端子                                               |  |  |  |

|             | AGTWOA0, AGTWOA1                          | 出力                    | コンペアマッチ A 出力端子                                        |  |  |  |

|             | AGTWOB0, AGTWOB1                          | 出力                    | コンペアマッチ B 出力端子                                        |  |  |  |

| TMR         | TMCI0, TMCI1                              | 入力                    | カウンタに入力する外部クロックの入力端子                                  |  |  |  |

|             | TMRI0, TMRI1                              | 入力                    | カウンタリセット入力端子                                          |  |  |  |

|             | TMO0, TMO1                                | 出力                    | コンペアマッチ出力端子                                           |  |  |  |

| WUPT        | TMWO                                      | 出力                    | パルス出力端子                                               |  |  |  |

| RTC         | RTCIC0-RTCIC2                             | 入力                    | 時間キャプチャイベント入力端子                                       |  |  |  |

|             | RTCOUT                                    | 出力                    | 1Hz または 64Hz のクロック出力端子                                |  |  |  |

| ccc         | CCCOUT                                    | 出力                    | CCC クロック出力端子                                          |  |  |  |

| CCC<br>SCIi | 【調歩同期式モード/ク                               | 【調歩同期式モード/クロック同期式モード】 |                                                       |  |  |  |

|             | SCK0, SCK1                                | 入出力                   | クロック用の入出力端子 (クロック同期式モード)                              |  |  |  |

|             | RXD0, RXD1                                | 入力                    | 受信データ用の入力端子(調歩同期式モード/クロック同期式モード)                      |  |  |  |

|             | TXD0, TXD1                                | 出力                    | 送信データ用の出力端子(調歩同期式モード/クロック同期式モード)                      |  |  |  |

|             | CTS0, CTS1                                | 入力                    | 送受信の開始制御用の入力端子(調歩同期式モード/クロック同期<br>式モード)               |  |  |  |

|             | RTS0, RTS1                                | 出力                    | 送受信の開始制御用の出力端子(調歩同期式モード/クロック同期<br>式モード)               |  |  |  |

|             | 【簡易 I <sup>2</sup> C モード】 <sup>(注1)</sup> | 1                     |                                                       |  |  |  |

|             | SSCL0, SSCL1                              | 入出力                   | I <sup>2</sup> C クロック用の入出力端子(簡易 I <sup>2</sup> C モード) |  |  |  |

|             | SSDA0, SSDA1                              | 入出力                   | I <sup>2</sup> C データ用の入出力端子(簡易 I <sup>2</sup> C モード)  |  |  |  |

|             | 【簡易 SPI モード】 <sup>(注1)</sup>              |                       |                                                       |  |  |  |

|             | SCK0, SCK1                                | 入出力                   | クロック用の入出力端子(簡易 SPI モード)                               |  |  |  |

|             | MISO0, MISO1                              | 入出力                   | データのスレーブ送信用の入出力端子(簡易 SPI モード)                         |  |  |  |

|             | MOSI0, MOSI1                              | 入出力                   | データのマスタ送信用の入出力端子(簡易 SPI モード)                          |  |  |  |

|             | SS0, SS1                                  | 入力                    | チップセレクト入力端子(簡易 SPI モード)                               |  |  |  |

## 表 1.14 端子機能一覧 (4/5)

| 機能     | 端子名                                       | 入出力     | 説明                                                                                                                                                                   |

|--------|-------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SClg   | 【調歩同期式モード/クロッ                             | ック同期式モー | - F]                                                                                                                                                                 |

|        | SCK2~SCK5, SCK9                           | 入出力     | クロック用の入出力端子 (クロック同期式モード)                                                                                                                                             |

|        | RXD2~RXD5, RXD9                           | 入力      | 受信データ用の入力端子 (調歩同期式モード/クロック同期式モード)                                                                                                                                    |

|        | TXD2~TXD5, TXD9                           | 出力      | 送信データ用の出力端子 (調歩同期式モード/クロック同期式モード)                                                                                                                                    |

|        | CTS2~CTS5, CTS9                           | 入力      | 送受信の開始制御用の入力端子 (調歩同期式モード/クロック同期式モード)                                                                                                                                 |

|        | RTS2~RTS5, RTS9                           | 出力      | 送受信の開始制御用の出力端子 (調歩同期式モード/クロック同期式モード)                                                                                                                                 |

|        | 【簡易 I <sup>2</sup> C モード】 <sup>(注1)</sup> |         |                                                                                                                                                                      |

|        | SSCL2~SSCL5, SSCL9                        | 入出力     | I <sup>2</sup> C クロック用の入出力端子(簡易 I <sup>2</sup> C モード)                                                                                                                |

|        | SSDA2~SSDA5, SSDA9                        | 入出力     | I <sup>2</sup> C データ用の入出力端子(簡易 I <sup>2</sup> C モード)                                                                                                                 |

|        | 【簡易 SPI モード】 <sup>(注1)</sup>              |         |                                                                                                                                                                      |

|        | SCK2~SCK5, SCK9                           | 入出力     | クロック用の入出力端子(簡易 SPI モード)                                                                                                                                              |

|        | MISO2~MISO5, MISO9                        | 入出力     | │<br>│データのスレーブ送信用の入出力端子(簡易 SPI モード)                                                                                                                                  |

|        | MOSI2~MOSI5, MOSI9                        | 入出力     | ├──<br>├データのマスタ送信用の入出力端子(簡易 SPI モード)                                                                                                                                 |

|        | SS2~SS5, SS9                              | 入力      | チップセレクト入力端子(簡易 SPI モード)                                                                                                                                              |

| IIC    | SCL0, SCL1                                | 入出力     | クロック用の入出力端子                                                                                                                                                          |

|        | SDA0, SDA1                                | 入出力     | データ用の入出力端子                                                                                                                                                           |

| SPI    | RSPCKA, RSPCKB                            | 入出力     | クロック入出力端子                                                                                                                                                            |

|        | MOSIA, MOSIB                              | 入出力     | マスタからの出力データ用の入出力端子                                                                                                                                                   |

|        | MISOA, MISOB                              | 入出力     | スレーブからの出力データ用の入出力端子                                                                                                                                                  |

|        | SSLA0, SSLB0                              | 入出力     | スレーブ選択用の入出力端子                                                                                                                                                        |

|        | SSLA1~SSLA3, SSLB1<br>~SSLB3              | 出力      | スレーブ選択用の出力端子                                                                                                                                                         |

| QSPI   | QSPCLK                                    | 出力      | QSPI のクロック出力端子                                                                                                                                                       |

|        | QSSL                                      | 出力      | QSPI スレーブ出力端子                                                                                                                                                        |

|        | QIO0~QIO3                                 | 入出力     | データ 0~データ 3                                                                                                                                                          |

| アナログ電源 | AVCC0                                     | 入力      | 14 ビット A/D コンバータ、基準電圧生成回路、温度センサのアナログ電源端子。 1.0 μF の平滑コンデンサを介して AVSSO に接続してください。平滑コンデンサは端子近くに配置してください。(注4) 使用しない場合は、端子を開放できます。使用する場合は、電源オープン制御レジスタ (VOCR) を設定してください。   |

|        | AVSS0                                     | 入力      | 14 ビット A/D コンバータ、基準電圧生成回路、温度センサ用のアナロググランド端子。<br>使用しない場合は、端子を開放できます。使用する場合は、電源オープン制御レジスタ (VOCR) を設定してください。                                                            |

|        | VREFH0                                    | 入力      | 14 ビット A/D コンバータ用のアナログ基準電圧端子。 1.0 μF の平滑コンデンサを介して VREFL0 に接続してください。 平滑コンデンサは端子近くに配置してください。 (注5) A/D コンバータを使用しない場合は AVCC0 に接続してください。 AVCC0 が供給されない場合、オープン(開放)にしてください。 |

|        | AVTRO                                     | 出力      | 基準電圧生成回路 (VREF) の基準電圧出力端子<br>10 µF の平滑コンデンサを介して VREFL0 に接続してください。                                                                                                    |

|        | VREFL0                                    | 入力      | 14 ビット A/D コンバータ用のアナログ基準グランド端子。A/D コンバータを使用しない場合は AVSSO に接続してください。AVCCOが供給されない場合、オープン(開放)にしてください。                                                                    |

### 表 1.14 端子機能一覧 (5/5)

| 機能      | 端子名                                        | 入出力 | 説明                           |

|---------|--------------------------------------------|-----|------------------------------|

| ADC14   | AN000~AN007, AN016,<br>AN017, AN020, AN021 | 入力  | A/D コンバータで処理されるアナログ信号用の入力端子  |

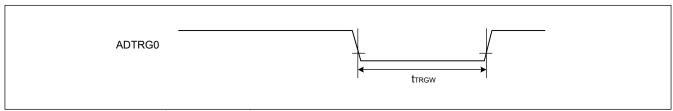

|         | ADTRG0                                     | 入力  | A/D 変換を開始する外部トリガ信号用の入力端子     |

| MLCD    | MLCD_VCOM                                  | 出力  | コモン電極極性信号端子                  |

|         | MLCD_XRST                                  | 出力  | 液晶表示制御出力端子                   |

|         | MLCD_SCLK                                  | 出力  | 通信用シリアル出力クロック端子              |

|         | MLCD_DEN                                   | 出力  | データ識別信号端子                    |

|         | MLCD_ENBS                                  | 出力  | 水平方向データイネーブル端子               |

|         | MLCD_ENBG                                  | 出力  | 垂直方向データイネーブル端子               |

|         | MLCD_SI0~MLCD_SI7                          | 出力  | 画像データ信号端子                    |

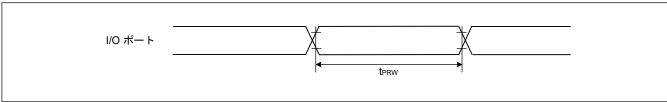

| I/O ポート | P000~P007, P010~<br>P015                   | 入出力 | 14 ビットの入出力端子                 |

|         | P100-P113                                  | 入出力 | 14 ビットの入出力端子                 |

|         | P200                                       | 入力  | 1 ビットの入力専用端子。NMI 端子と兼用。      |

|         | P201~P205, P207~<br>P210                   | 入出力 | 8 ビットの入出力端子                  |

|         | P300~P302, P314~<br>P315                   | 入出力 | 5 ビットの入出力端子                  |

|         | P409~P411                                  | 入出力 | 3 ビットの入出力端子                  |

|         | P412, P413                                 | 入出力 | 2ビットの入出力端子。EXTAL、XTAL 端子と兼用。 |

|         | P500, P501, P508~P511                      | 入出力 | 6 ビットの入出力端子                  |

|         | P600~P604                                  | 入出力 | 5 ビットの入出力端子                  |

|         | P700~P704                                  | 入出力 | 5 ビットの入出力端子                  |

|         | P806~P815                                  | 入出力 | 10 ビットの入出力端子                 |

- 注. 平滑コンデンサには積層セラミックコンデンサをお使いください。

- 注 1. SCIi、SCIg における各モードの通信端子は、以下の通り同一端子に兼用されています。RXDn/SCLn/MISOn, TXDn/SDAn/MOSIn, CTSn/RTSn/SSn

- 注 2. 外来ノイズが多い環境では、外来ノイズへの耐性と回路の安定動作を向上させるために、電流源の近傍に任意で 10 µF の平滑コンデンサを介して VSS に接続してください。

- 注 3. IOVCC0/1 のそれぞれの端子で、同電位で接続した端子があれば、10  $\mu$ F の平滑コンデンサは共有できます。VCC/IOVCC と接続した場合は、10  $\mu$ F の平滑コンデンサは不要です。

- 注 4. 外来ノイズが多い環境では、外来ノイズへの耐性と回路の安定動作を向上させるために、電流源の近傍に任意で 10 µF の平滑コンデンサを介して AVSSO に接続してください。

- 注 5. 外来ノイズが多い環境では、外来ノイズへの耐性と回路の安定動作を向上させるために、電流源の近傍に任意で 10 µF の平滑コンデンサを介して VREFLO に接続してください。

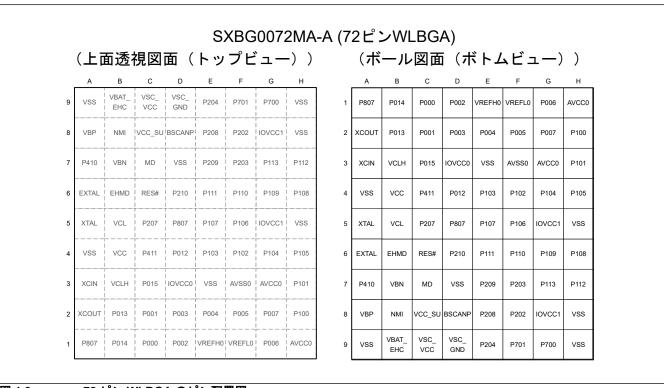

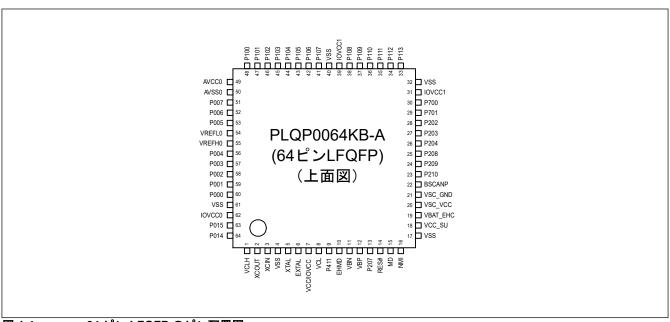

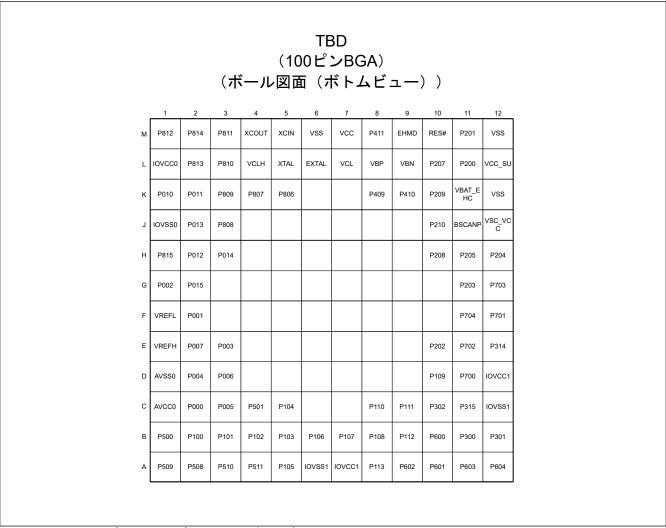

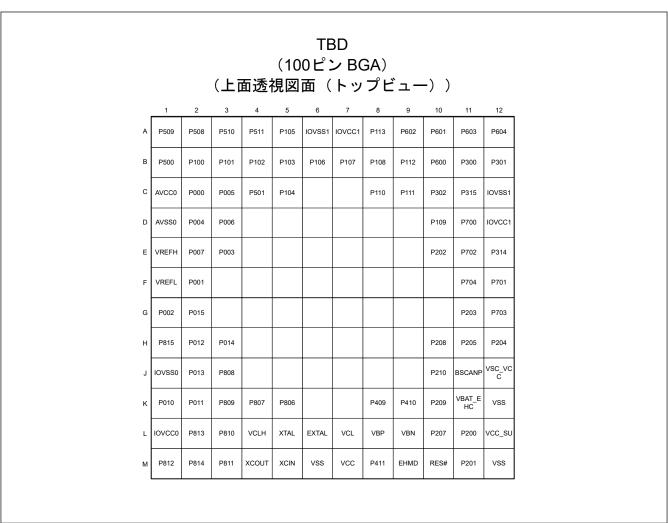

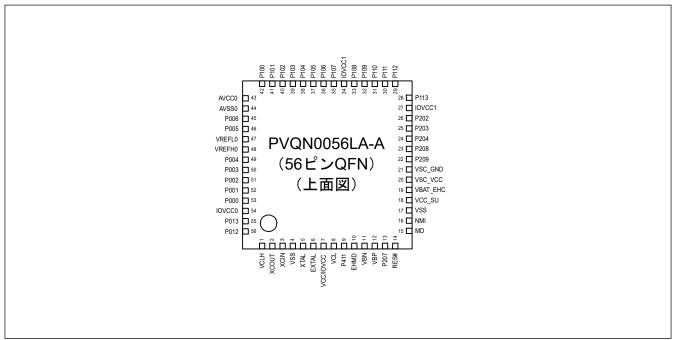

### 1.6 ピン配置図

図 1.2、図 1.3、図 1.4 は、ピン配置の上面図を示しています。ピン配置図には、電源端子、I/O ポートを記載しています。

図 1.2 100 ピン LFQFP のピン配置図

図 1.3 72 ピン WLBGA のピン配置図

図 1.4 64 ピン LFQFP のピン配置図

図 1.5 100 ピン BGA のピン配置図(ボトムビュー)

図 1.6 100 ピン BGA のピン配置図(トップビュー)

図 1.7 56 ピン QFN のピン配置図

# 1.7 端子一覧

## 表 1.15 端子一覧 (1/3)

| 4X I            | 5 1.15       |                |                |              |                         |         |                                                           |                             |               |                        |                 |        |

|-----------------|--------------|----------------|----------------|--------------|-------------------------|---------|-----------------------------------------------------------|-----------------------------|---------------|------------------------|-----------------|--------|

| 100 ピン<br>LFQFP | 100 ば<br>BGA | 72 ピソ<br>WLBGA | 64 ピン<br>LFGFP | 56 ピン<br>QFN | <b>電源、システム、</b><br>クロック | 1/0 ポート | タイマ<br>(CAC, CCC, GPT, AGT, AGTW,<br>TMR, WUPT, RTC)      | 通信<br>(SCI, SPI, IIC, QSPI) | 表示系<br>(MLCD) | 外部割り込み<br>(IRQn, KINT) | アナログ<br>(ADC14) | 電源     |

| 1               | M1           | _              | _              | _            |                         | P812    | AGTWEE1_B                                                 | TXD4_C/QSPCLK_A             |               |                        |                 | IOVCC0 |

| 2               | М3           | _              | _              | _            |                         | P811    | AGTWIO1_B                                                 | QIO0_A                      |               |                        |                 | IOVCC0 |

| 3               | L3           | _              | _              | _            |                         | P810    | AGTIO1_B/GTIOC3A_B                                        | QIO1_A                      |               | IRQ5_B                 |                 | IOVCC0 |

| 4               | К3           | _              | _              | _            |                         | P809    | AGTEE1_B/GTIOC3B_B                                        | QIO2_A                      |               | IRQ6_B                 |                 | IOVCC0 |

| 5               | J3           | F5             | _              | _            |                         | P808    | AGTO1_B                                                   | RXD3_B/QIO3_A               |               | IRQ2_B                 |                 | IOVCC0 |

| 6               | K4           | E4             | _              | _            |                         | P807    | AGTOA1_B                                                  | CTS3_B/QSSL_A               |               | IRQ6_A                 |                 | IOVCC0 |

| 7               | K5           | _              | _              | _            |                         | P806    | AGTOB1_B                                                  |                             |               |                        |                 | IOVCC0 |

| 8               | L4           | G2             | 1              | 1            | VCLH                    |         |                                                           |                             |               |                        |                 |        |

| 9               | M4           | H1             | 2              | 2            | XCOUT                   |         |                                                           |                             |               |                        |                 | IOVCC  |

| 10              | M5           | G1             | 3              | 3            | XCIN                    |         |                                                           |                             |               |                        |                 | IOVCC  |

| 11              | М6           | F1             | 4              | 4            | VSS                     |         |                                                           |                             |               |                        |                 |        |

| 12              | L5           | E1             | 5              | 5            | XTAL                    | P413    | GTIOC0A_A                                                 | TXD3_A                      |               |                        |                 | IOVCC  |

| 13              | L6           | D1             | 6              | 6            | EXTAL                   | P412    | GTIOC0B_A                                                 | RXD3_A                      |               |                        |                 | IOVCC  |

| 14              | M7           | F2             | 7              | 7            | VCC/IOVCC               |         |                                                           |                             |               |                        |                 |        |

| 15              | L7           | E2             | 8              | 8            | VCL                     |         |                                                           |                             |               |                        |                 |        |

| 16              | M8           | F3             | 9              | 9            | CLKOUT32K_A             | P411    | AGTWEE1_A/GTIOC0B_B                                       | TXD9_A/SCK3_A               |               | IRQ0_A_DS              |                 | IOVCC  |

| 17              | K9           | C1             | _              | _            |                         | P410    |                                                           |                             |               | IRQ9_A                 |                 | IOVCC  |

| 18              | K8           | _              | _              | _            | CLKOUT32K_B             | P409    |                                                           |                             |               | IRQ9_B                 |                 | IOVCC  |