# **Analog Front End Wideband Mixed-Signal Transceiver**

Check for Samples: AFE7222, AFE7225

# 1 INTRODUCTION

# 1.1 FEATURES

- AFE7225

- Dual 12-Bit 250MSPS TX DACs

- Dual 12-Bit 125MSPS RX ADCs

- AFE7222

- Dual 12-Bit 130MSPS TX DACs

- Dual 12-Bit 65MSPS RX ADCs

- OPTIONS

- Dual 12-Bit Auxiliary DACs

- Dual Input 12-Bit Auxiliary ADC

- TX Path Interpolation by 2 or 4

- RX Path Decimation by 2

- 3.0V/1.8V Supplies, Low Power

- Fast Wakeup Modes for Half-Duplex

- Coarse or Fine Digital Mixer

- Quadrature Modulation Corrections

- Clock Input Divide/Multiply

- Serial LVDS or Interleaved Parallel CMOS Interface

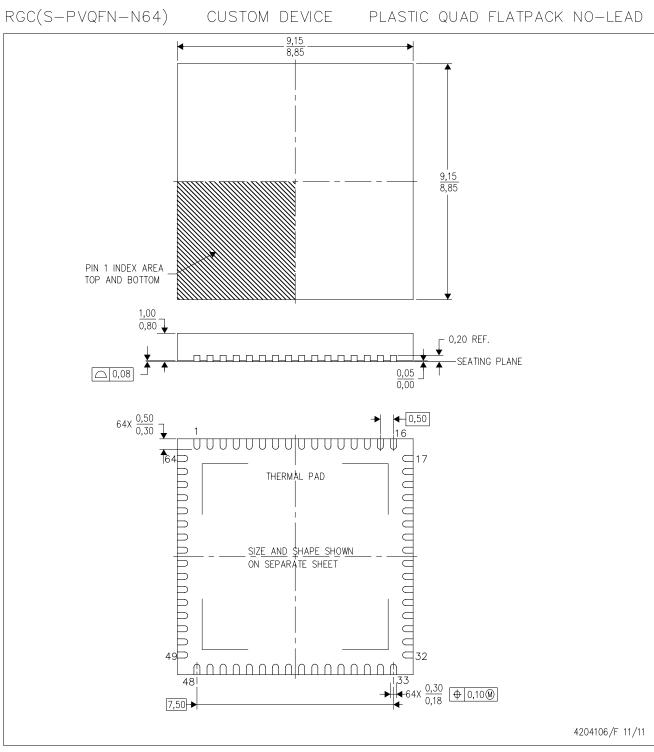

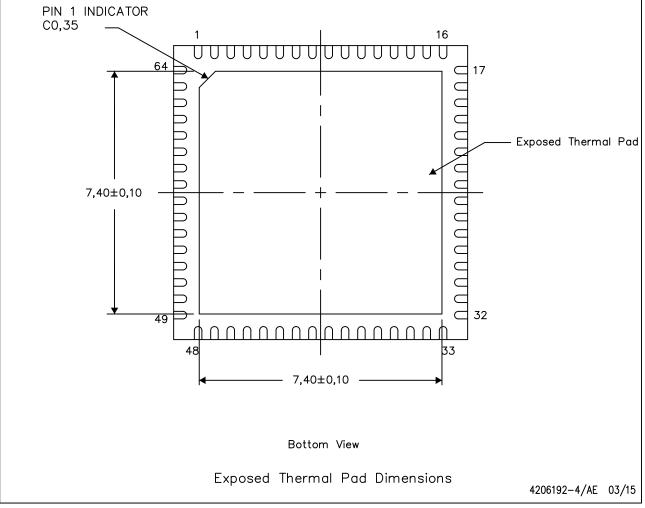

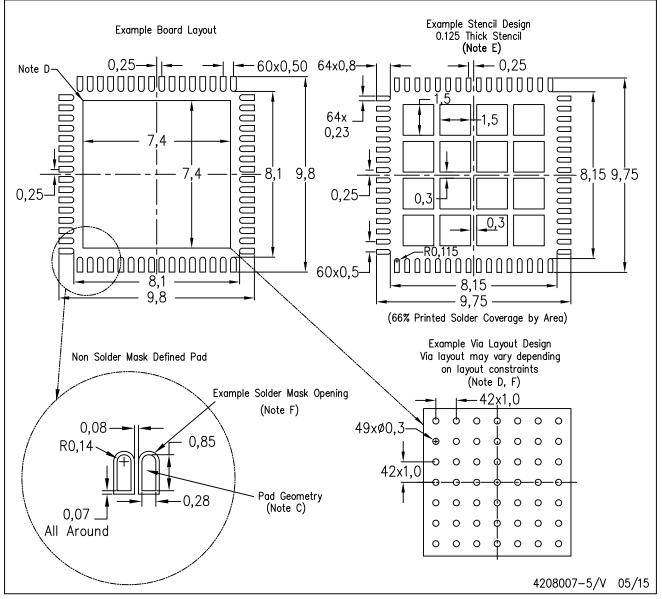

- 64-Pin QFN Package (9mm × 9mm)

#### 1.2 APPLICATIONS

- · Portable, Low Power Radio

- · Wireless Infrastructure

- · Point-to-Point Radio

- Pico-Cell BTS

# 1.3 DESCRIPTION

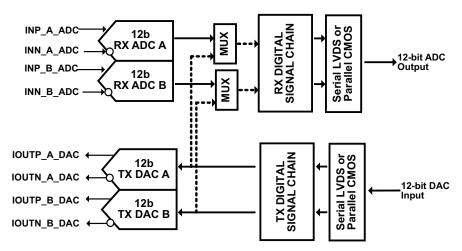

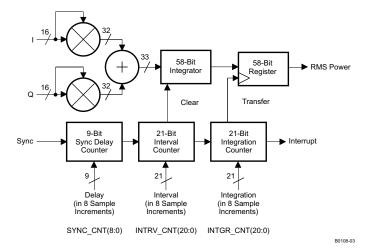

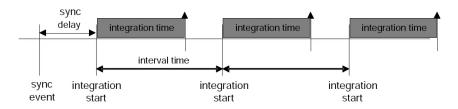

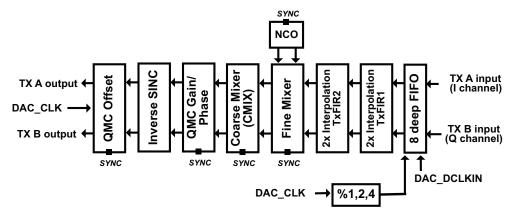

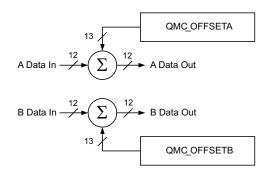

The AFE7225/7222 is an analog front end designed for full- or half-duplex radios. Over-sampling transmit 12-bit DACs provide output frequencies from baseband to Nyquist. Under-sampling receive 12-bit ADCs allow analog inputs from baseband to ~230MHz. Most blocks within the AFE7225/7222 are independently controlled for optimization of power consumption versus utilization. Two auxiliary control 12-bit DACs and a dual input auxiliary monitoring 12-bit ADC are available via serial interface. Digital features include QMC (quadrature modulation correction), interpolation, decimation, RMS/peak power meter and mixers with independent NCOs for RX and TX path.

The AFE7225/7222 is available in a 64-pin 9x9mm QFN package (RGC). The AFE7225/7222 is built on Texas Instrument's low power analog CMOS process and is specified over the full industrial temperature range (–40°C to 85°C).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

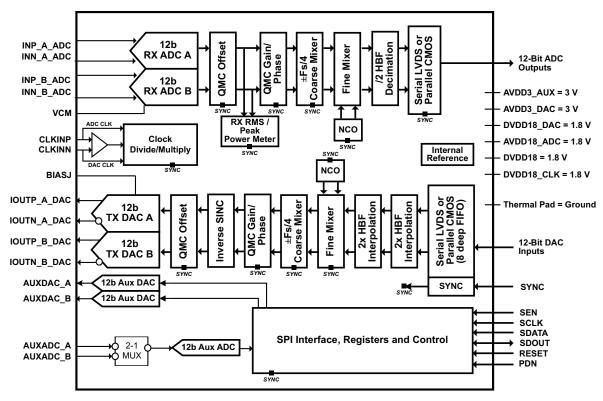

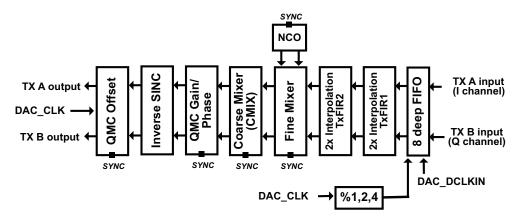

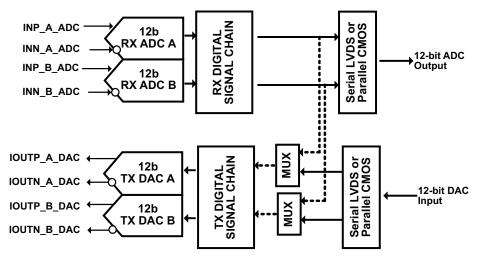

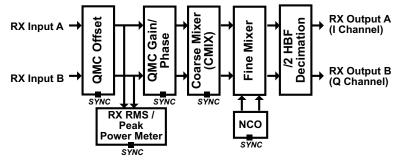

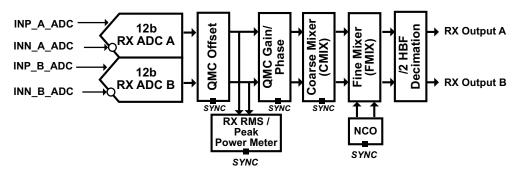

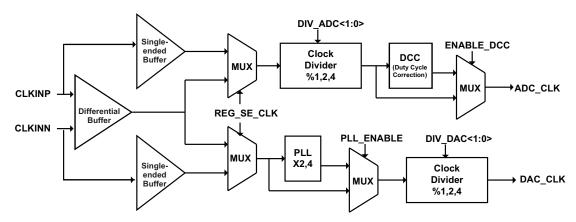

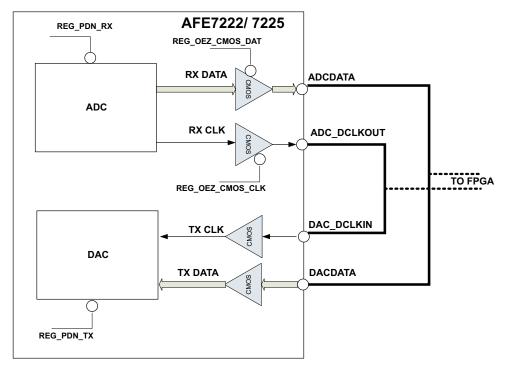

# 1.4 DETAILED BLOCK DIAGRAM

Figure 1-1. Block Diagram of AFE7222/AFE7225

#### 2 DEVICE INFORMATION

#### 2.1 PACKAGE/ORDERING INFORMATION

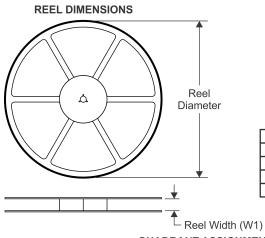

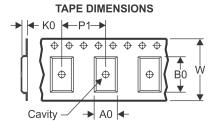

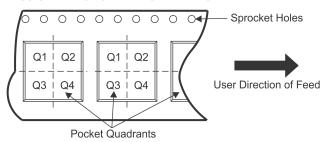

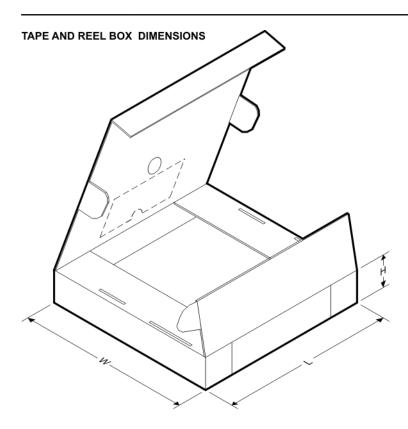

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA,<br>QUANTITY |

|---------|--------------|-----------------------|-----------------------------------|--------------------|--------------------|---------------------------------|

|         |              |                       |                                   |                    | AFE7222IRGCT       | Tape and Reel                   |

| AFE7222 | QFN-64       | RGC                   | -40°C to 85°C                     | AFE7222I           | AFE7222IRGCR       | Tape and Reel                   |

|         |              |                       |                                   |                    | AFE7222IRGC25      | Tape and Reel                   |

|         |              |                       |                                   |                    | AFE7225IRGCT       | Tape and Reel                   |

| AFE7225 | QFN-64       | RGC                   | –40°C to 85°C                     | AFE7225I           | AFE7225IRGCR       | Tape and Reel                   |

|         |              |                       |                                   |                    | AFE7225IRGC25      | Tape and Reel                   |

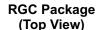

# 2.2 DEVICE PINOUT, CMOS INPUT/OUTPUT MODE

Figure 2-1. Device Pinout, CMOS Input/Output Mode

# Table 2-1. Pin Configuration: CMOS Input/Output Mode

|     | PIN         | DECORPORATION                                                                                                   |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | DESCRIPTION                                                                                                     |

| 1   | AVDD18_ADC  | 1.8V supply for RX ADCs                                                                                         |

| 2   | INN_B_ADC   | RX ADC channel B analog input, negative                                                                         |

| 3   | INP_B_ADC   | RX ADC channel B analog input, positive                                                                         |

| 4   | AVDD18_ADC  | 1.8V supply for RX ADCs                                                                                         |

| 5   | INN_A_ADC   | RX ADC channel A analog input, negative                                                                         |

| 6   | INP_A_ADC   | RX ADC channel A analog input, positive                                                                         |

| 7   | AVDD18_ADC  | 1.8V supply for RX ADCs                                                                                         |

| 8   | CLKINN      | main clock input, negative side if differential mode, TX side if single-ended 2 clock mode                      |

| 9   | CLKINP      | main clock input, positive side if differential mode, RX side if single-ended 2 clock mode                      |

| 10  | DVDD18_CLK  | 1.8V supply for Clocking circuit                                                                                |

| 11  | AVDD3_DAC   | 3V supply for TX DACs                                                                                           |

| 12  | IOUTP_A_DAC | TX DAC channel A current output, positive (current sink DACs)                                                   |

| 13  | IOUTN_A_DAC | TX DAC channel A current output, negative (current sink DACs)                                                   |

| 14  | AVDD3_DAC   | 3V supply for TX DACs                                                                                           |

| 15  | IOUTP_B_DAC | TX DAC channel B current output, positive (current sink DACs)                                                   |

| 16  | IOUTN_B_DAC | TX DAC channel B current output, negative (current sink DACs)                                                   |

| 17  | AVDD3_DAC   | 3V supply for TX DACs                                                                                           |

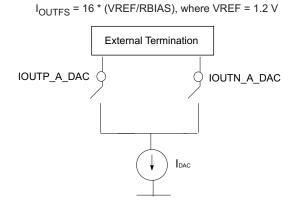

| 18  | BIASJ       | sets the TX DAC output current (resistor from pin to ground). Use 960 Ohm to set a full scale current of 20 mA. |

| 19  | DVDD18_DAC  | 1.8V DAC digital supply                                                                                         |

| 20  | AUXDAC_A    | auxiliary DAC channel A output, current sourcing up to 7.5mA (SPI programmable)                                 |

| 21  | AUXDAC_B    | auxiliary DAC channel B output, current sourcing up to 7.5mA (SPI programmable)                                 |

| 22  | AVDD3_AUX   | 3V supply for auxiliary ADC/DACs                                                                                |

| 23  | AUXADC_A    | auxiliary ADC channel A input                                                                                   |

| 24  | AUXADC_B    | auxiliary ADC channel B input                                                                                   |

| 25  | AVDD18_ADC  | 1.8V supply for RX ADCs                                                                                         |

| 26  | DACDATA11   | CMOS data input for TX data, MSB of TX DACs                                                                     |

| 27  | DACDATA10   | CMOS data input for TX data                                                                                     |

| 28  | DACDATA9    | CMOS data input for TX data                                                                                     |

| 29  | DACDATA8    | CMOS data input for TX data                                                                                     |

| 30  | DACDATA7    | CMOS data input for TX data                                                                                     |

| 31  | DACDATA6    | CMOS data input for TX data                                                                                     |

| 32  | DVDD18      | 1.8V supply for digital interface                                                                               |

| 33  | DACDATA5    | CMOS data input for TX data                                                                                     |

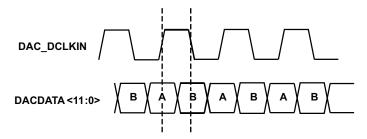

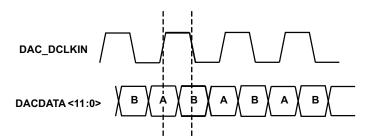

| 34  | DAC_DCLKIN  | CMOS clock input for TX data. Send clock with data.                                                             |

| 35  | DACDATA4    | CMOS data input for TX data                                                                                     |

| 36  | DACDATA3    | CMOS data input for TX data                                                                                     |

| 37  | DACDATA2    | CMOS data input for TX data                                                                                     |

| 38  | DACDATA1    | CMOS data input for TX data                                                                                     |

| 39  | DACDATA0    | CMOS data input for TX data. LSB of TX DACs                                                                     |

| 40  | SYNCIN      | CMOS sync input. Used to reset internal clock dividers and reset TX data FIFO pointer                           |

| 41  | DVDD18      | 1.8V supply for digital interface                                                                               |

| 42  | ADCDATA11   | CMOS data output for RX data, MSB of RX ADCs                                                                    |

| 43  | ADCDATA10   | CMOS data output for RX data                                                                                    |

| 44  | ADCDATA9    | CMOS data output for RX data                                                                                    |

| 45  | ADCDATA8    | CMOS data output for RX data                                                                                    |

| 46  | ADCDATA7    | CMOS data output for RX data                                                                                    |

# Table 2-1. Pin Configuration: CMOS Input/Output Mode (continued)

|             | PIN         | DECORIDATION                                                                                                            |

|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| NO.         | NAME        | DESCRIPTION                                                                                                             |

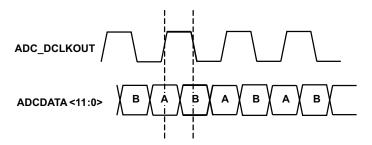

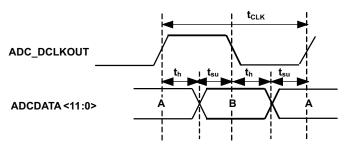

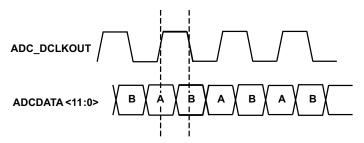

| 47          | ADC_DCLKOUT | CMOS clock output for RX data                                                                                           |

| 48          | ADCDATA6    | CMOS data output for RX data                                                                                            |

| 49          | DVDD18      | 1.8V supply for digital interface                                                                                       |

| 50          | ADCDATA5    | CMOS data output for RX data                                                                                            |

| 51          | ADCDATA4    | CMOS data output for RX data                                                                                            |

| 52          | ADCDATA3    | CMOS data output for RX data                                                                                            |

| 53          | ADCDATA2    | CMOS data output for RX data                                                                                            |

| 54          | ADCDATA1    | CMOS data output for RX data                                                                                            |

| 55          | ADCDATA0    | CMOS data output for RX data, LSB of RX ADCs                                                                            |

| 56          | PDN         | Can be programmed as global powerdown (deep sleep), fast recovery powerdown (light sleep) or TX/RX switch. Active high. |

| 57          | SEN         | SPI enable (1.8V CMOS)                                                                                                  |

| 58          | SDATA       | SPI data input (1.8V CMOS)                                                                                              |

| 59          | SCLK        | SPI clock input (1.8V CMOS)                                                                                             |

| 60          | SDOUT       | SPI data output (1.8V CMOS)                                                                                             |

| 61          | RESET       | Reset the SPI. Active high (1.8V CMOS).                                                                                 |

| 62          | AVDD18_ADC  | 1.8V supply for RX ADCs                                                                                                 |

| 63          | VCM         | Common mode voltage output. Outputs the ideal common mode input voltage for the ADC. Nominally around 0.95V.            |

| 64          | AVDD18_ADC  | 1.8V supply for RX ADCs                                                                                                 |

| Thermal pad | VSS         | Connect thermal pad to the board ground                                                                                 |

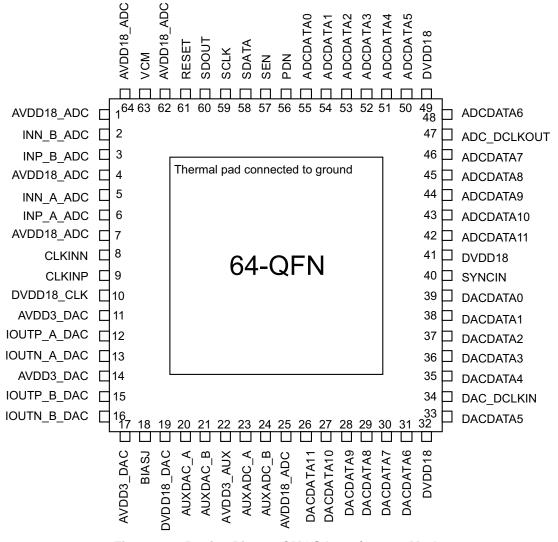

# 2.3 DEVICE PINOUT, LVDS INPUT/OUTPUT MODE

Figure 2-2. Device Pinout, LVDS Input/Output Mode

Table 2-2. Pin Configuration: LVDS Input/Output Mode

|     | PIN        | DESCRIPTION                                                                                |  |  |  |

|-----|------------|--------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME       | DESCRIPTION                                                                                |  |  |  |

| 1   | AVDD18_ADC | 1.8V supply for RX ADCs                                                                    |  |  |  |

| 2   | INN_B_ADC  | RX ADC channel B analog input, negative                                                    |  |  |  |

| 3   | INP_B_ADC  | RX ADC channel B analog input, positive                                                    |  |  |  |

| 4   | AVDD18_ADC | 1.8V supply for RX ADCs                                                                    |  |  |  |

| 5   | INN_A_ADC  | RX ADC channel A analog input, negative                                                    |  |  |  |

| 6   | INP_A_ADC  | RX ADC channel A analog input, positive                                                    |  |  |  |

| 7   | AVDD18_ADC | 1.8V supply for RX ADCs                                                                    |  |  |  |

| 8   | CLKINN     | main clock input, negative side if differential mode, TX side if single-ended 2 clock mode |  |  |  |

# Table 2-2. Pin Configuration: LVDS Input/Output Mode (continued)

|        | PIN          |                                                                                                                 |

|--------|--------------|-----------------------------------------------------------------------------------------------------------------|

| NO.    | NAME         | DESCRIPTION                                                                                                     |

| 9      | CLKINP       | main clock input, positive side if differential mode, RX side if single-ended 2 clock mode                      |

| 10     | DVDD18_CLK   | 1.8V supply for Clocking circuit                                                                                |

| 11     | AVDD3_DAC    | 3V supply for TX DACs                                                                                           |

| 12     | IOUTP_A_DAC  | TX DAC channel A current output, positive (current sink DACs)                                                   |

| 13     | IOUTN_A_DAC  | TX DAC channel A current output, negative (current sink DACs)                                                   |

| 14     | AVDD3_DAC    | 3V supply for TX DACs                                                                                           |

| 15     | IOUTP_B_DAC  | TX DAC channel B current output, positive (current sink DACs)                                                   |

| 16     | IOUTN_B_DAC  | TX DAC channel B current output, negative (current sink DACs)                                                   |

| 17     | AVDD3_DAC    | 3V supply for TX DACs                                                                                           |

| 18     | BIASJ        | sets the TX DAC output current (resistor from pin to ground). Use 960 Ohm to set a full scale current of 20 mA. |

| 19     | DVDD18_DAC   | 1.8V DAC digital supply                                                                                         |

| 20     | AUXDAC_A     | auxiliary DAC channel A output, current sourcing up to 7.5mA (SPI programmable)                                 |

| 21     | AUXDAC_B     | auxiliary DAC channel B output, current sourcing up to 7.5mA (SPI programmable)                                 |

| 22     | AVDD3_AUX    | 3V supply for auxiliary ADC/DACs                                                                                |

| 23     | AUXADC_A     | auxiliary ADC channel A input                                                                                   |

| 24     | AUXADC_B     | auxiliary ADC channel B input                                                                                   |

| 25     | AVDD18_ADC   | 1.8V supply for RX ADCs                                                                                         |

| 26, 27 |              | LVDS Wire 1 data input for Channel A TX data – inactive in 1-wire mode, LSB byte in 2-wire mode                 |

| 26     | DAC_DATA_11  | Positive                                                                                                        |

| 27     | DAC_DATA_10  | Negative                                                                                                        |

| 28, 29 |              | LVDS Wire 0 data input for Channel A TX data – active in 1-wire mode, MSB byte in 2-wire mode                   |

| 28     | DAC_DATA_9   | Positive                                                                                                        |

| 29     | DAC_DATA_8   | Negative                                                                                                        |

| 30, 31 |              | LVDS frame clock input                                                                                          |

| 30     | DAC_FCLKINP  | Positive                                                                                                        |

| 31     | DAC_FCLKINN  | Negative                                                                                                        |

| 32     | DVDD18       | 1.8V supply for digital interface                                                                               |

| 33, 34 |              | LVDS bit clock input                                                                                            |

| 33     | DAC_DCLKINP  | Positive                                                                                                        |

| 34     | DAC_DCLKINN  | Negative                                                                                                        |

| 35, 36 |              | LVDS Wire 0 data input for Channel B TX data – active in 1-wire mode, LSB byte in 2-wire mode                   |

| 35     | DACB_DATA_0P | Positive                                                                                                        |

| 36     | DACB_DATA_0N | Negative                                                                                                        |

| 37, 38 |              | LVDS Wire 1 data input for Channel B TX data – inactive in 1-wire mode, MSB byte in 2-wire mode                 |

| 37     | DACB_DATA_1P | Positive                                                                                                        |

| 38     | DACB_DATA_1N | Negative                                                                                                        |

| 39, 40 | 0)/10/1/15   | LVDS SYNC input – Used to reset internal clock dividers and reset TX data FIFO pointer                          |

| 39     | SYNCINP      | Positive                                                                                                        |

| 40     | SYNCINN      | Negative                                                                                                        |

| 41     | DVDD18       | 1.8V supply for digital interface                                                                               |

| 42, 43 | ADOD DATA 41 | LVDS Wire 1 data output for Channel B RX data – inactive in 1-wire mode, MSB byte in 2-wire mode                |

| 42     | ADCB_DATA_1D | Positive                                                                                                        |

| 43     | ADCB_DATA_1P | Negative                                                                                                        |

| 44, 45 | ADCD DATA ON | LVDS Wire 0 data output for Channel B RX data – active in 1-wire mode, LSB byte in 2-wire mode                  |

| 44     | ADCB_DATA_OR | Positive                                                                                                        |

| 45     | ADCB_DATA_0P | Negative                                                                                                        |

# Table 2-2. Pin Configuration: LVDS Input/Output Mode (continued)

|             | PIN          |                                                                                                                         |

|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------|

| NO.         | NAME         | DESCRIPTION                                                                                                             |

| 46, 47      |              | LVDS frame clock output                                                                                                 |

| 46          | ADC_FCLKOUTN | Positive                                                                                                                |

| 47          | ADC_FCLKOUTP | Negative                                                                                                                |

| 48          | NC           | No Connect                                                                                                              |

| 49          | DVDD18       | 1.8V supply for digital interface                                                                                       |

| 50, 51      |              | LVDS bit clock output                                                                                                   |

| 50          | ADC_DCLKOUTN | Positive                                                                                                                |

| 51          | ADCDCLKOUTP  | Negative                                                                                                                |

| 52,53       |              | LVDS Wire 0 data output for Channel A RX data – active in 1-wire mode, MSB byte in 2-wire mode                          |

| 52          | ADCA_DATA_0N | Positive                                                                                                                |

| 53          | ADCA_DATA_0P | Negative                                                                                                                |

| 54,55       |              | LVDS Wire 1 data output for Channel A RX data – inactive in 1-wire mode, LSB byte in 2-wire mode                        |

| 54          | ADCA_DATA_1N | Positive                                                                                                                |

| 55          | ADCA_DATA_1P | Negative                                                                                                                |

| 56          | PDN          | Can be programmed as global powerdown (deep sleep), fast recovery powerdown (light sleep) or TX/RX switch. Active high. |

| 57          | SEN          | SPI enable (1.8V CMOS)                                                                                                  |

| 58          | SDATA        | SPI data input (1.8V CMOS)                                                                                              |

| 59          | SCLK         | SPI clock input (1.8V CMOS)                                                                                             |

| 60          | SDOUT        | SPI data output (1.8V CMOS)                                                                                             |

| 61          | RESET        | Reset the SPI. Active high (1.8V CMOS).                                                                                 |

| 62          | AVDD18_ADC   | 1.8V supply for RX ADCs                                                                                                 |

| 63          | VCM          | Common mode voltage output. Outputs the ideal common mode input voltage for the ADC. Nominally around 0.95V.            |

| 64          | AVDD18_ADC   | 1.8V supply for RX ADCs                                                                                                 |

| Thermal pad | VSS          | Connect thermal pad to the board ground                                                                                 |

# **ELECTRICAL SPECIFICATIONS**

#### ABSOLUTE MAXIMUM RATINGS(1) 3.1

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                                | MIN  | MAX | UNIT |

|------------------|--------------------------------------------------------------------------------|------|-----|------|

|                  | Supply voltage range, *VDD3*                                                   | -0.3 | 3.6 | V    |

|                  | Supply voltage range, *VDD18*                                                  | -0.3 | 2.1 | V    |

|                  | Voltage betweeen *VDD3* to *VDD18*                                             | -2.4 | 3.9 | V    |

|                  | INP_A_ADC, INM_A_ADC, INP_B_ADC, INM_B_ADC, AUXADC_A, AUXADC_B, CLKINN, CLKINP | -0.3 | 2.1 | V    |

|                  | RESET, SCLK, SDATA SEN                                                         | -0.3 | 3.9 | V    |

|                  | DAC*_DATA_nP/M, DAC_DCLK                                                       | -0.3 | 2.1 | V    |

| T <sub>A</sub>   | Operating free-air temperature range                                           | -40  | 85  | °C   |

| $T_{J}$          | Operating junction tamperature range                                           |      | 125 | °C   |

| T <sub>stg</sub> | Storage temperature range                                                      | -65  | 150 | °C   |

|                  | ESD rating Human Body Model (HBM)                                              |      | 2   | kV   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

#### 3.2 THERMAL INFORMATION

|                         |                                              | AFE7222/AFE7225 |        |

|-------------------------|----------------------------------------------|-----------------|--------|

|                         | THERMAL METRIC                               | RGC PACKAGE     | UNITS  |

|                         |                                              | 64 PINS         |        |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 22.8            |        |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance    | 6.7             |        |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 2.3             | °C/W   |

| ΨЈТ                     | Junction-to-top characterization parameter   | 0.1             | · C/VV |

| ΨЈВ                     | Junction-to-board characterization parameter | 2.2             |        |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 0.2             |        |

#### 3.3 RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

| DADAMETED                              | TEST CONDITIONS | AFE7222  |       |          |                    |       |                                               |      |

|----------------------------------------|-----------------|----------|-------|----------|--------------------|-------|-----------------------------------------------|------|

| PARAMETER                              | TEST CONDITIONS | MIN      | TYP   | MAX      | MIN                | TYP   | 1.8 1.9 \(\frac{1}{3}\).0 3.6 \(\frac{1}{3}\) | UNIT |

| DVDD18 voltage range                   |                 | 1.7      | 1.8   | 1.9      | 1.7                | 1.8   | 1.9                                           | V    |

| AVDD3 voltage range                    |                 | 2.85     | 3.0   | 3.6      | 2.85               | 3.0   | 3.6                                           | V    |

| Common mode voltage at ADC input pins  |                 | VCM-0.05 | VCM   | VCM+0.05 | VCM-0.05           | VCM   | VCM+0.05                                      | V    |

| Common mode voltage at DAC output pins |                 |          | AVDD3 |          |                    | AVDD3 |                                               | V    |

| ADC_CLK speed <sup>(1)</sup>           |                 | 2.5(2)   |       | 65       | 2.5 <sup>(2)</sup> |       | 125                                           | MSPS |

| DAC_CLK speed <sup>(1)</sup>           |                 | 1        |       | 130      | 1                  |       | 250                                           | MSPS |

- See Table 10-1 and Table 10-2 for corresponding maximum interface rates.

- Minimum ADC\_CLK speed can be reduced to 0.8 MSPS by writing the following serial interface registers:

- Register address 0x208, value 0x8

- Register address 0x4, value 0x8

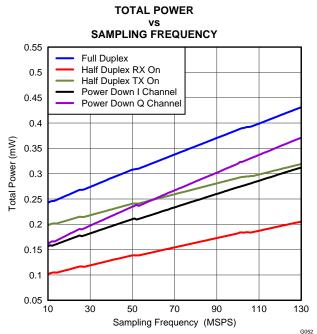

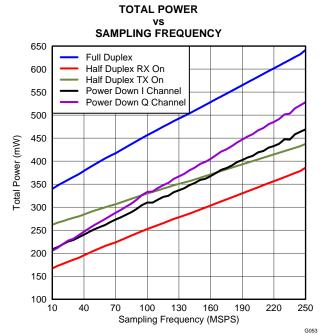

#### 3.4 SUPPLY CHARACTERISTICS

AVDD18\_ADC=1.8V, DVDD18\_CLK=1.8V, DVDD18=1.8V, DVDD18\_DAC=1.8V, AVDD3\_DAC=3.0V, AVDD3\_AUX=3.0V, IOUTFS=20mA, typical values at  $T_A = 25^{\circ}$ C, full temperature range is  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, unless otherwise noted.

| PARAMETER                               | TEST CONDITION                                                                                                                                                                   | DNS                                                                                                                                                                 | AF                                                                                                                                           | E7225                                                                                                                                |     |          |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|----------|

| POWER IN LVDS MODE                      |                                                                                                                                                                                  |                                                                                                                                                                     | Dual RX ADC, Dual TX DAC with Interpolate by 2, 2-wire LVDS interface FADCCLK = 125 MSPS fADCIN = 10 MHz FDACCLK = 250 MSPS fDACOUT = 10 MHz |                                                                                                                                      |     | UNIT     |

|                                         |                                                                                                                                                                                  |                                                                                                                                                                     | MIN                                                                                                                                          | TYP                                                                                                                                  | MAX |          |

| Power dissipation, full duplex mode     | RX and TX active, No input signal applied on A                                                                                                                                   | ADC and DAC                                                                                                                                                         |                                                                                                                                              | 577                                                                                                                                  | 650 | mW       |

|                                         | AVDD18_ADC, RX and TX active, No input sign                                                                                                                                      | gnal applied on ADC and DAC                                                                                                                                         |                                                                                                                                              | 115                                                                                                                                  |     |          |

|                                         | DVDD18, RX and TX active, No input signal a                                                                                                                                      | oplied on ADC and DAC                                                                                                                                               |                                                                                                                                              | 95                                                                                                                                   |     |          |

| Supply current, full duplex mode        | DVDD18_CLK, RX and TX active, No input sign                                                                                                                                      | nal applied on ADC and DAC                                                                                                                                          |                                                                                                                                              | 12                                                                                                                                   |     | mΛ       |

| Зарріў сапені, напааріёх mode           | DVDD18_DAC, RX and TX active, No input sign                                                                                                                                      | gnal applied on ADC and DAC                                                                                                                                         |                                                                                                                                              | 7                                                                                                                                    |     | mA       |

|                                         | AVDD3_DAC, RX and TX active, No input sign                                                                                                                                       | nal applied on ADC and DAC                                                                                                                                          |                                                                                                                                              | 48                                                                                                                                   |     |          |

|                                         | AVDD3_AUX, RX and TX active, No input sign                                                                                                                                       | nal applied on ADC and DAC                                                                                                                                          |                                                                                                                                              | 7                                                                                                                                    |     |          |

| Power dissipation, half duplex RX mode  | RX active, TX in light sleep, TX clock is off, No DAC                                                                                                                            | input signal applied on ADC and                                                                                                                                     |                                                                                                                                              | 362                                                                                                                                  | 417 | mW       |

| Power dissipation, half duplex TX mode  | TX active, RX in light sleep, RX clock is on, No and DAC                                                                                                                         |                                                                                                                                                                     | 419                                                                                                                                          | 482                                                                                                                                  | mW  |          |

|                                         | Global powerdown enabled                                                                                                                                                         |                                                                                                                                                                     | 12                                                                                                                                           | 40                                                                                                                                   |     |          |

| Power dissipation in Sleep modes        | Fast recovery powerdown enabled, TX/RX slee                                                                                                                                      |                                                                                                                                                                     | 215                                                                                                                                          | 246                                                                                                                                  | mW  |          |

|                                         | Fast recovery powerdown enabled, TX/RX slee                                                                                                                                      |                                                                                                                                                                     | 177                                                                                                                                          | 231                                                                                                                                  |     |          |

| PARAMETER                               | TEST CONDITION                                                                                                                                                                   | DNS                                                                                                                                                                 | AFE722                                                                                                                                       | 2/AFE72                                                                                                                              | 25  |          |

| POWER IN CMOS MODE                      |                                                                                                                                                                                  |                                                                                                                                                                     |                                                                                                                                              | Dual RX ADC, Dual TX DAC with Interpolate by 2, CMOS interface FADCCLK = 65 MSPS fADCIN = 10 MHz FDACCLK = 130 MSPS fDACCUT = 10 MHz |     |          |

|                                         |                                                                                                                                                                                  |                                                                                                                                                                     | MIN                                                                                                                                          | TYP                                                                                                                                  | MAX |          |

| Power dissipation, full duplex mode     | RX and TX active, No input signal applied on ADC and DAC                                                                                                                         | Power<br>(AVDD18_ADC,<br>DVDD18_CLK, DVDD18_DAC,<br>AVDD3_DAC, AVDD3_AUX)                                                                                           |                                                                                                                                              | 326                                                                                                                                  | 391 | mW       |

|                                         |                                                                                                                                                                                  | Digital Power <sup>(1)</sup> (DVDD18)                                                                                                                               |                                                                                                                                              | 72                                                                                                                                   |     | mW       |

|                                         |                                                                                                                                                                                  | Total Power                                                                                                                                                         |                                                                                                                                              | 398                                                                                                                                  |     | mW       |

|                                         | AVDD18_ADC, RX and TX active, No input sign                                                                                                                                      | gnal applied on ADC and DAC                                                                                                                                         |                                                                                                                                              | 77                                                                                                                                   |     |          |

|                                         | DVDD18, RX and TX active, No input signal a                                                                                                                                      | oplied on ADC and DAC                                                                                                                                               |                                                                                                                                              | 40                                                                                                                                   |     |          |

| Supply current, full duplex mode        | DVDD18_CLK, RX and TX active, No input sign                                                                                                                                      | nal applied on ADC and DAC                                                                                                                                          |                                                                                                                                              | 9                                                                                                                                    |     | mA       |

| cupply cultons, run aupiex meac         | DVDD18_DAC, RX and TX active, No input sign                                                                                                                                      | gnal applied on ADC and DAC                                                                                                                                         |                                                                                                                                              | 4                                                                                                                                    |     |          |

|                                         |                                                                                                                                                                                  |                                                                                                                                                                     |                                                                                                                                              |                                                                                                                                      |     |          |

|                                         | AVDD3_DAC, RX and TX active, No input sign                                                                                                                                       | nal applied on ADC and DAC                                                                                                                                          |                                                                                                                                              | 48                                                                                                                                   |     |          |

|                                         | AVDD3_DAC, RX and TX active, No input sign AVDD3_AUX, RX and TX active, No input sign                                                                                            | **                                                                                                                                                                  |                                                                                                                                              | 48<br>7                                                                                                                              |     |          |

| Power dissipation, half duplex RX mode  | AVDD3_AUX, RX and TX active, No input sign RX active, TX in light sleep, TX clock is off,                                                                                        | **                                                                                                                                                                  |                                                                                                                                              |                                                                                                                                      | 211 | mW       |

| Power dissipation, half duplex RX mode  | AVDD3_AUX, RX and TX active, No input sign                                                                                                                                       | pal applied on ADC and DAC Power (AVDD18_ADC, DVDD18_CLK, DVDD18_DAC,                                                                                               |                                                                                                                                              | 7                                                                                                                                    | 211 | mW       |

|                                         | AVDD3_AUX, RX and TX active, No input sign RX active, TX in light sleep, TX clock is off,                                                                                        | Power (AVDD18_ADC, DVDD18_CLK, DVDD18_DAC, AVDD3_DAC, AVDD3_AUX)                                                                                                    |                                                                                                                                              | 7<br>176                                                                                                                             | 211 | mW       |

| mode  Power dissipation, half duplex TX | AVDD3_AUX, RX and TX active, No input sign  RX active, TX in light sleep, TX clock is off, No input signal applied on ADC and DAC  TX active, RX in light sleep, RX clock is on, | Power (AVDD18_ADC, DVDD18_CLK, DVDD18_DAC, AVDD3_DAC, AVDD3_AUX) Digital Power <sup>(1)</sup> (DVDD18)                                                              |                                                                                                                                              | 7<br>176<br>36                                                                                                                       | 211 | mW<br>mW |

| mode                                    | AVDD3_AUX, RX and TX active, No input sign  RX active, TX in light sleep, TX clock is off, No input signal applied on ADC and DAC                                                | pal applied on ADC and DAC  Power (AVDD18_ADC, DVDD18_CLK, DVDD18_DAC, AVDD3_DAC, AVDD3_AUX)  Digital Power  Power (AVDD18_ADC, DVDD18_ADC, DVDD18_ADC, DVDD18_DAC, |                                                                                                                                              | 7<br>176<br>36<br>212                                                                                                                |     |          |

<sup>(1)</sup> These numbers belong to no-load capacitance present on board. The maximum DVDD18 current with CMOS interface depends on the actual load capacitance on the digital output lines.

# 3.5 SUPPLY CHARACTERISTICS (Continued)

AVDD18\_ADC=1.8V, DVDD18\_CLK=1.8V, DVDD18=1.8V, DVDD18\_DAC=1.8V, AVDD3\_DAC=3.0V, AVDD3\_AUX=3.0V, IOUTFS=20mA, typical values at  $T_A = 25^{\circ}$ C, full temperature range is  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, unless otherwise noted.

| PARAMETER                                                      | TEST CONDITIONS                                                             | AFE72                                                                                                                                |     |      |    |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|------|----|--|--|--|

| POWER IN CMOS MODE                                             |                                                                             | Dual RX ADC, Dual TX DAC with Interpolate by 2, CMOS interface FADCCLK = 65 MSPS fADCIN = 10 MHz FDACCLK = 130 MSPS fDACOUT = 10 MHz |     | UNIT |    |  |  |  |

|                                                                |                                                                             | MIN                                                                                                                                  | TYP | MAX  |    |  |  |  |

|                                                                | Global powerdown enabled                                                    |                                                                                                                                      | 12  | 40   |    |  |  |  |

| Power dissipation in Sleep modes                               | Fast recovery powerdown enabled, TX/RX sleeping, clocks on                  |                                                                                                                                      | 140 | 165  | mW |  |  |  |

|                                                                | Fast recovery powerdown enabled, TX/RX sleeping, TX clock off, RX clock on. | n. 120 1                                                                                                                             |     |      |    |  |  |  |

| Power Up and Power Down Time in                                | Different Modes                                                             |                                                                                                                                      |     |      |    |  |  |  |

| OLL I BY "                                                     | Differential input clock                                                    |                                                                                                                                      | 25  |      |    |  |  |  |

| Global powerdown, RX recovery time                             | Single-ended input clock                                                    |                                                                                                                                      | 20  |      | μs |  |  |  |

| Global powerdown in Low power RX                               | Differential input clock                                                    |                                                                                                                                      | 25  |      |    |  |  |  |

| CMOS mode, RX recovery time (ADC running at less than 40 MSPS) | Single-ended input clock                                                    |                                                                                                                                      | 13  |      | μs |  |  |  |

| Clabal navvardavin TV vacavani tima                            | Differential input clock                                                    | 25                                                                                                                                   |     |      |    |  |  |  |

| Global powerdown, TX recovery time                             | Single-ended input clock                                                    | 4                                                                                                                                    |     |      | μs |  |  |  |

| RX recovery time in fast recovery mode                         | RX clock is ON during powerdown                                             |                                                                                                                                      | 5   |      | μs |  |  |  |

| TX recovery time in fast recovery mode                         |                                                                             |                                                                                                                                      | 4   |      | μs |  |  |  |

| RX recovery time from RX powerdown                             | RX clock is on during powerdown                                             |                                                                                                                                      | 5   |      | μs |  |  |  |

| TX recovery time fromTX powerdown                              |                                                                             |                                                                                                                                      | 4   |      | μs |  |  |  |

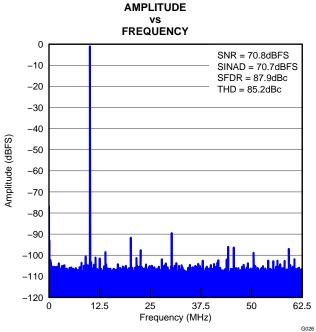

# 3.6 RX ADC ELECTRICAL CHARACTERISTICS

Typical values at  $T_A = 25^{\circ}\text{C}$ , full temperature range is  $T_{\text{MIN}} = -40^{\circ}\text{C}$  to  $T_{\text{MAX}} = 85^{\circ}\text{C}$ , supplies at nominal voltages, 50% clock duty cycle, LVDS output interface, -1dBFS differential input, unless otherwise noted.

|          | DADAMETED                                                             | TEST COMPITIONS                 | Δ     | AFE7222 |     |       | AFE7225 |                   |       |  |

|----------|-----------------------------------------------------------------------|---------------------------------|-------|---------|-----|-------|---------|-------------------|-------|--|

|          | PARAMETER                                                             | TEST CONDITIONS                 | MIN   | TYP     | MAX | MIN   | TYP     | MAX               | UNIT  |  |

| Maxim    | um Clock Rate                                                         |                                 |       |         | 65  |       |         | 125               | MSPS  |  |

| Resolu   | tion                                                                  |                                 |       |         | 12  |       |         | 12                | bits  |  |

| ANALC    | OG INPUTS                                                             |                                 |       |         |     |       |         |                   |       |  |

|          | Differential input range                                              |                                 |       | 2       |     |       | 2       |                   | Vpp   |  |

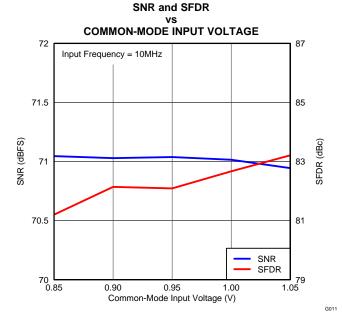

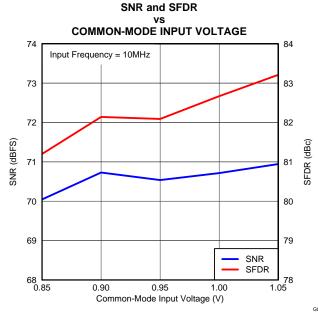

| $V_{CM}$ | Common mode output voltage                                            |                                 |       | 0.95    |     |       | 0.95    |                   | V     |  |

|          | Input resistance (DC)                                                 | Differential                    |       | >1      |     |       | >1      |                   | МΩ    |  |

|          | Input capacitance                                                     | Differential                    |       | 4       |     |       | 4       |                   | pF    |  |

|          | Analog input bandwidth                                                |                                 |       | 550     |     |       | 550     |                   | MHz   |  |

| CMRR     | Common mode rejection ratio                                           | Fin = 10MHz                     |       | 40      |     |       | 40      |                   | dB    |  |

| DYNAN    | MIC ACCURACY                                                          |                                 |       |         |     |       |         |                   |       |  |

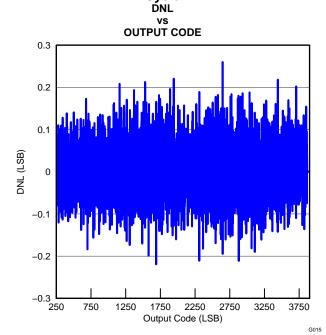

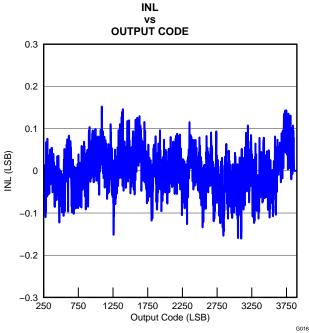

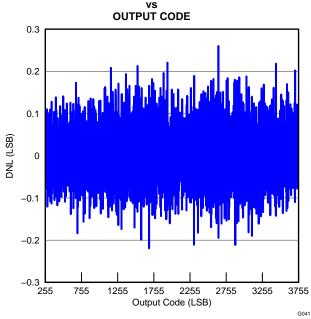

| DNL      | Differential linearity error                                          | No Missing Codes,<br>Fin =10MHz | -0.95 | ±0.5    | 1.4 | -0.95 | ±0.5    | 1.4               | LSB   |  |

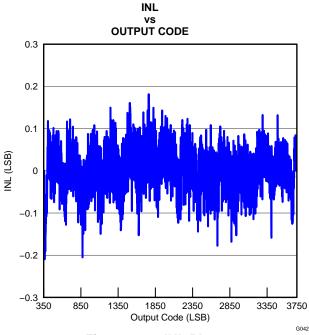

| INL      | Integral linearity error                                              | Fin = 10MHz                     | -1.7  | ±0.2    | 1.7 | -1.7  | ±0.2    | 1.7               | LSB   |  |

|          | Offset error                                                          |                                 | -15   | 2       | 15  | -15   | 3       | 15                | mV    |  |

|          | Offset temperature co-efficient                                       |                                 |       | >0.005  |     |       | >0.005  |                   | mV/°C |  |

|          | Gain error as a result of internal reference inaccuracy alone – EGREF |                                 | -2.5  |         | 2.5 | -2.5  |         | 2.5               | %FS   |  |

|          | Gain error of channel alone – EGCHAN                                  |                                 |       | ±1      |     |       | ±1      |                   | %FS   |  |

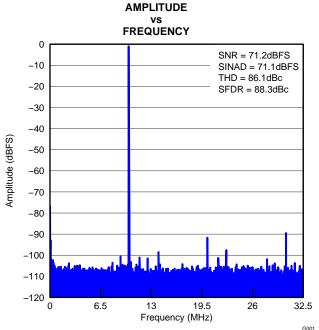

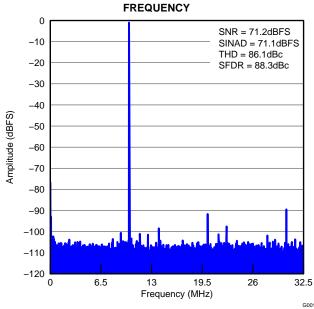

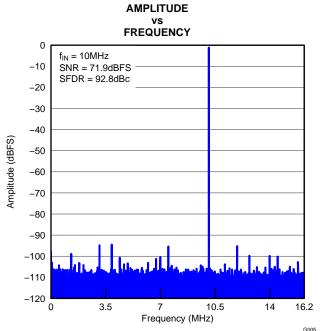

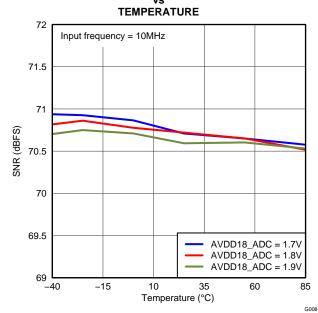

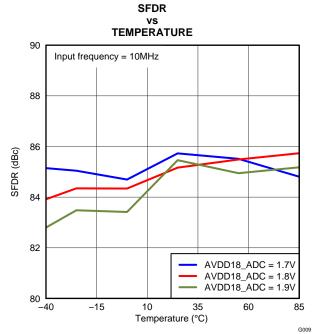

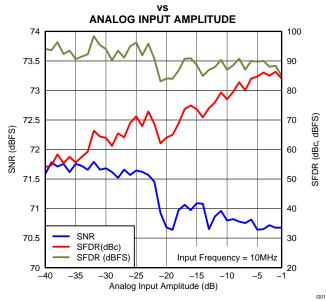

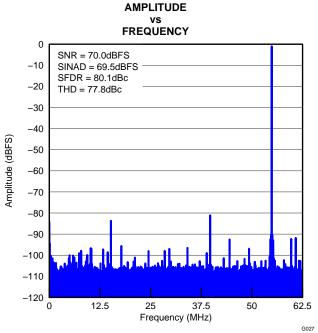

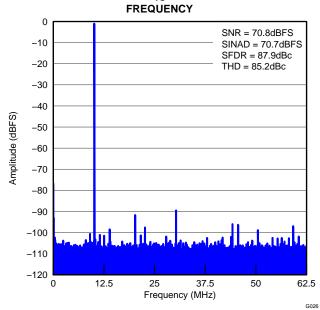

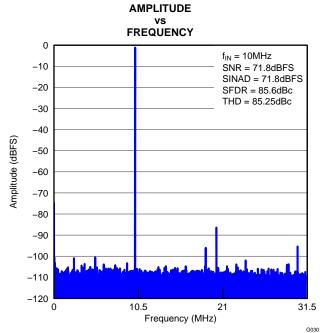

| DYNAN    | MIC AC CHARACTERISTICS                                                |                                 |       |         |     |       |         |                   |       |  |

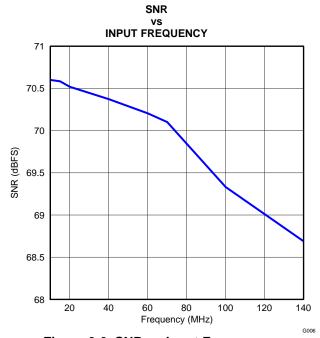

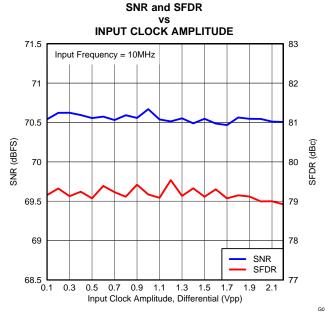

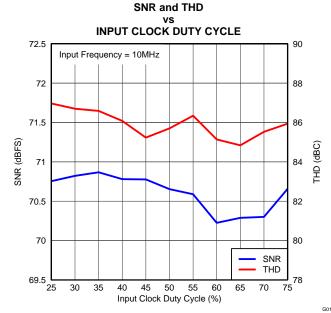

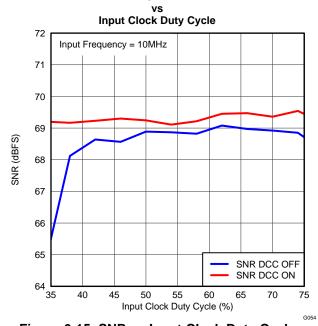

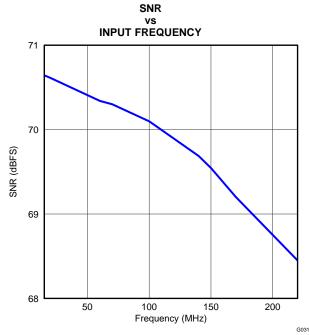

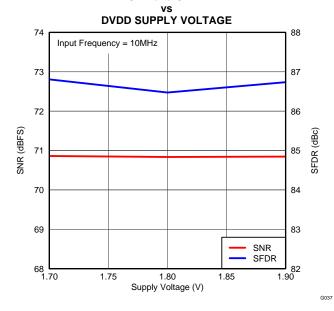

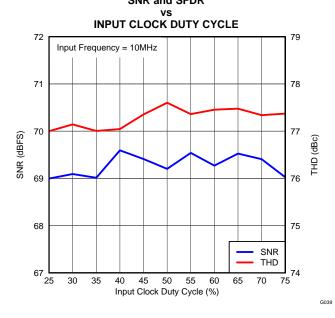

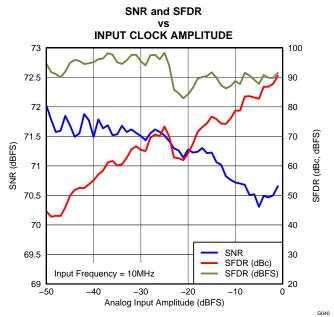

|          |                                                                       | Fin = 10MHz                     | 67.5  | 70.5    |     | 67    | 70.7    |                   | dBFS  |  |

| SNR      | Signal-to-noise ratio (1)                                             | Fin = 70MHz                     |       | 70      |     |       | 70.1    |                   | dBFS  |  |

|          |                                                                       | Fin = 140MHz                    |       | 68.7    |     |       | 69.5    | 1.4<br>1.7<br>1.5 | dBFS  |  |

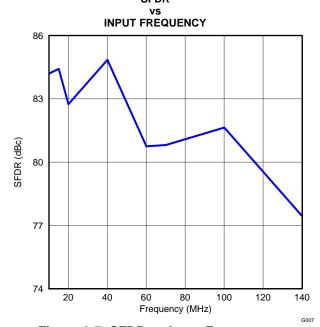

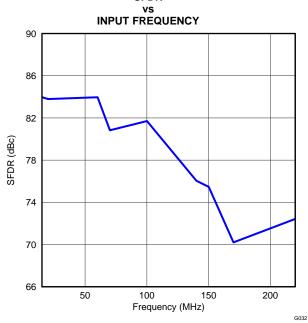

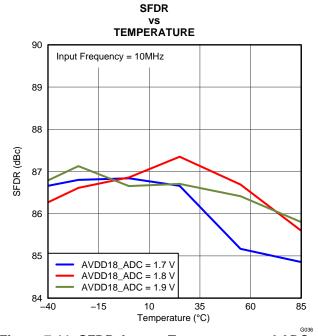

|          |                                                                       | Fin = 10MHz                     | 73    | 85      |     | 73    | 84      |                   | dBc   |  |

| SFDR     | Spurious free dynamic range <sup>(1)</sup>                            | Fin = 70MHz                     |       | 81      |     |       | 79      |                   | dBc   |  |

|          |                                                                       | Fin = 140MHz                    |       | 77      |     |       | 76      | 1.4<br>1.7<br>1.5 | dBc   |  |

<sup>(1)</sup> Up to 65MSPS typical SNR and SFDR performance in CMOS interface is same as with LVDS interface.

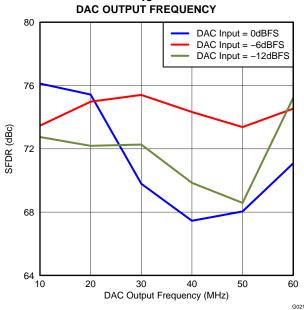

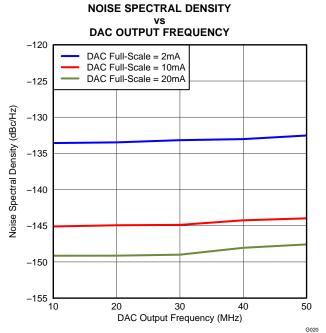

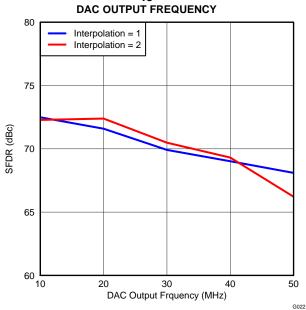

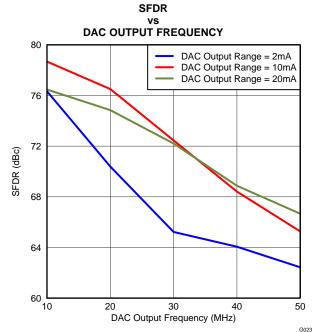

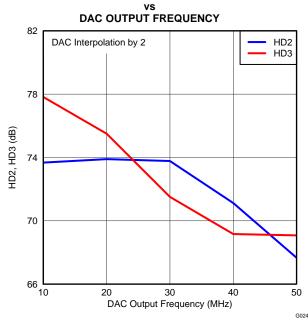

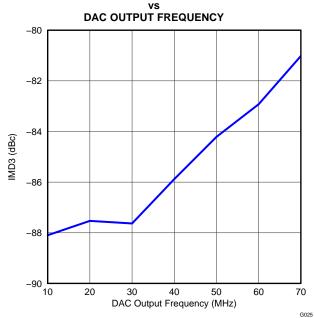

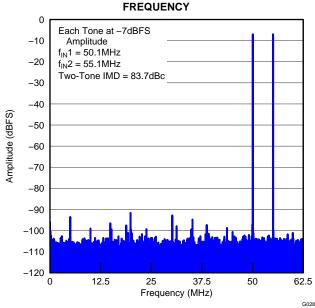

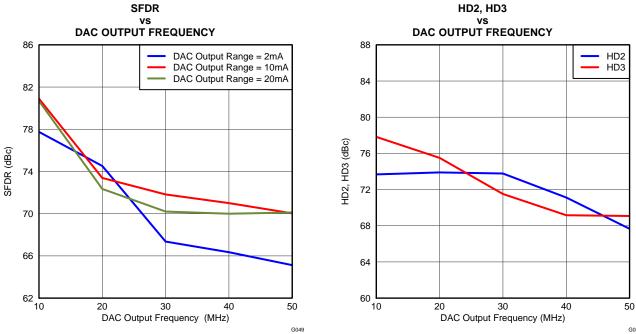

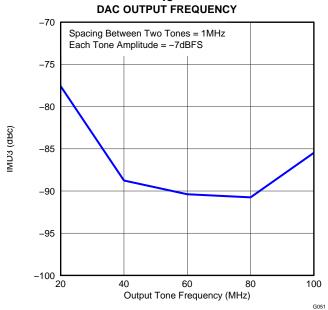

# 3.7 TX DAC ELECTRICAL CHARACTERISTICS

Typical values at  $T_A = 25^{\circ}\text{C}$ , full temperature range is  $T_{\text{MIN}} = -40^{\circ}\text{C}$  to  $T_{\text{MAX}} = 85^{\circ}\text{C}$ , 50% clock duty cycle, supplies at nominal voltages,  $I_{\text{OUTFS}} = 20$  mA, DAC output common mode voltage is AVDD3=3.0V, unless otherwise noted.

|        | PARAMETER                          | TEST CONDITIONS                                    | AF             | E7222 |               | AF             | E7225 |               | UNIT               |

|--------|------------------------------------|----------------------------------------------------|----------------|-------|---------------|----------------|-------|---------------|--------------------|

|        | PARAMETER                          | TEST CONDITIONS                                    | MIN            | TYP   | MAX           | MIN            | TYP   | MAX           | UNII               |

| Maximu | um clock output rate               |                                                    |                |       | 130           |                |       | 250           | MSPS               |

| Resolu | tion                               |                                                    |                |       | 12            |                |       | 12            | Bits               |

| ANALC  | OG OUTPUTS                         |                                                    |                |       |               |                |       |               |                    |

|        | Full scale output current, per DAC |                                                    | 2              |       | 20            | 2              |       | 20            | mA                 |

|        | Output voltage compliance range    | I <sub>OUTFS</sub> = 20 mA,<br>Current sink output | AVDD3_DAC -0.5 |       | AVDD3_DAC+0.5 | AVDD3_DAC -0.5 |       | AVDD3_DAC+0.5 | V                  |

|        | Output resistance                  |                                                    |                | 300   |               |                | 300   |               | kΩ                 |

|        | Output capacitance                 |                                                    |                | 5     |               |                | 5     |               | pF                 |

|        | Offset error                       | Mid code offset                                    |                | ±0.03 |               |                | ±0.03 |               | %FS <sup>(1)</sup> |

|        | Gain error                         | Internal reference                                 |                | ±1    |               |                | ±1    |               | %FS <sup>(1)</sup> |

|        | Gain mismatch                      | Internal reference dual DAC                        |                | ±0.5  |               |                | ±0.5  |               | %FS <sup>(1)</sup> |

| DC PEF | RFORMANCE                          |                                                    |                |       |               |                |       |               |                    |

| INL    | Integral non-linearity             | Fout = 10 MHz                                      | -2             | ±1    | 2             | -2             | ±1    | 2             | LSB                |

| DNL    | Differential non-linearity         | Fout = 10 MHz                                      |                | ±0.5  |               |                | ±0.5  |               | LSB                |

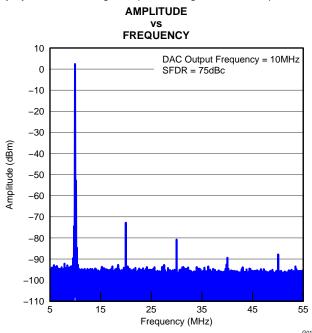

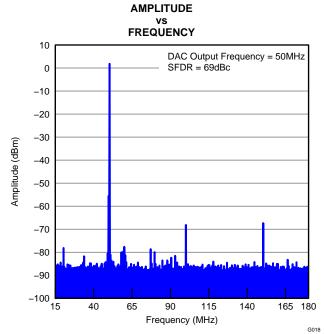

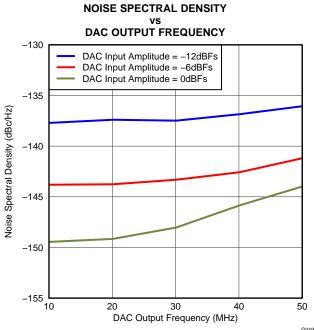

| AC PE  | RFORMANCE                          |                                                    |                |       |               |                |       |               |                    |

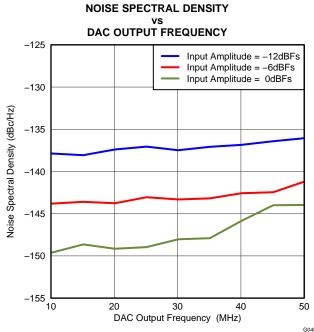

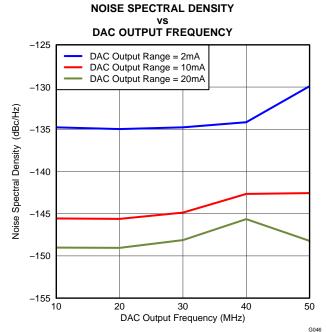

|        | Noise spectral density             | Fout = 10 MHz, 0 dBFS                              | 145.5          | 149   |               | 148.5          | 151   |               | dBc/Hz             |

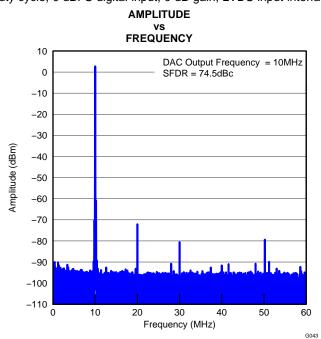

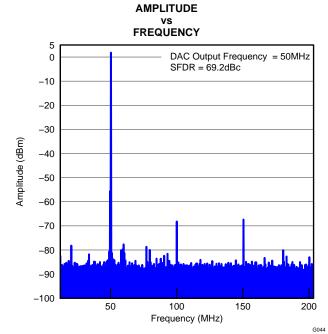

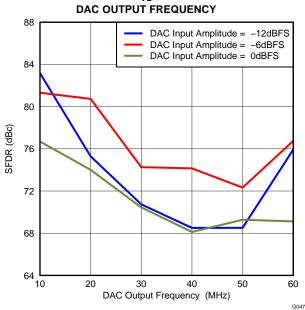

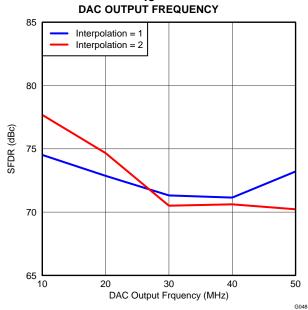

| CEDD   | Couries of the advances are no     | Fout = 10 MHz, 0 dBFS                              | 70             | 76    |               | 70             | 76    |               | dBc                |

| SFDR   | Spurious free dynamic range        | Fout = 20 MHz, 0 dBFS                              |                | 75    |               |                | 74    |               | dBc                |

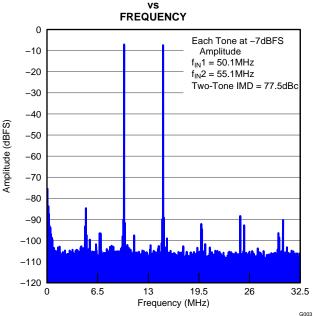

| IMD    | Inter-modulation distortion        | Fout = 5.1/6.1 MHz,<br>-7 dBFS each                |                | 73    |               |                | 73    |               | dBc                |

| ACLR   | Adjacent channel leakage ratio     | DAC clock = 122.88 MSPS,<br>Fout = 30.72 MHz       |                | 75    |               |                |       |               | dB                 |

| ACLR   | Aujacent Chamber leakage (allo     | DAC clock = 245.76 MSPS,<br>Fout = 61.44 MHz       |                |       |               |                | 73    |               | uБ                 |

<sup>(1) %</sup>FS = % Differential Full Scale

# 3.8 AUXILIARY ADC ELECTRICAL CHARACTERISTICS

Typical values at  $T_A = 25^{\circ}$ C, full temperature range is  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, supplies at nominal voltages, unless otherwise noted.

|         | PARAMETER                      | TEST CONDITIONS                   | AFE722 | 2 / AF | E7225 | UNIT |

|---------|--------------------------------|-----------------------------------|--------|--------|-------|------|

|         |                                |                                   | MIN    | TYP    | MAX   | UNII |

| Maximu  | ım Clock Rate                  |                                   |        |        | 100   | kSPS |

| Resolut | tion                           |                                   |        |        | 12    | Bits |

| ANALO   | G INPUTS                       |                                   |        |        |       |      |

|         | Input voltage range            |                                   |        | 1.5    |       | V    |

|         | Input capacitance              |                                   |        | 4      |       | pF   |

|         | Maximum input signal frequency |                                   |        | 10     |       | kHz  |

| DC PER  | RFORMANCE                      |                                   |        |        |       |      |

| INL     | Integral non-linearity         | Static conditions (near DC input) | -4.5   | ±2     | 4.5   | LSB  |

# 3.9 AUXILIARY DAC ELECTRICAL CHARACTERISTICS

Typical values at  $T_A = 25$ °C, full temperature range is  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, supplies at nominal voltages,  $I_{OUTFS} = 5$ mA, 300  $\Omega$  termination, unless otherwise noted.

|         | PARAMETER                       | TEST CONDITIONS                                                             | AFE72 | UNIT |                     |      |

|---------|---------------------------------|-----------------------------------------------------------------------------|-------|------|---------------------|------|

|         | PARAMETER                       | TEST CONDITIONS                                                             | MIN   | TYP  | MAX                 | UNII |

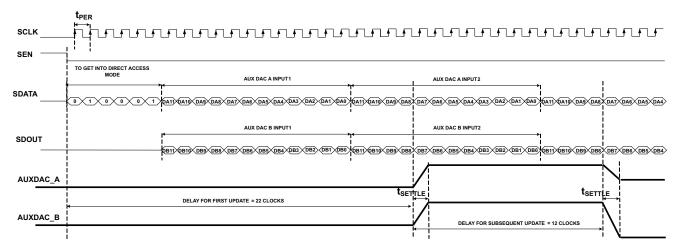

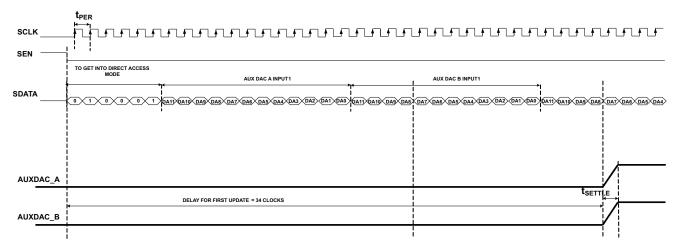

| Maximu  | ım Clock Rate                   | Continuous refresh of AUX DAC Channel A from SDATA and Channel B from SDOUT |       |      | 3.33 <sup>(1)</sup> | MSPS |

| Resolut | tion                            |                                                                             |       | 12   | Bits                |      |

| ANALO   | G OUTPUTS                       |                                                                             |       |      |                     |      |

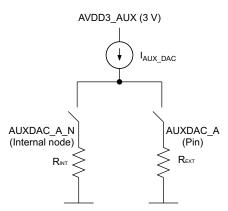

|         | Output current, per auxDAC      |                                                                             | 2.5   |      | 7.5                 | mA   |

|         | Output voltage compliance range |                                                                             |       | 1.5  |                     | V    |

| DYNAM   | IIC PERFORMANCE                 |                                                                             |       |      |                     |      |

| INL     | Integral non-linearity          | Static conditions (near DC input)                                           | -1.7  | ±0.5 | 1.7                 | LSB  |

| DNL     | Differential non-linearity      | Static conditions (near DC input)                                           |       | ±0.3 |                     | LSB  |

<sup>(1) 12</sup> bits x (1/SCLK) in direct access mode, SCLK max limit is 40MHz

# 3.10 DIGITAL CHARACTERISTICS

The DC specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level 0 or 1.  $AVDD18^*$ ,  $DVDD18^* = 1.8V$ ,  $AVDD3^* = 3.0V$

|                  | PARAMETER                              | TEST CONDITIONS                                       | MIN          | TYP    | MAX  | UNIT |

|------------------|----------------------------------------|-------------------------------------------------------|--------------|--------|------|------|

| DIGITA           | AL INPUTS – RESET, SCLK, SDATA, SE     | EN, PDN                                               |              |        |      |      |

|                  | High-level input voltage               | All these pins support 1.8V and 3V CMOS logic levels. | 1.3          |        |      | ٧    |

|                  | Low-level input voltage                |                                                       |              |        | 0.4  | V    |

| DAC E            | DIGITAL INPUTS IN CMOS INTERFACE       | MODE                                                  |              |        |      |      |

|                  | High-level input voltage               | 1.8V CMOS logic levels only                           | 1.3          |        |      | V    |

|                  | Low-level input voltage                |                                                       |              |        | 0.4  | V    |

| DAC E            | DIGITAL INPUTS IN LVDS INTERFACE I     | MODE                                                  | •            |        |      |      |

| V <sub>IDH</sub> | High-level differential input voltage  | Standard swing LVDS with external 100ohms termination |              | 350    |      | mV   |

| V <sub>IDL</sub> | Low-level differential input voltage   | Standard swing LVDS with external 100ohms termination |              | -350   |      | mV   |

| V <sub>ICM</sub> | Input common-mode voltage              |                                                       |              | 1.2    |      | V    |

| DIGITA           | AL OUTPUTS – CMOS INTERFACE – SI       | DOUT, ADC OUTPUTS (IN CMOS INTERFACE                  | MODE)        |        |      |      |

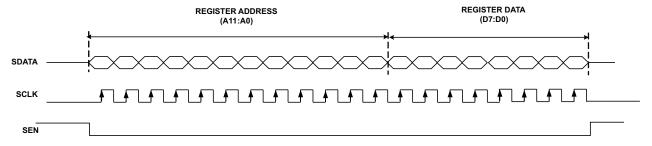

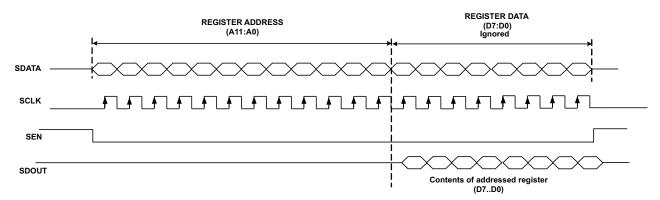

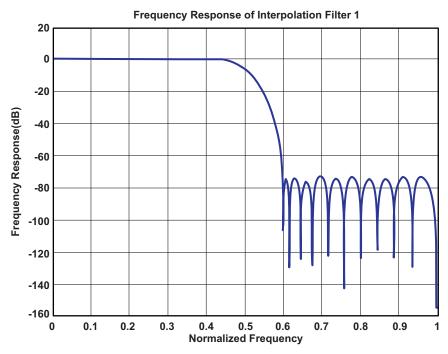

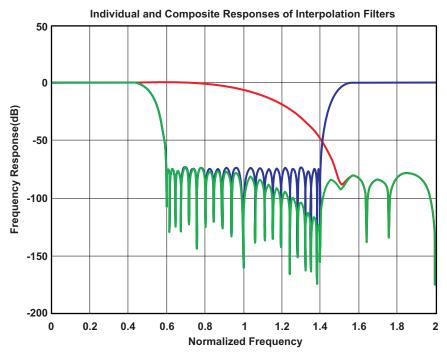

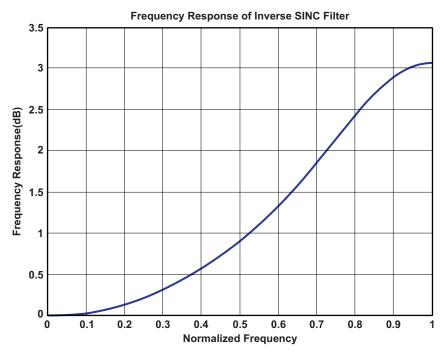

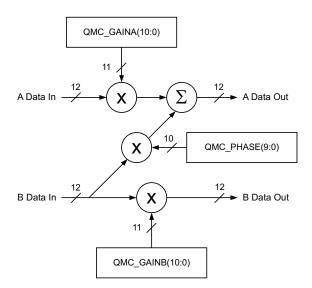

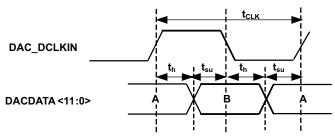

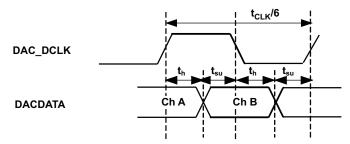

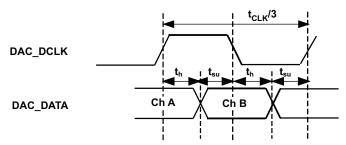

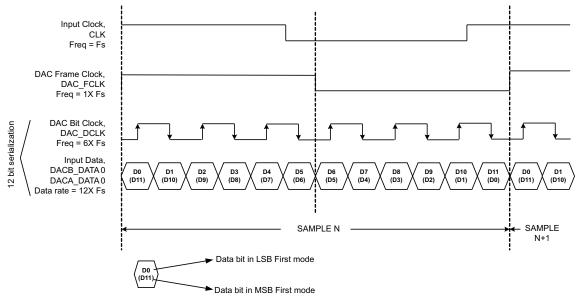

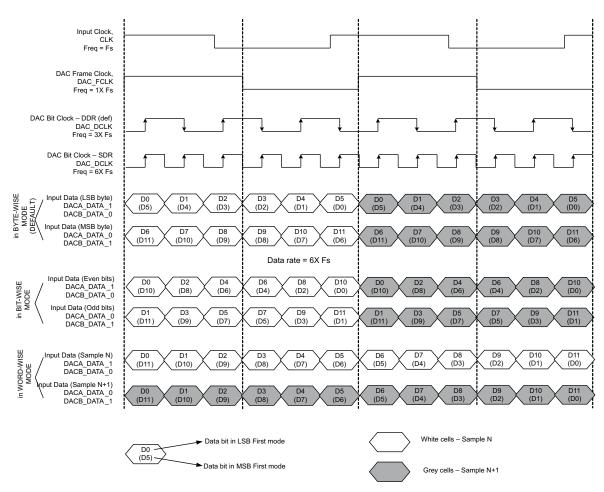

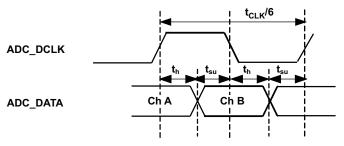

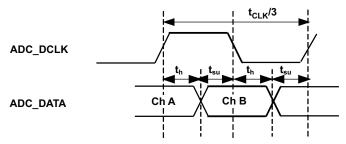

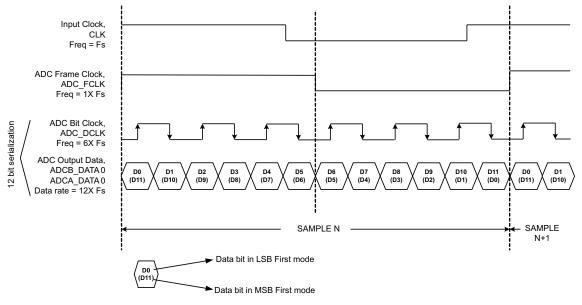

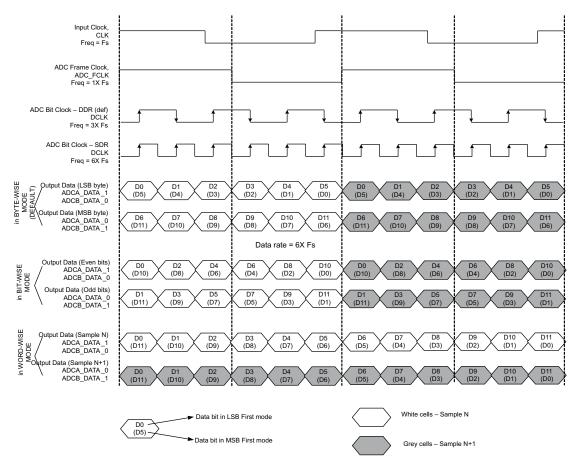

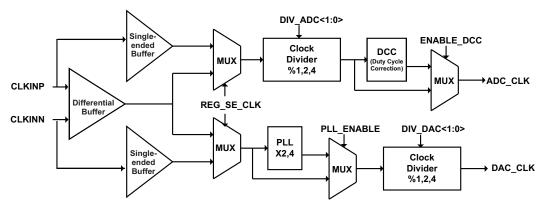

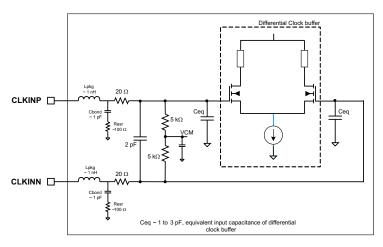

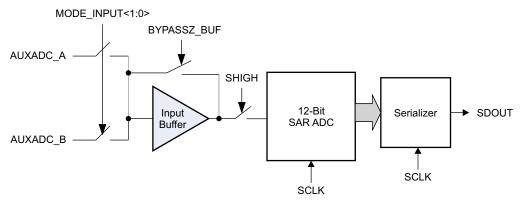

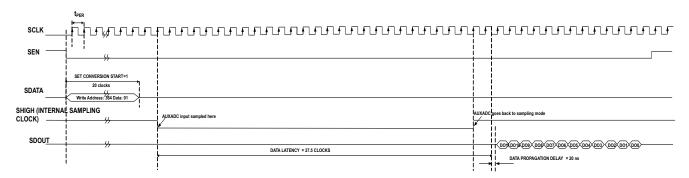

|                  | High-level output voltage              |                                                       | DVDD18 - 0.1 | DVDD18 |      | V    |