# life.augmented

## STIPN1M50T-H

## SLLIMM<sup>™</sup>-nano small low-loss intelligent molded module IPM, 3-phase inverter, 1 A, 3.6 Ω max., 500 V MOSFET

Datasheet - production data

#### **Features**

- IPM 1 A, 500 V, R<sub>DS(on)</sub>= 3.6 Ω, 3-phase MOSFET inverter bridge including control ICs for gate driving

- Optimized for low electromagnetic interference

- 3.3 V, 5 V, 15 V CMOS/TTL input comparators with hysteresis and pulldown/pull-up resistors

- Undervoltage lockout

- Internal bootstrap diode

- Interlocking function

- Smart shutdown function

- Comparator for fault protection against overtemperature and overcurrent

- Op-amp for advanced current sensing

- Optimized pinout for easy board layout

- NTC for temperature control (UL 1434 CA 2 and 4)

- Up to ±2 kV ESD protection (HBM C = 100 pF, R = 1.5 kΩ)

## **Applications**

- 3-phase inverters for small power motor drives

- Dish washers, refrigerator compressors, heating systems, air-conditioning fans, draining and recirculation pumps

## **Description**

This SLLIMM (small low-loss intelligent molded module) nano provides a compact, high performance AC motor drive in a simple, rugged design. It is composed of six MOSFETs and three half-bridge HVICs for gate driving, providing low electromagnetic interference (EMI) characteristics with optimized switching speed. The package is optimized for thermal performance and compactness in built-in motor applications, or other low power applications where assembly space is limited. This IPM includes an operational amplifier, completely uncommitted, and a comparator that can be used to design a fast and efficient protection circuit. SLLIMM™ is a trademark of STMicroelectronics.

**Table 1: Device summary**

| Order code   | Marking    | Package  | Packing |

|--------------|------------|----------|---------|

| STIPN1M50T-H | IPN1M50T-H | NDIP-26L | Tube    |

June 2017 DocID028911 Rev 5 1/25

Contents STIPN1M50T-H

## Contents

| 1 | Internal | schematic diagram and pin configuration | 3  |

|---|----------|-----------------------------------------|----|

| 2 | Electric | al ratings                              | 6  |

|   | 2.1      | Absolute maximum ratings                | 6  |

|   | 2.2      | Thermal data                            | 6  |

| 3 | Electric | al characteristics                      | 7  |

|   | 3.1      | Inverter part                           | 7  |

|   | 3.2      | Control part                            | 9  |

|   |          | 3.2.1 NTC thermistor                    |    |

|   | 3.3      | Waveform definitions                    | 14 |

| 4 | Smart s  | shutdown function                       | 15 |

| 5 | Applica  | tion circuit example                    | 17 |

|   | 5.1      | Guidelines                              | 18 |

| 6 | Packag   | e information                           | 20 |

|   | 6.1      | NDIP-26L package information            | 21 |

|   | 6.2      | NDIP-26L packing information            | 23 |

| 7 | Revisio  | n history                               | 24 |

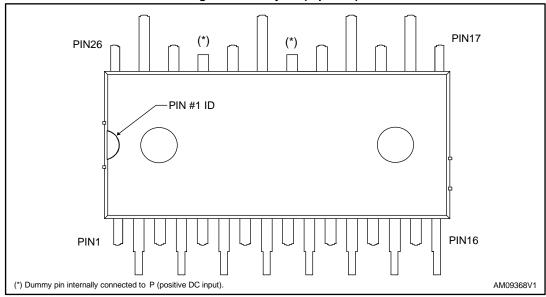

## 1 Internal schematic diagram and pin configuration

GND(1)( (26)NW NTC T/SD/OD(2) )(25)W,OUTW GND VccW(3) HVG )(24)VbootW OUT vcc HinW(4) HIN LVG SD/OD LinW(5) OP+(6) )(23)NV OPOUT(7)( GND OPOUT )(22)V,OUTV OP-HVG OP-(8) OUT VCC VccV(9) HIN LVG SD/OD Vboot HinV(10) )(21)VbootV LinV(11) )(20)NU GND Cin(12) HVG VccU(13) )(19)U,OUTU OUT vcc HIN LVG HinU(14) SD/OD )(18)P LIN Vboot T/SD/OD(15) LinU(16) )(17)VbootU GIPD120120170806S A

Figure 1: Internal schematic diagram

Table 2: Pin description

| Pin | Symbol                 | Description                                                                                  |

|-----|------------------------|----------------------------------------------------------------------------------------------|

| 1   | GND                    | Ground                                                                                       |

| 2   | T/SD/OD                | NTC thermistor terminal / shutdown logic input (active low) / open-drain (comparator output) |

| 3   | Vcc W                  | Low voltage power supply W phase                                                             |

| 4   | HIN W                  | High-side logic input for W phase                                                            |

| 5   | LIN W                  | Low-side logic input for W phase                                                             |

| 6   | OP+                    | Op-amp non inverting input                                                                   |

| 7   | OPout                  | Op-amp output                                                                                |

| 8   | OP-                    | Op-amp inverting input                                                                       |

| 9   | Vcc V                  | Low voltage power supply V phase                                                             |

| 10  | HIN V                  | High-side logic input for V phase                                                            |

| 11  | LIN V                  | Low-side logic input for V phase                                                             |

| 12  | CIN                    | Comparator input                                                                             |

| 13  | Vcc U                  | Low voltage power supply for U phase                                                         |

| 14  | HIN U                  | High-side logic input for U phase                                                            |

| 15  | T/SD/OD                | NTC thermistor terminal / shutdown logic input (active low) / open-drain (comparator output) |

| 16  | LIN U                  | Low-side logic input for U phase                                                             |

| 17  | V <sub>BOOT</sub> U    | Bootstrap voltage for U phase                                                                |

| 18  | Р                      | Positive DC input                                                                            |

| 19  | U, OUT∪                | U phase output                                                                               |

| 20  | Nυ                     | Negative DC input for U phase                                                                |

| 21  | V <sub>BOOT</sub> V    | Bootstrap voltage for V phase                                                                |

| 22  | V, OUT∨                | V phase output                                                                               |

| 23  | N <sub>V</sub>         | Negative DC input for V phase                                                                |

| 24  | V <sub>BOOT</sub> W    | Bootstrap voltage for W phase                                                                |

| 25  | W,<br>OUT <sub>W</sub> | W phase output                                                                               |

| 26  | Nw                     | Negative DC input for W phase                                                                |

Figure 2: Pin layout (top view)

Electrical ratings STIPN1M50T-H

## 2 Electrical ratings

## 2.1 Absolute maximum ratings

Table 3: Inverter part

| Symbol                           | Parameter                                                                               | Value | Unit |

|----------------------------------|-----------------------------------------------------------------------------------------|-------|------|

| V <sub>DSS</sub>                 | MOSFET blocking voltage (or drain-source voltage) for each MOSFET ( $V_{IN}^{(f)}$ = 0) | 500   | ٧    |

| ± I <sub>D</sub>                 | Continuous current each MOSFET                                                          | 1     | Α    |

| ± I <sub>DP</sub> <sup>(2)</sup> | Peak drain current each MOSFET (less than 1 ms)                                         | 2     | Α    |

| P <sub>TOT</sub>                 | Each MOSFET total dissipation at T <sub>C</sub> = 25 °C                                 | 9.6   | W    |

#### Notes:

**Table 4: Control part**

| Symbol                     | Parameter                                           | Min.                   | Max.                    | Unit |

|----------------------------|-----------------------------------------------------|------------------------|-------------------------|------|

| Vouт                       | Output voltage applied among OUT∪, OUT∨, OUTw - GND | V <sub>boot</sub> - 21 | V <sub>boot</sub> + 0.3 | V    |

| Vcc                        | Low voltage power supply                            | - 0.3                  | 21                      | V    |

| V <sub>CIN</sub>           | Comparator input voltage                            | - 0.3                  | Vcc + 0.3               | V    |

| $V_{op+}$                  | Op-amp non-inverting input                          | - 0.3                  | $V_{CC} + 0.3$          | V    |

| V <sub>op</sub> -          | Op-amp inverting input                              | - 0.3                  | Vcc + 0.3               | V    |

| V <sub>boot</sub>          | Bootstrap voltage                                   | - 0.3                  | 620                     | V    |

| $V_{IN}$                   | Logic input voltage applied among HIN, LIN and GND  | - 0.3                  | 15                      | V    |

| $V_{T/\overline{SD}/OD}$   | Open-drain voltage                                  | - 0.3                  | 15                      | V    |

| $\Delta V_{\text{OUT/dT}}$ | Allowed output slew rate                            |                        | 50                      | V/ns |

Table 5: Total system

| Symbol           | Parameter                                                                                      | Value      | Unit     |

|------------------|------------------------------------------------------------------------------------------------|------------|----------|

| V <sub>ISO</sub> | Isolation withstand voltage applied between each pin and heatsink plate (AC voltage, t = 60 s) | 1000       | <b>V</b> |

| Tj               | Power chip operating junction temperature range                                                | -40 to 150 | °C       |

| Tc               | Module case operation temperature range                                                        | -40 to 125 | °C       |

## 2.2 Thermal data

Table 6: Thermal data

| Symbol               | Parameter                        | Value | Unit |

|----------------------|----------------------------------|-------|------|

| R <sub>th(j-c)</sub> | Thermal resistance junction-case | 13    | °C/W |

$<sup>^{(1)}</sup>$ Applied among HINi, LINi and GND for i = U, V, W.

<sup>&</sup>lt;sup>(2)</sup>Pulse width limited by max. junction temperature.

## 3 Electrical characteristics

$T_J = 25$  °C unless otherwise specified.

## 3.1 Inverter part

Table 7: Static

| Symbol               | Parameter                              | Test conditions                                                                              | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|------|

| IDSS                 | Zero-gate voltage drain current        | V <sub>DS</sub> = 500 V, V <sub>CC</sub> = 15 V;<br>V <sub>Boot</sub> = 15 V                 |      |      | 1    | mA   |

| V <sub>(BR)DSS</sub> | Drain-source breakdown voltage         | $V_{CC} = V_{boot} = 15 \text{ V},$<br>$V_{IN}^{(1)} = 0 \text{ V}, I_D = 1 \text{ mA}$      | 500  |      |      | V    |

| R <sub>DS(on)</sub>  | Static drain source turn-on resistance | $V_{CC} = V_{boot} = 15 \text{ V},$<br>$V_{IN}^{(1)} = 0 - 5 \text{ V}, I_D = 0.5 \text{ A}$ |      | 3.2  | 3.6  | Ω    |

| V <sub>SD</sub>      | Drain-source diode forward voltage     | $V_{IN}^{(1)} = 0$ "logic state",<br>$I_D = 1 \text{ A}$                                     |      | 0.9  | 1.6  | V    |

#### Notes:

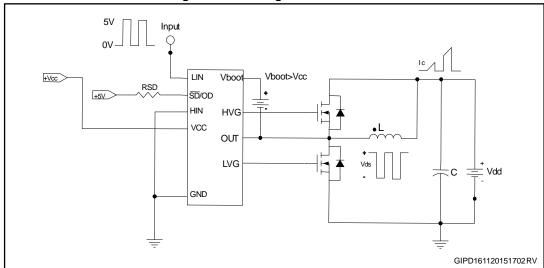

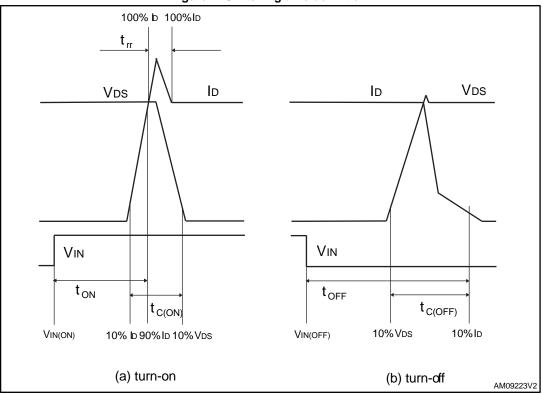

Table 8: Inductive load switching time and energy

| Symbol                             | Parameter                 | Test conditions                                           | Min. | Тур. | Max. | Unit |

|------------------------------------|---------------------------|-----------------------------------------------------------|------|------|------|------|

| ton <sup>(1)</sup>                 | Turn-on time              |                                                           | ı    | 226  | -    |      |

| $t_{c(on)}^{(1)}$                  | Crossover time (on)       | $V_{DD} = 300 \text{ V},$                                 | -    | 130  | -    |      |

| t <sub>off</sub> (1)               | Turn-off time             | $V_{CC} = V_{boot} = 15 \text{ V},$                       | -    | 248  | -    | ns   |

| t <sub>c(off)</sub> <sup>(1)</sup> | Crossover time (off)      | $V_{IN}^{(2)} = 0 - 5 V,$                                 | -    | 56   | -    |      |

| t <sub>rr</sub>                    | Reverse recovery time     | Ic = 0.5 A<br>(see Figure 4: "Switching time definition") | -    | 155  | -    |      |

| Eon                                | Turn-on switching energy  |                                                           | ı    | 25   | -    | 1    |

| E <sub>off</sub>                   | Turn-off switching energy |                                                           | -    | 3.8  | -    | μJ   |

#### Notes:

$<sup>^{(1)}</sup>$ Applied among HINx, LINx and GND for x=U,V,W.

$<sup>^{(1)}</sup>$ toN and toFF include the propagation delay time of the internal drive.  $t_{C(ON)}$  and  $t_{C(OFF)}$  are the switching time of MOSFET itself under the internally given gate driving conditions.

$<sup>^{(2)}</sup>$ Applied among HINx, LINx and GND for x=U,V,W.

Figure 3: Switching time test circuit

Figure 4: Switching time definition

Figure 4: "Switching time definition" refers to HIN, LIN inputs (active high).

## 3.2 Control part

Table 9: Low voltage power supply (Vcc = 15 V unless otherwise specified)

| Symbol                | Parameter                                   | Test conditions                                                                                                                  | Min. | Тур. | Max. | Unit |

|-----------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Vcc_hys               | Vcc UV hysteresis                           |                                                                                                                                  | 1.2  | 1.5  | 1.8  | V    |

| V <sub>CC_thON</sub>  | V <sub>CC</sub> UV turn ON threshold        |                                                                                                                                  | 11.5 | 12   | 12.5 | V    |

| V <sub>CC_thOFF</sub> | Vcc UV turn OFF threshold                   |                                                                                                                                  | 10   | 10.5 | 11   | V    |

| I <sub>qccu</sub>     | Undervoltage quiescent supply current       | $V_{CC} = 10 \text{ V},$<br>$T/\overline{SD}/OD = 5 \text{ V}; \text{ LIN} = 0 \text{ V};$<br>$H_{IN} = 0, C_{IN} = 0 \text{ V}$ |      |      | 150  | μΑ   |

| Iqcc                  | Quiescent current                           | $V_{cc} = 15 \text{ V},$<br>$T/\overline{SD}/OD = 5 \text{ V}; \text{LIN} = 0 \text{ V};$<br>$H_{IN} = 0, C_{IN} = 0 \text{ V}$  |      |      | 1    | mA   |

| V <sub>ref</sub>      | Internal comparator (CIN) reference voltage |                                                                                                                                  | 0.5  | 0.54 | 0.58 | V    |

Table 10: Bootstrapped voltage (V<sub>CC</sub> = 15 V unless otherwise specified)

| Symbol                | Parameter                                      | Test conditions                                                                                                                 | Min. | Тур. | Max. | Unit |

|-----------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>BS_hys</sub>   | V <sub>BS</sub> UV hysteresis                  |                                                                                                                                 | 1.2  | 1.5  | 1.8  | V    |

| V <sub>BS_thON</sub>  | V <sub>BS</sub> UV turn-ON<br>threshold        |                                                                                                                                 | 11.1 | 11.5 | 12.1 | V    |

| V <sub>BS_thOFF</sub> | V <sub>BS</sub> UV turn-OFF<br>threshold       |                                                                                                                                 | 9.8  | 10   | 10.6 | V    |

| I <sub>QBSU</sub>     | Undervoltage V <sub>BS</sub> quiescent current | $V_{BS} < 9 \text{ V}$<br>$T/\overline{SD}/OD = 5 \text{ V}; \text{LIN} = 0 \text{ V}$<br>and HIN = 5 V; $C_{IN} = 0 \text{ V}$ |      | 70   | 110  | μΑ   |

| IQBS                  | V <sub>BS</sub> quiescent current              | $V_{BS} = 15 \text{ V T/$\overline{SD}$/OD} = 5 \text{ V};$<br>LIN = 0 V and HIN = 5 V;<br>$C_{IN} = 0 \text{ V}$               |      | 200  | 300  | μΑ   |

| R <sub>DS(on)</sub>   | Bootstrap driver on- resistance                | LVG ON                                                                                                                          |      | 120  |      | Ω    |

Table 11: Logic inputs (Vcc = 15 V unless otherwise specified)

| Table 11. Logic inputs (VCC = 13 V unless otherwise specified) |                                     |                                                                 |      |      |      |      |  |

|----------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------|------|------|------|------|--|

| Symbol                                                         | Parameter                           | Test conditions                                                 | Min. | Тур. | Max. | Unit |  |

| Vil                                                            | Low logic level voltage             |                                                                 |      |      | 0.8  | V    |  |

| V <sub>ih</sub>                                                | High logic level voltage            |                                                                 | 2.25 |      |      | V    |  |

| IHINh                                                          | HIN logic "1" input bias current    | HIN = 15 V                                                      | 20   | 40   | 100  | μΑ   |  |

| I <sub>HINI</sub>                                              | HIN logic "0" input bias current    | HIN = 0 V                                                       |      |      | 1    | μΑ   |  |

| ILINh                                                          | LIN logic "1" input<br>bias current | LIN = 15 V                                                      | 20   | 40   | 100  | μΑ   |  |

| I <sub>LINI</sub>                                              | LIN logic "0" input<br>bias current | LIN = 0 V                                                       |      |      | 1    | μΑ   |  |

| I <sub>SDh</sub>                                               | SD logic "0" input bias current     | <u>SD</u> = 15 V                                                | 220  | 295  | 370  | μΑ   |  |

| Isdi                                                           | SD logic "1" input bias current     | $\overline{SD} = 0 \text{ V}$                                   |      |      | 3    | μΑ   |  |

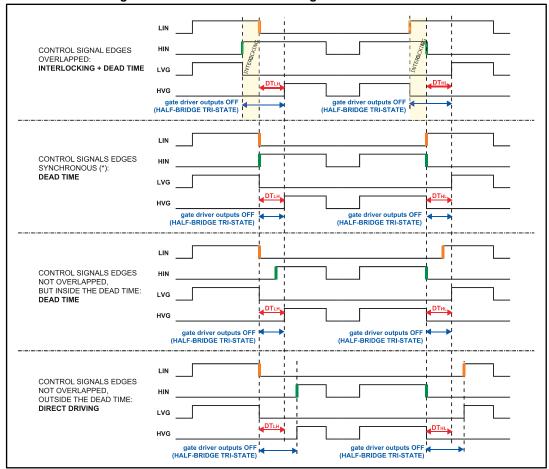

| Dt                                                             | Dead time                           | see Figure 9: "Dead time and interlocking waveform definitions" |      | 180  |      | ns   |  |

Table 12: Op-amp characteristics (Vcc = 15 V unless otherwise specified)

| Symbol          | Parameter                      | Test conditions                                           | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------------|-----------------------------------------------------------|------|------|------|------|

| Vio             | Input offset voltage           | V <sub>ic</sub> = 0 V, V <sub>o</sub> = 7.5 V             |      |      | 6    | mV   |

| l <sub>io</sub> | Input offset current           | $V_{ic} = 0 \text{ V}, V_0 = 7.5 \text{ V}$               |      | 4    | 40   | nA   |

| l <sub>ib</sub> | Input bias current (1)         | $V_{1C} = U V, V_0 = 7.5 V$                               |      | 100  | 200  | nA   |

| Vol             | Low level output voltage       | $R_L = 10 \text{ k}\Omega \text{ to V}_{CC}$              |      | 75   | 150  | mV   |

| V <sub>OH</sub> | High level output voltage      | $R_L$ = 10 k $\Omega$ to GND                              | 14   | 14.7 |      | V    |

|                 | Output short-circuit           | Source, $V_{id} = +1 \text{ V}$ ; $V_o = 0 \text{ V}$     | 16   | 30   |      | mA   |

| current         |                                | Sink, $V_{id} = -1 V$ ; $V_0 = V_{CC}$                    | 50   | 80   |      | mA   |

| SR              | Slew rate                      | $V_i = 1 - 4 \text{ V}; C_L = 100 \text{ pF};$ unity gain | 2.5  | 3.8  |      | V/µs |

| GBWP            | Gain bandwidth product         | V <sub>o</sub> = 7.5 V                                    | 8    | 12   |      | MHz  |

| A <sub>vd</sub> | Large signal voltage gain      | R <sub>L</sub> = 2 kΩ                                     | 70   | 85   |      | dB   |

| SVR             | Supply voltage rejection ratio | vs. Vcc                                                   | 60   | 75   |      | dB   |

| CMRR            | Common mode rejection ratio    |                                                           | 55   | 70   |      | dB   |

#### Notes:

$<sup>^{\</sup>left( 1\right) }The$  direction of input current is out of the IC.

Table 13: Sense comparator characteristics (V<sub>CC</sub> = 15 V unless otherwise specified)

| Symbol              | Parameter Test conditions Min.                                             |                                                               | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------------------------------------------------|---------------------------------------------------------------|------|------|------|------|

| l <sub>ib</sub>     | Input bias current                                                         | V <sub>CIN</sub> = 1 V                                        |      |      | 3    | μΑ   |

| V <sub>od</sub>     | Open-drain low level output voltage                                        | I <sub>od</sub> = 3 mA                                        |      |      | 0.5  | V    |

| R <sub>ON_OD</sub>  | Open-drain low level output resistance                                     | I <sub>od</sub> = 3 mA                                        |      | 166  |      | Ω    |

| R <sub>PD_SD</sub>  | SD pull-down resistor (1)                                                  |                                                               |      | 125  |      | kΩ   |

| t <sub>d_comp</sub> | Comparator delay                                                           | T/SD/OD pulled to 5 V through 100 kΩ resistor                 |      | 90   | 130  | ns   |

| SR                  | Slew rate                                                                  | $C_L = 180 \text{ pF}; R_{pu} = 5 \text{ k}\Omega$            |      | 60   |      | V/µs |

| t <sub>sd</sub>     | Shutdown to high / low-<br>side driver propagation<br>delay                | $V_{OUT} = 0$ , $V_{boot} = V_{CC}$ , $V_{IN} = 0$ to 3.3 V   | 50   | 125  | 200  | 20   |

| tisd                | Comparator triggering to high / low-side driver turn-off propagation delay | Measured applying a voltage step from 0 V to 3.3 V to pin CIN | 50   | 200  | 250  | ns   |

#### Notes:

Table 14: Truth table

| Condition                                | Logic input (V <sub>I</sub> ) |                  |                  | Output |     |  |

|------------------------------------------|-------------------------------|------------------|------------------|--------|-----|--|

| Condition                                | T/SD/OD                       | LIN              | HIN              | LVG    | HVG |  |

| Shutdown enable half-bridge tri-state    | L                             | X <sup>(1)</sup> | X <sup>(1)</sup> | L      | L   |  |

| Interlocking half-bridge tri-state       | Н                             | Н                | Η                | L      | L   |  |

| 0 "logic state" half-bridge tri-state    | Н                             | L                | Ш                | L      | L   |  |

| 1 "logic state" low-side direct driving  | Н                             | Н                | L                | Н      | L   |  |

| 1 "logic state" high-side direct driving | Н                             | L                | Η                | L      | Н   |  |

#### Notes:

(1)X: don't care.

$<sup>^{(1)}</sup>$ Equivalent values as a result of the resistances of three drivers in parallel.

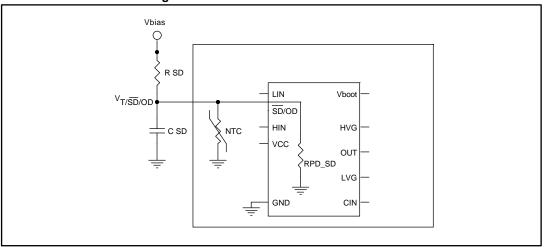

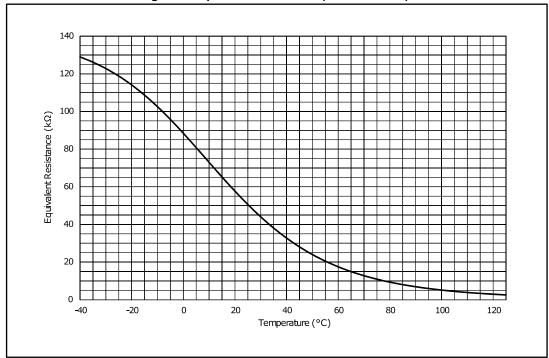

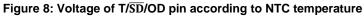

#### 3.2.1 NTC thermistor

Figure 5: Internal structure of  $\overline{\text{SD}}$  and NTC

RPD\_SD: equivalent value as result of resistances of three drivers in parallel.

Figure 6: Equivalent resistance (NTC//RPD\_SD)

14

12

(G)

10

10

14

12

10

10

10

10

10

110

120

Temperature (°C)

Figure 7: Equivalent resistance (NTC//RPD\_SD) zoom

#### 3.3 Waveform definitions

Figure 9: Dead time and interlocking waveform definitions

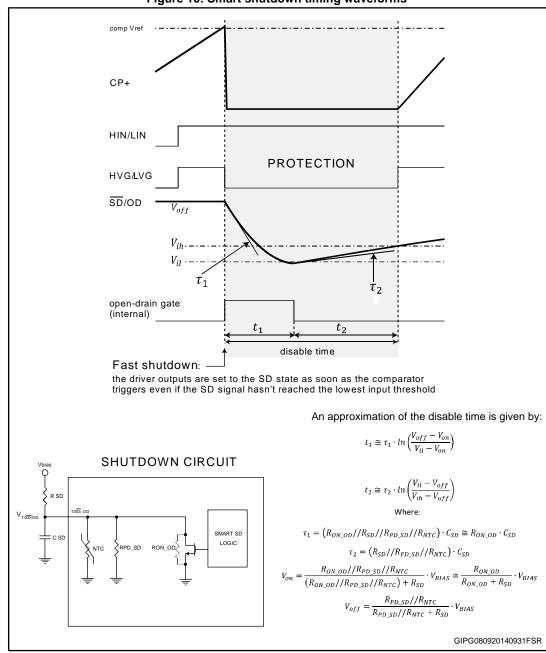

### 4 Smart shutdown function

The device integrates a comparator for fault sensing purposes. The comparator has an internal voltage reference  $V_{\text{REF}}$  connected to the inverting input, while the non-inverting input on pin (CIN) can be connected to an external shunt resistor for simple overcurrent protection.

When the comparator triggers, the device is set to the shutdown state and both of its outputs are set to the low level, causing the half-bridge to enter a tri-state.

In common overcurrent protection architectures, the comparator output is usually connected to the shutdown input through an RC network so to provide a monostable circuit which implements a protection time following to a fault condition.

Our smart shutdown architecture immediately turns off the output gate driver in case of overcurrent through a preferential path for the fault signal which directly switches off the outputs. The time delay between the fault and output shutdown no longer depends on the RC values of the external network connected to the shutdown pin. At the same time, the DMOS connected to the open-drain output (pin T/SD/OD) is turned on by the internal logic, which holds it on until the shutdown voltage is lower than the minimum value of logic input threshold.

Besides, the smart shutdown function allows the real disable time to be increased while the constant time of the external RC network remains as it is.

An NTC thermistor for temperature monitoring is internally connected in parallel to the  $\overline{\text{SD}}$  pin. To avoid undesired shutdown, keep the voltage.  $V_{T/\overline{\text{SD}}/OD}$  higher than the high-level logic threshold by setting the pull-up resistor  $V_{T/\overline{\text{SD}}/OD}$  to 1 k $\Omega$  or 2.2 k $\Omega$  for 3.3 V or 5 V MCU power supplies, respectively.

Figure 10: Smart shutdown timing waveforms

Please refer to *Table 13:* "Sense comparator characteristics ( $V_{CC} = 15 \text{ V unless otherwise specified}$ )" for internal propagation delay time details.

## 5 Application circuit example

Σ : c1 7 HinV(10) 3 Ĩ ( N N N N P MICROCONTROLLER GADG100620160912FSR

Figure 11: Application circuit example

Application designers are free to use a different scheme according to the specifications of the device.

#### 5.1 Guidelines

- Input signals HIN, LIN are active high logic. A 375 k $\Omega$  (typ.) pull-down resistor is built-in for each input. To prevent the input signal oscillation, the wiring of each input should be as short as possible and the use of RC filters (R1, C1) on each input signal is suggested. The filters should be with a time constant of about 100 ns and placed as close as possible to the IPM input pins.

- The use of a bypass capacitor CVCC (aluminum or tantalum) can help to reduce the transient circuit demand on the power supply. Besides, to reduce high frequency switching noise distributed on the power lines, a decoupling capacitor C<sub>2</sub> (100 to 220 nF, with low ESR and low ESL) should be placed as close as possible to V<sub>cc</sub> pin and in parallel with the bypass capacitor.

- The use of RC filter (RSF, CSF) is recommended to avoid protection circuit malfunction. The time constant (RSF x CSF) should be set to 1 μs and the filter must be placed as close as possible to CIN pin.

- The  $\overline{SD}$  is an input/output pin (open-drain type if used as output). A built-in thermistor NTC is internally connected between the  $\overline{SD}$  pin and GND. The voltage VSD-GND decreases as the temperature increases, due to RSD pull-up resistor. In order to be sure that the voltage is always higher than the high level logic threshold, the pull-up resistor should be set to 1 kΩ or 2.2 kΩ for 3.3 V or 5 V MCU power supply, respectively. The CSD capacitor of the filter on  $\overline{SD}$  should not be higher than 3.3 nF in order to assure the  $\overline{SD}$  activation time T₁≤ 500 ns; the filter should be placed as close as possible to the  $\overline{SD}$  pin.

- The decoupling capacitor C<sub>3</sub> (from 100 to 220 nF, ceramic with low ESR and low ESL), in parallel with each C<sub>boot</sub>, filters the high frequency disturbance. Both C<sub>boot</sub> and C<sub>3</sub> (if present) should be placed as close as possible to the U, V, W and V<sub>boot</sub> pins. Bootstrap negative electrodes should be connected to U, V, W terminals directly and separated from the main output wires.

- To prevent the overvoltage on  $V_{cc}$  pin, a Zener diode (Dz1) can be used. Similarly on the  $V_{boot}$  pin, a Zener diode (Dz2) can be placed in parallel with each  $C_{boot}$ .

- The use of the decoupling capacitor C<sub>4</sub> (100 to 220 nF, with low ESR and low ESL), in parallel with the electrolytic capacitor C<sub>vdc</sub>, prevents surge destruction. Both capacitors C<sub>4</sub> and C<sub>vdc</sub> should be placed as close as possible to the IPM (C<sub>4</sub> has priority over C<sub>vdc</sub>).

- By integrating an application-specific type HVIC inside the module, direct coupling to the MCU terminals without an optocoupler is possible.

- Low inductance shunt resistors should be used for phase leg current sensing.

- In order to avoid malfunctions, the wiring on N pins, the shunt resistor and PWR\_GND should be as short as possible.

- The connection of SGN\_GND to PWR\_GND on one point only (close to the shunt resistor terminal) can help to reduce the impact of power ground fluctuation.

These guidelines are useful for application designs to ensure the specifications of the device. For further details, please refer to the relevant application note.

**Table 15: Recommended operating conditions**

| Symbol            | Parameter                          | Test conditions                                                      |    | Тур. | Max. | Unit |

|-------------------|------------------------------------|----------------------------------------------------------------------|----|------|------|------|

| $V_{PN}$          | Supply voltage                     | Applied among P-Nu, Nv, Nw                                           |    | 300  | 400  | V    |

| Vcc               | Control supply voltage             | e Applied to Vcc-GND 13.5 15                                         |    | 15   | 18   | V    |

| V <sub>BS</sub>   | High-side bias voltage             | Applied to V <sub>BOOTi</sub> -OUT <sub>i</sub> for i = U, V, W      | 13 |      | 18   | ٧    |

| t <sub>dead</sub> | Blanking time to prevent arm-short | For each input signal                                                | 1  |      |      | μs   |

| fрwм              | PWM input signal                   | -40 °C < T <sub>c</sub> < 100 °C<br>-40 °C < T <sub>j</sub> < 125 °C |    |      | 25   | kHz  |

| Tc                | Case operation temperature         |                                                                      |    |      | 100  | °C   |

## 6 Package information

20/25

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

STIPN1M50T-H Package information

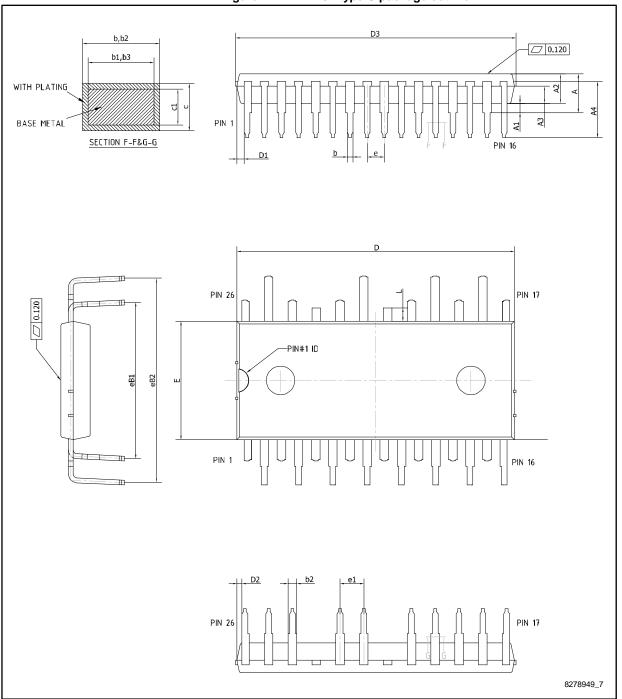

## 6.1 NDIP-26L package information

Figure 12: NDIP-26L type C package outline

Table 16: NDIP-26L type C mechanical data

| Dim  |       | mm    |       |

|------|-------|-------|-------|

| Dim. | Min.  | Тур.  | Max.  |

| А    |       |       | 4.40  |

| A1   | 0.80  | 1.00  | 1.20  |

| A2   | 3.00  | 3.10  | 3.20  |

| A3   | 1.70  | 1.80  | 1.90  |

| A4   | 5.70  | 5.90  | 6.10  |

| b    | 0.53  |       | 0.72  |

| b1   | 0.52  | 0.60  | 0.68  |

| b2   | 0.83  |       | 1.02  |

| b3   | 0.82  | 0.90  | 0.98  |

| С    | 0.46  |       | 0.59  |

| c1   | 0.45  | 0.50  | 0.55  |

| D    | 29.05 | 29.15 | 29.25 |

| D1   | 0.50  | 0.77  | 1.00  |

| D2   | 0.35  | 0.53  | 0.70  |

| D3   |       |       | 29.55 |

| Е    | 12.35 | 12.45 | 12.55 |

| е    | 1.70  | 1.80  | 1.90  |

| e1   | 2.40  | 2.50  | 2.60  |

| eB1  | 16.10 | 16.40 | 16.70 |

| eB2  | 21.18 | 21.48 | 21.78 |

| L    | 1.24  | 1.39  | 1.54  |

STIPN1M50T-H Package information

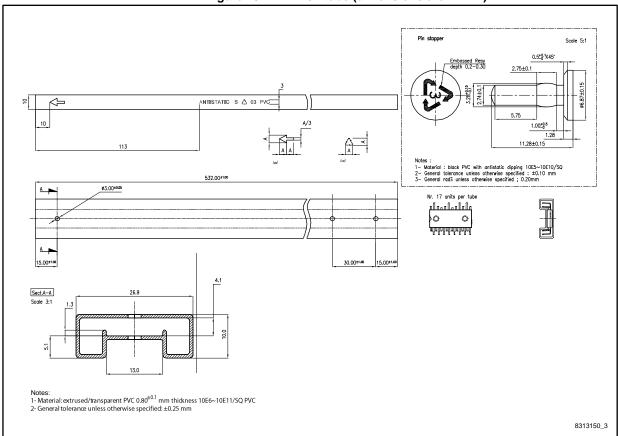

## 6.2 NDIP-26L packing information

Figure 13: NDIP-26L tube (dimensions are in mm)

Table 17: Shipping details

| Parameter     | Value      |  |  |

|---------------|------------|--|--|

| Base quantity | 17 pieces  |  |  |

| Bulk quantity | 476 pieces |  |  |

Revision history STIPN1M50T-H

## 7 Revision history

**Table 18: Document revision history**

| Date          | Revision | Changes                                                                                                                                                                                                                                                                                             |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03-Feb-2016   | 1        | Initial release.                                                                                                                                                                                                                                                                                    |

| 07-Mar-2016   | 2        | Document status promoted from preliminary to production data.  Updated title and features in cover page.  Updated Table 7: Inverter part, Figure 3: Switching time test circuit, Figure 4: Switching time definition and Section 6.2: Packing information.  Minor text changes.                     |

| 12-Jul-2016   | 3        | Updated title and features in cover page. Updated Section 3: Electrical characteristics, Figure 11: Application circuit example and Section 5.1: Guidelines.  Updated Section 6.1: NDIP-26L package information.  Document status changed from preliminary to production data.  Minor text changes. |

| 02-Feb-2017 4 |          | Modified <i>Table 15: "Recommended operating conditions".</i> Minor text changes.                                                                                                                                                                                                                   |

| 08-Jun-2017   | 5        | Modified <i>Table 3: "Inverter part"</i> , <i>Table 6: "Thermal data"</i> .  Modified <i>Section 5.1: "Guidelines"</i> .  Minor text changes.                                                                                                                                                       |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved