# ProxSense<sup>®</sup> IQS333 Datasheet

# 9 Channel Projected / 7 Channel Self- Capacitive Touch and Proximity Controller with 2 x 11-bit slider/scroll wheels

The **IQS333** ProxSense<sup>®</sup> IC is a 9-channel projected (or 7-channel self) capacitive proximity and touch controller with best in class sensitivity, signal to noise ratio and power consumption. Other features include automatic tuning of sense electrodes, internal reference capacitor and internal regulator to reduce total system cost.

### **Main Features**

- 7 Self or 9 Mutual Channel Capacitive Controller

- 2 Configurable 11-bit sliders/scroll wheels

- Advanced on-chip digital signal processing

- Automatic adjustment for optimal performance (ATI)

- User selectable Proximity and Touch thresholds

- Long proximity range

- Automatic drift compensation

- Fast I<sup>2</sup>C Interface

- Event mode or Streaming modes

- 8 PWM LED/Output drivers (5mA source/10mA sink)

- Hardware PWM set through  $I^2C$  memory map no overhead from host

- o Dimming modes available, up and down

- Minimum, maximum & adjustable limit levels for dimming modes

- Low Power, suitable for battery applications

- Supply voltage: 1.8V to 3.6V

- <3µA Active sensing in LP mode

### Applications

- White goods and appliances

- Office equipment, toys

- Medical and test equipment

- Blu-Ray, DVD players, TVs

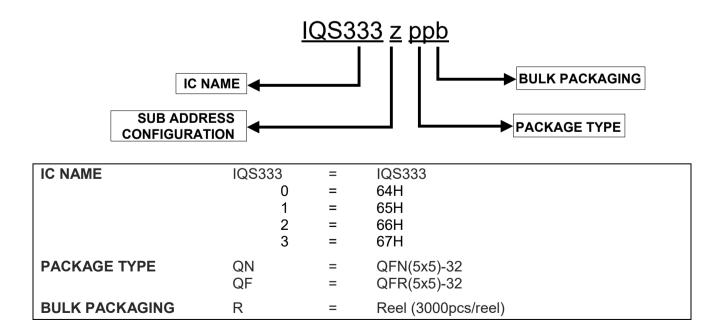

### Available options

| T <sub>A</sub> | QFR(5x5)-32 |

|----------------|-------------|

| -20°C to 85°C  | IQS333      |

IQS333 QFR32 Representations only, not actual markings

### Contents

| FUN                        | CTIONAL OVERVIEW                        |

|----------------------------|-----------------------------------------|

| 1                          | INTRODUCTION                            |

| 2                          | ANALOGUE FUNCTIONALITY                  |

| 3                          | DIGITAL FUNCTIONALITY                   |

| 4                          | HARDWARE CONFIGURATION                  |

| 5                          | USER CONFIGURABLE OPTIONS               |

| 6                          | PROXSENSE <sup>®</sup> MODULE           |

| 7                          | COMMUNICATION                           |

| 8                          | RF NOISE                                |

|                            |                                         |

| 9                          | COMMUNICATION COMMAND/ADDRESS STRUCTURE |

| 9<br>10                    | COMMUNICATION COMMAND/ADDRESS STRUCTURE |

| -                          |                                         |

| 10                         | IQS333 OTP OPTIONS                      |

| 10<br>11                   | IQS333 OTP OPTIONS                      |

| 10<br>11<br>12             | IQS333 OTP OPTIONS                      |

| 10<br>11<br>12<br>13       | IQ\$333 OTP OPTIONS                     |

| 10<br>11<br>12<br>13<br>14 | IQS333 OTP OPTIONS                      |

# **Functional Overview**

# 1 Introduction

The **IQS333** is a 9 channel projected (7 self) capacitive proximity and touch sensor featuring an internal voltage regulator and reference capacitor ( $C_s$ ).

The device has 7 possible pins for the connection of the sense electrodes, which consist of 7 Self electrodes, or 3 transmitters and 3 receivers. Three pins are used for serial data communication through the  $I^2C^{TM}$  compatible protocol, including an optional RDY pin. Up to 9 configurable outputs provide 8 PWM or general purpose I/O's. There is also a dedicated pin for driving a buzzer.

The device automatically tracks slow varying environmental changes via various filters, detects noise and is equipped with an Automatic Tuning Implementation (ATI) to adjust the device for optimal sensitivity.

# 1.1 Applicability

All specifications, except where specifically mentioned otherwise, provided by this datasheet are applicable to the following ranges:

- Temperature -20°C to +85°C

- Supply voltage (V<sub>DDHI</sub>) 1.8V to 3.6V

# 2 Analogue Functionality

CRX and CTX electrodes are arranged in a suitable configuration that results in a mutual capacitance (Cm) between the two electrodes. CTX is charged up to a set positive potential during a charge cycle which results in a negative charge buildup at CRX.

The resulting charge displacement is then measured within the **IQS333** device

through a charge transfer process that is periodically initiated by the digital circuitry. The capacitance measurement circuitry makes use of an internal reference capacitor  $C_S$  and voltage reference ( $V_{REF}$ ).

The measuring process is referred to as a conversion and consists of the discharging of Cs and Cx capacitors, the charging of Cx and then a series of charge transfers from Cx to Cs until a trip voltage is reached. The number of charge transfers required to reach the trip voltage is referred to as the Counts (CS) value.

The analogue circuitry further provides functionality for:

- Power On Reset (POR) detection.

- Brown Out Detection (BOD).

- Internal regulation provides for accurate sampling.

# **3 Digital Functionality**

The digital processing functionality is responsible for:

- Managing BOD and WDT events.

- Initiation of conversions at the selected rate.

- Processing of CS and execution of algorithms.

- Monitoring and execution of the ATI algorithm.

- Signal processing and digital filtering.

- Detection of PROX and TOUCH events.

- Managing outputs of the device.

- Managing serial communications.

# 4 Hardware Configuration

The **IQS333** can be configured to charge in Self- or Projected-Capacitive mode through the memory map by the host controller. The **IQS333** is default in Self-Capacitive mode, and can be set to Projected-Capacitive mode by setting the "Proj Mode" bit in <u>Register 0x01</u>, byte 0.

In **Self-Capacitive** mode, the **IQS333** has 7 channels. It can be used as 7 discrete buttons OR 1 slider and 4 buttons, OR 2 sliders with 1 button.

In **Projected-Capacitive** mode, the **IQS333** has 9 channels. It can be used as 9 discrete buttons OR 1 slider with 6 buttons, OR 2 sliders with 3 buttons.

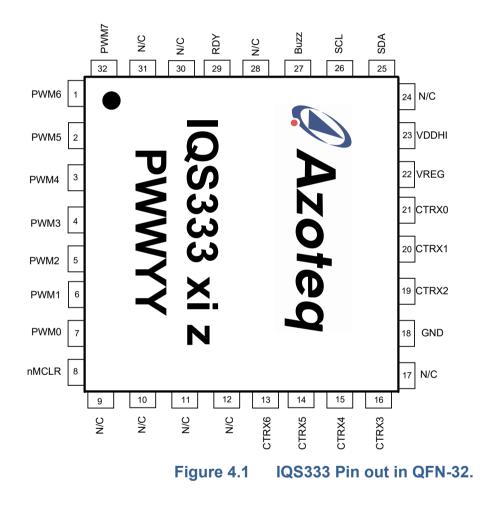

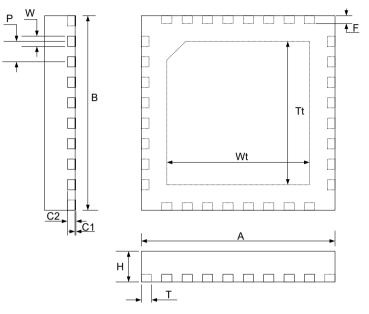

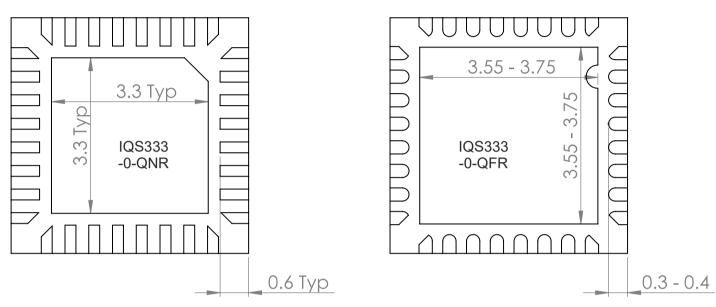

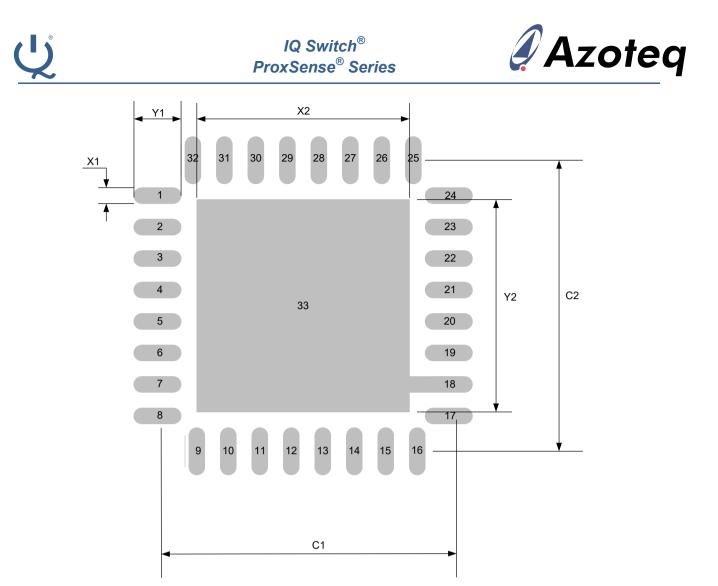

# 4.1 IQS333 Pin Out

# IQ Switch<sup>®</sup> ProxSense<sup>®</sup> Series

# Table 4.1 IQS333 QFN-32 Pin-outs.

| Pin | Self-Capacitive Projected-Capacitive |              | Function               |  |  |

|-----|--------------------------------------|--------------|------------------------|--|--|

| 1   | PWM6                                 | PWM6         | Output                 |  |  |

| 2   | PWM5                                 | PWM5         | Output                 |  |  |

| 3   | PWM4                                 | PWM4         | Output                 |  |  |

| 4   | PWM3                                 | PWM3         | Output                 |  |  |

| 5   | PWM2                                 | PWM2         | Output                 |  |  |

| 6   | PWM1                                 | PWM1         | Output                 |  |  |

| 7   | PWM0                                 | PWM0         | Output                 |  |  |

| 8   | NMCLR                                | NMCLR        | Master Clear           |  |  |

| 9   | N/C                                  | N/C          | No Connect             |  |  |

| 10  | Internal use <sup>1</sup>            | Internal use | No Connect             |  |  |

| 11  | Internal use                         | Internal use | No Connect             |  |  |

| 12  | Internal use                         | Internal use | No Connect             |  |  |

| 13  | CX6                                  |              | Sense Electrode        |  |  |

| 14  | CX5                                  | TX2          | Sense Electrode        |  |  |

| 15  | CX4                                  | TX1          | Sense Electrode        |  |  |

| 16  | CX3                                  | TX0          | Sense Electrode        |  |  |

| 17  | N/C                                  | N/C          | No Connect             |  |  |

| 18  | GND                                  | GND          | Supply Ground          |  |  |

| 19  | CX2                                  | CRX2         | Sense Electrode        |  |  |

| 20  | CX1                                  | CRX1         | Sense Electrode        |  |  |

| 21  | CX0                                  | CRX0         | Sense Electrode        |  |  |

| 22  | VREG                                 | VREG         | Regulator Output       |  |  |

| 23  | VDDHI                                | VDDHI        | Supply Input           |  |  |

| 24  | Internal use                         | Internal use | No Connect             |  |  |

| 25  | SDA                                  | SDA          | I <sup>2</sup> C Data  |  |  |

| 26  | SCL                                  | SCL          | I <sup>2</sup> C Clock |  |  |

| 27  | BUZ                                  | BUZ          | Buzzer                 |  |  |

| 28  | N/C                                  | N/C          | Connect to GND         |  |  |

| 29  | RDY                                  | RDY          | Ready                  |  |  |

| 30  | N/C                                  | N/C          | No Connect             |  |  |

| 31  | N/C                                  | N/C          | No Connect             |  |  |

| 32  | PWM7                                 | PWM7         | Output                 |  |  |

<sup>1</sup> Do not connect to GND

# 4.2 Reference Design

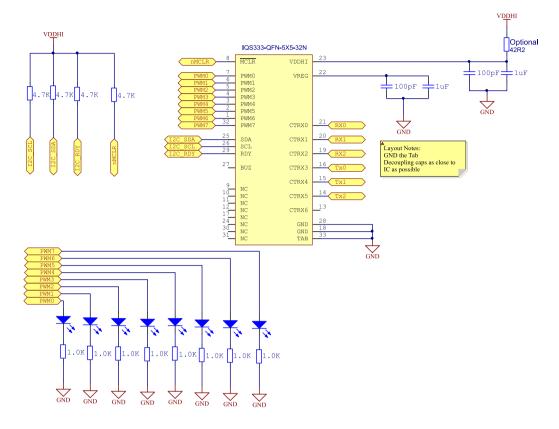

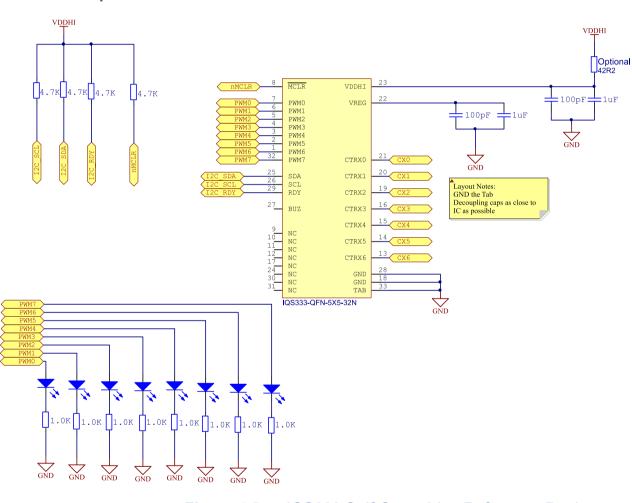

# 4.2.1 Projected Schematic

Figure 4.2 IQS333 Reference Design (Projected capacitive sensing). 4.2.2 Projected Electrodes

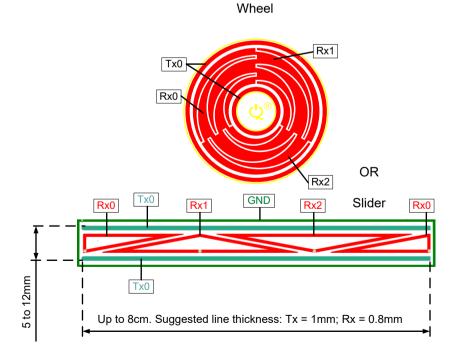

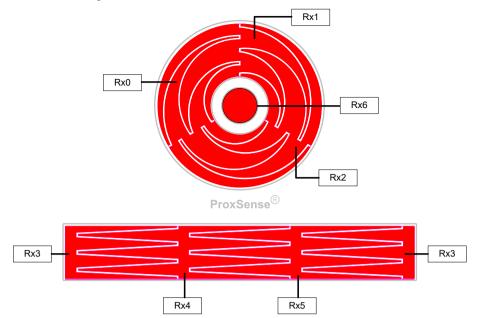

Figure 4.3 Projected-Capacitive Wheel, Slider and Button layout guidelines. DXF files for wheels and sliders are available on request: <u>info@azoteq.com.</u>

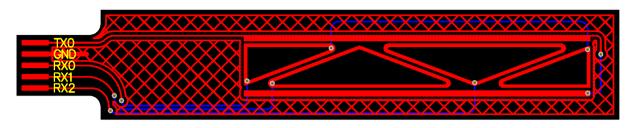

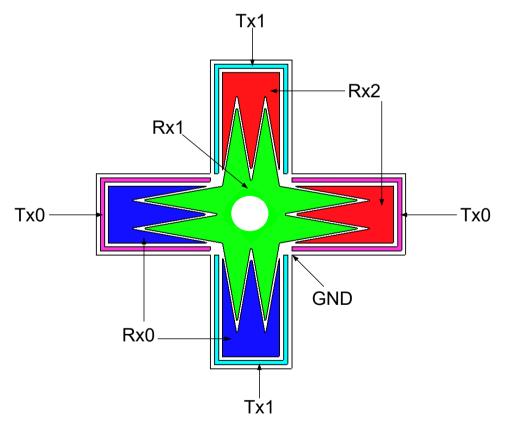

### 4.2.3 Example Routing

Figure 4.4 Example routing of a projected slider. GND on top layer shields the Rx lines from the user on the bottom layer.

### 4.2.4 Self-capacitive Schematic

Figure 4.5 IQS333

IQS333 Self Capacitive Reference Design.

IQ Switch<sup>®</sup> ProxSense<sup>®</sup> Series

### 4.2.5 Self Electrode Layouts

Figure 4.6 Self-Capacitive Wheel, Slider and Button layout guidelines. DXF files for wheels and sliders are available on request: <u>info@azoteq.com.</u>

Figure 4.7 Projected XY-cross slider, made possible by the reuse of the Rx electrodes. As these sliders do not wrap around, the full resolution specified will not be achievable.

# 4.3 Power Supply and PCB Layout

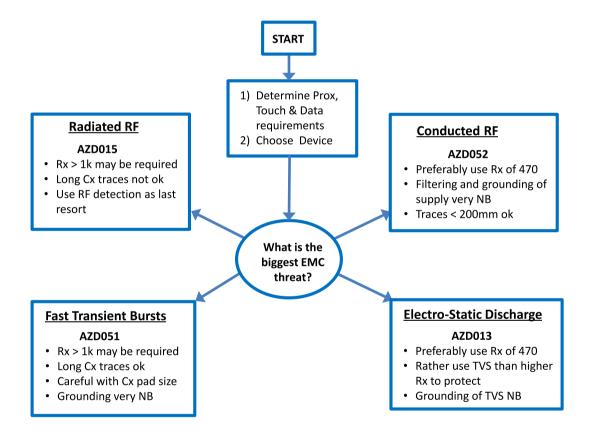

Azoteq IC's provide a high level of on-chip hardware and software noise filtering and ESD protection (refer to application note "*AZD013 – ESD Overview*"). Designing PCB's with better noise immunity against EMI, FTB and ESD in mind, it is always advisable to keep the critical noise suppression components like the de-coupling capacitors and series resistors in **Figure 4.2** as close as possible to the IC. Always maintain a good ground connection and ground pour underneath the IC. For more guidelines please refer to the relevant application notes as mentioned in **Section 4.4**.

Where a system level ESD strike is found to cause the IC to go into ESD induced latch-up, it is suggested that the supply current to the IQS333 IC is limited by means of a series resistor that could limit the maximum supply current to the IC to <80mA.

# 4.4 Design Rules for Harsh EMC Environments

### > Applicable application notes: AZD013, AZD015, AZD051, and AZD052.

# 4.5 High Sensitivity

Through patented design and advanced signal processing, the device is able to provide extremely high sensitivity to detect proximity. This enables designs to detect proximity at distances that cannot be equaled by most other products. When the device is used in environments where high levels of noise or floating metal objects exist, a reduced proximity threshold is proposed to ensure reliable functioning of the sensor. The high sensitivity also

allows the device to sense through overlay materials with low dielectric constants, such as wood or porous plastics.

For more guidelines on the layout of capacitive sense electrodes, please refer to application note *AZD008*, available on the Azoteq web page: <u>www.azoteq.com</u>.

# **5** User Configurable Options

The **IQS333** requires configuration by a master/host controller or MCU. The user needs to select the number of channels and corresponding touch and proximity thresholds.

# 5.1 Self and Projected Modes

The **IQS333** can function as a Self or Projected capacitive controller, depending on the application requirement. The **IQS333** is default in Self capacitive mode. Pre-configured devices can be ordered for projected mode, or the user can select the operation mode as projected during initialization by setting the "Proj Mode" bit in <u>Register 0x01</u>, byte 0 (Sysflags0).

### **5.2 Active Channels**

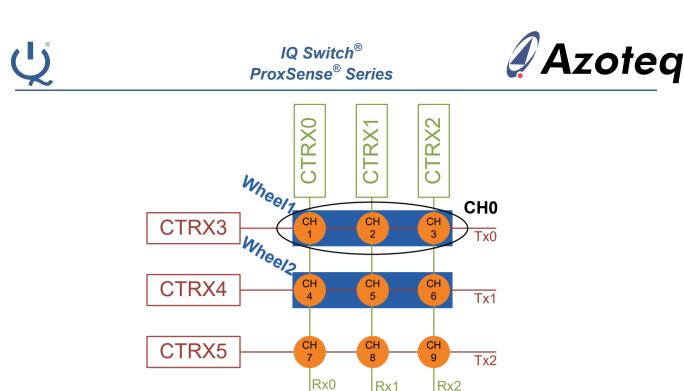

The **IQS333** can be configured to have up to 9 active touch channels (CH1-CH9) with one additional proximity channel (CH0) in projected charging mode. By default CH0 is a distributed proximity channel, comprised of charging all the channels together in one timeslot. There is an option to only charge Tx0 (transmitter) and CTRX0 – CTRX2 (receivers) together (see Figure 5.1). by setting the CH0\_Settings bit in <u>Register 0x08</u>, byte 6.

The **IQS333** can be configured to have up to 7 active touch channels (CH1-CH7) with one additional proximity channel (CH0) in self-capacitive charging mode. CH0 is a distributed proximity channel, comprised of charging all the channels together in one timeslot.

The desired number of channels can be selected in **Register 0x0E**.

**Figure 5.1** illustrates the **IQS333** channels mapped to the respective transmit (CTX) and receive (CRX) sense electrodes. Tx0 is used with all three Rx lines to form wheel 1, and Tx1 is used with all three lines to form wheel 2. All three Rx lines are charged together with Tx0 to for the distributed proximity channel (CH0).

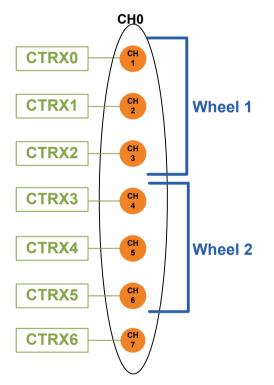

**Figure 5.2** illustrates the **IQS333** channels mapped to the respective CTRX lines in Self capacitive charging mode. CX0 to CX2 forms wheel 1, while CX 3 to CX 5 forms wheel 2. All the channels are charged together to form 1 distributed proximity channel (CH0).

Figure 5.1 IQS333 Channel Mapping in Projected mode. By default CH0 charges all the channels, but can be set to only use Tx0 as shown.

### 5.3 Proximity Threshold

A proximity threshold for channel 0 can be selected by the designer in **Register 0x09**, byte 0, to obtain the desired proximity trigger level. The proximity threshold is selectable between 1 (most sensitive) and

255 (least sensitive) counts. These threshold values (i.e. 1-255) are specified in Counts (CS). Note: The **IQS333** has a default proximity threshold of 4 counts,  $P_{THR} = 4$ .

# 5.4 Touch Thresholds

A touch threshold for each channel can be selected by the designer to obtain the desired touch sensitivity and is selectable between 1/256 (most sensitive) to 255/256 (least sensitive). The touch threshold is calculated as a fraction of the Long-Term Average (LTA) given by,

$$T_{THR} = \frac{x}{256} \times LTA$$

With lower target values (therefore lower LTA's) the touch threshold will be lower and vice versa.

Individual touch thresholds can be set for each channel (excl. CH0) in <u>Register 0x09</u>, byte 1 to 9.

Note: The **IQS333** has a default touch threshold of 16/256\*LTA for all active channels.

## 5.5 Wheel Enable/Disable

The **IQS333** has the option to enable or disable wheel/slider coordinate calculations on 2 wheels. By default, both wheels will be enabled, but can disabled by setting the Wheel\_Disable bits in <u>Register 0x08</u>, byte 3 (ProxSettings3).

# 5.6 Wheel Resolution

Both wheels/sliders have resolution up to 11-bit. The resolution can be adjusted between 4-bit and 11-bit, depending on the application requirements and wheel size. The resolution of the wheels cannot be adjusted individually. To adjust the resolution, set the Resolution bits in **Register 0x08**, byte 3 (ProxSettings3).

### 5.7 Wheel Filter

A filter is implemented on both wheels/sliders to smooth the output. This filter can be disabled to increase the response rate by setting the Wheel Filter Disable bit in <u>Register 0x08</u>, byte 3 (ProxSettings3).

### 5.8 Halt times

The Halt Timer is started when a proximity or touch event occurs and is restarted when that event is removed or reoccurs. When a proximity or touch event condition occurs, the LTA values for all channels will be "halted", thus its values will be kept fixed, until the proximity event is cleared, or the halt timer reaches the halt time. The halt timer will count to the selected halt time  $(t_{HALT})$ , which can be configured in **Register 0x0A**, byte 0. There is also the option to change to never halt or always halt instead of t<sub>HALT</sub> by setting the HALT bits in **Register** 0x08, byte 2 (ProxSettings2) When the timer expires, the output will be cleared, and a reseed or re-ATI event will occur (depending on whether the counts are within the ATI band).

It is possible that the CS (Count Value) could be outside the ATI boundary (ATI Target +- 12.5%) when the timer expires, which will cause the device to perform a re-ATI event on that channel and not just a reseed event.

The designer needs to select a halt timer value  $(t_{HALT})$  to best accommodate the required application. The value of  $t_{HALT}$  is selectable between 1 and 255 (times 250ms). The default value is 0x50H (80 decimal times 250ms = 20 seconds).

There is also the option to set  $t_{HALT}$  timer to never halt, or always halt in <u>Register 0x08</u>, byte 2 (Prox\_Settings2).

# 5.9 AC Filter

The AC filter can be implemented to provide better stability of Counts (CS) in electrically noisy environments.

The AC filter also enforces a longer minimum sample time for detecting proximity events on CH0, which will result in a slower response rate when the device

enters low power modes. The AC filter can be disabled in <u>Register 0x08</u>, byte 2 (Prox\_Settings2).

The AC filter is implemented on all channels, to aid in the slider coordinate calculations, but touch events are determined on unfiltered count values.

# 5.10 Power Modes

### 5.10.1 LP Modes

The **IQS333** IC has a wide range of configurable low power modes, specifically designed to reduce current consumption for low power and battery applications.

The power modes are implemented around the occurrence of a charge cycle every  $t_{LP}$  seconds. The value of  $t_{LP}$  is determined by the custom (LP<sub>value</sub>) value between 1 and 255 in <u>Register 0x0A</u>, byte 2, multiplied by 16ms. Only CH0 is charged during LP, and is forced active (CH0 cannot be disabled). The other active channels will be periodically charged to keep their LTA filter values up to date.

Lower sampling frequencies typically yield significant lower power consumption (but also decreases the response time)

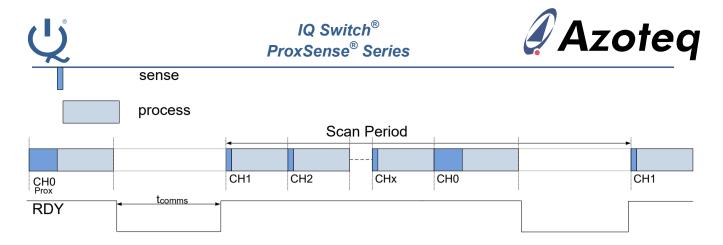

NOTE: While in any power mode the device will zoom to Boost Power (BP) mode whenever the condition  $(CS - LTA)^{1}$ PROX TH > or TOUCH TH holds, indicating a possible proximity or touch event. This improves the response time. The device will remain in BP for t<sub>ZOOM</sub> and then return to the selected power mode. The Zoom function allows reliable detection of events with counts being produced at the BP rate. The LP charge cycle timing is illustrated in Figure 5.3. The bit0 in Register 0x01, byte 0 (Sys Flags0), will indicate if low power is active, or the device is zoomed in.

<sup>&</sup>lt;sup>1</sup> CS-LTA in Projected mode. LTA-CS in Self capacitive sensing mode.

|             | sense                   |          |  |

|-------------|-------------------------|----------|--|

|             | process                 |          |  |

| ·           | Scan Period = LP x 16ms | <b>-</b> |  |

|             |                         |          |  |

| CH0<br>Prox |                         | СНО      |  |

| RDY         | ← Icomms →              |          |  |

### Figure 5.3 IQS333 Charge Cycle Timing in Low Power Mode.

Typical timings of the charge sequence shown above are listed in Table 5.1. These timings are only as reference, as they will differ with each application, depending on the setup of the **IQS333**. For example, the sense (or charge time) is affected by the target counts and charge transfer frequency, while process time is dependent on the turbo mode activation, ATI checking for counts within the pre-set band, filter settings and slider calculations. Communication time is affected by the MCU clock speed and the amount of data read (as well as the sequence thereof) and can be bypassed with using Event Mode. Communication time and the number of active channels will influence the Scan Period. Values shown below are for default settings.

### Table 5.1Typical Timings in LP mode

| Typical timings of IQS333 |                          |    |  |  |

|---------------------------|--------------------------|----|--|--|

| t <sub>sense</sub>        | 900                      | μs |  |  |

| t <sub>process</sub>      | 1.4                      | ms |  |  |

| t <sub>comms</sub>        | 6                        | ms |  |  |

| Scan Period <sup>1</sup>  | LP register setting x 16 | ms |  |  |

<sup>&</sup>lt;sup>1</sup> All channels active, and all data read during communication window. Projected mode, all other settings default.

### 5.10.2 Turbo Mode

Setting the Turbo Mode bit in Register 0x08, byte 1 (Prox settings1) will enable the IQS333 device to perform conversions (charge transfers or sensing) as fast as processing and communication allows. Enabling Turbo Mode will maximizing detection speeds, but also increasing current consumption. Disabling Turbo Mode will yield in a fixed sampling period t<sub>Sample.</sub>

### 5.11 ATI Method

The IQS333 can be set up to perform sensor calibration in three ways: Full ATI, Partial ATI and Alternative ATI. The ATI method is selected or turned off in <u>Register</u> <u>0x08</u>, byte 0 (Prox\_Settings0).

In **Full ATI** mode, the device automatically selects the multipliers through the ATI algorithm to setup the **IQS333** as close as possible to its default sensitivity for the environment where it was placed.

The user can however, select **Partial ATI**, and set the multipliers to pre-configured values. This will cause the **IQS333** to only calculate the compensation (not the compensation and multipliers as in Full ATI), which allows the freedom to make the **IQS333** more or less sensitive for its intended environment of use. The Partial ATI also reduces start-up and re-ATI times.

In Alternative ATI, the **IQS333** will take the smallest multiplier values from Full ATI, and apply it to all the channels, and the algorithm will determine the compensation values. Special attention should be paid to layout when using Alternative ATI when using a wheel and/or slider, as multipliers for sliders and touch keys are not always in the same range.

### 5.12 Base Value

The **IQS333** has the option to individually change the base value of each channel during the Full ATI algorithm. Depending on the application, this provides the user with another option to select the sensitivity of the **IQS333** without changes in the hardware (CRX/CTX sizes and routing, etc).

The base values are set in <u>Register 0x06</u>, byte 0 to 9 (for channels 0 to 9). The base values can be selected to be **200**(default), **75, 100 or 150**.

The base value influences the overall sensitivity of the channel and establishes a base count from where the ATI algorithm starts executing. A lower base value will typically result in a higher sensitivity of the respective channel, as lower multipliers will be selected, and more compensation would be required.

### 5.13 Target Value

The default target value of the **IQS333** is 512 counts for the touch channels and 1024 counts for the proximity channel.

The target values are calculated by multiplying the value in <u>Register 0x0B</u>, byte 0 (for channel 0) & byte 1 (for channels 1 to 9) by 8.

Example: CH0 target = Register Value x 8 = 128(default) x 8 = 1024.

# 5.14 Charge Transfer Speed

The frequency at which charge cycles are performed can be adjusted by the Charge Xfer Speed bits in <u>Register 0x08</u>, byte 1 (Prox\_Settings1).

Adjusting the charge transfer speed will change the charge cycle duration ( $t_{SENSE}$ ) as shown in **Figure 5.3**.

The charge transfer frequency is a fraction of the main oscillator (FOSC = 8MHz) and

can be set at **1MHz** (default), **500kHz**, **250kHz** (not recommended for projected) or **2MHz**.

Higher charge transfer speeds are preferred for applications that require increased immunity against aqueous substances.

## 5.15C<sub>s</sub> Size

Another method to adjust the sensitivity of the IQS333 is to change the size of the internal  $C_s$  capacitor. The size on default is 60pF, but can be changed to 30pF by setting the  $C_s$ \_Size bit in <u>Register 0x08</u>, byte 0 (Prox\_Settings0). Choosing the smaller  $C_s$  size will effectively reduce the number of counts before ATI, thus changing the multiplier and compensation values required to reach the ATI target.

### 5.16 Projected Bias

The IQS333 has the option to change the bias current of the transmitter during projected sensing mode. A larger bias current is required to use larger electrodes, but will also increase the IC power consumption. The bias current is default on  $10\mu$ A, and can be changed in <u>Register</u> <u>0x08</u>, byte 0 (Prox\_Settings0).

### **5.17 Additional Features**

### 5.17.1 Halt Charge

Setting the Halt Charge bit in <u>Register</u> <u>0x08</u>, byte 1 (Prox\_Settings1), will stop all conversions.

This function is typically useful for ultra-low power requirements, where the **IQS333** can be controlled by a host MCU and does not require wake-up on proximity or touch events. This is a low power alternative to switching off, where no sensing is required, to avoid resetting the memory map.

### 5.17.2 Force Halt

The Force Halt bit in <u>Register 0x08</u>, byte 2 (Prox\_Settings2) can be set to halt all

current LTA values and prevent them from being adjusted towards the CS values.

Setting this bit overrides all filter halt settings and prevents the device from performing re-ATI events in cases where the CS values persist outside the ATI boundaries for extended periods of time. Reseed will also not be possible.

### 5.17.3 CTX / CRX Float

During the charge transfer process, the channels that are not being processed during the current cycle, are effectively grounded to decrease the effects of noisecoupling between the sense electrodes. Grounding these traces is useful in applications with long tracks between IC and sense electrode.

In <u>Register 0x08</u>, byte 5, there is the option to specify which channels' transmit and/or receive electrodes to float when they are not charged. This is particularly useful for applications with self-capacitive wheels/sliders with thick overlays, where more sensitivity is required. Sensitivity will be increased when floating the wheel channels, as they charge in series, and not parallel.

# 6 ProxSense<sup>®</sup> Module

The **IQS333** contains a ProxSense<sup>®</sup> module that uses patented technology to provide detection of proximity and touch conditions on numerous sensing lines.

The ProxSense<sup>®</sup> module is a combination of hardware and software, based on the principles of charge transfer measurements.

# 6.1 Charge Transfer Concept

On ProxSense<sup>®</sup> devices like the IQS333, capacitance measurements are taken with a charge transfer process that is periodically initiated.

For projected capacitive sensing, the device measures the capacitance between 2 electrodes referred to as the transmitter (CTX) and receiver (CRX).

The measuring process is referred to as a charge transfer cycle and consists of the following:

- Discharging of an internal sampling capacitor (C<sub>s</sub>) and the electrode capacitors (mutual: CTX & CRX) on a channel.

- charging of CTX's connected to the channel

- and then a series of charge transfers from the CRX's to the internal sampling capacitors (C<sub>s</sub>), until the trip voltage is reached.

The number of charge transfers required to reach the trip voltage on a channel is referred to as the Current Sample (**CS**) or Count value (Counts).

The device continuously repeats charge transfers on the sense electrodes connected to the CRX pins. For each channel a Long Term Average (LTA) is calculated (12 bit unsigned integer values). The count (CS) values (12 bit unsigned integer values) are processed and compared to the LTA to detect Touch and Proximity events.

Please note: Attaching scope probes to the CTX/CRX pins will influence the capacitance of the sense electrodes and therefore the related CS values of those channels. This will have an instant effect on the CS measurements.

# 6.2 Rate of Charge Cycles

The **IQS333** samples all its active channels (up to 9 + channel 0 for proximity) in 10 timeslots. The charge sequence (as measured on the receive electrodes) is shown in Figure 6.1, where CH0, the Proximity channel, charges first, followed by all other active channels. There is only a communication window after all active channels have been charged.

The charging of CH0 comprises the simultaneous charging of the three receive electrodes (CRX0, CRX1 and CRX2) in conjunction with all transmit electrodes, thus realising a distributed load mutual capacitive sense electrode. Refer to **Figure 5.1** for **IQS333** channel numbering. The user has the option to only charge 1 Tx (Tx0/CTRX3) together with all 3 receivers, by setting the 1 Tx bit in <u>Register 0x08</u>, byte 1 (Prox\_Settings1).

In self-capacitive mode, CH0 is also a distributed channel charging all 7 CX channels together.

### 6.2.1 Boost Power rate

With the **IQS333** zoomed to Boost Power (BP) mode, the active channels are charged at a fixed sampling period (t<sub>SAMPLE</sub>) per channel (if Turbo Mode is not enabled). This is done to ensure regular samples for processing of results, and fix timings for the halt times.

It is calculated as each channel having a time t<sub>SAMPLE</sub> = charge/conversion time (t<sub>SENSE</sub>) + computation time (t<sub>PROCESS</sub>) of approximately t<sub>SAMPLE</sub> = 1.6ms. Thus the time between consecutive samples on a specific channel (Scan Period) will depend on the number of enabled channels and the length of communication between the **IQS333** and the host MCU. Communication will always happen after processing of the last active channel. Due to processing and charging happening in parallel, CH0 will charge while the last active channel is Therefore, processed. communication windows will always be after CH0 has charged.

### Figure 6.1 IQS333 Charge Sequence timing diagram in Boost Power mode.

Typical timings of the charge sequence shown above are listed in Table 6.1. These timings are only as reference, as they will differ with each application, depending on the setup of the **IQS333**. For example, the sense (or charge time) is affected by the target counts and charge transfer frequency, while process time is dependent on the turbo mode activation, ATI checking for counts within the pre-set band, filter settings and slider calculations. Communication time is affected by the MCU clock speed and the amount of data read (as well as the sequence thereof) and can be bypassed with using Event Mode. Communication time and the number of active channels will influence the Scan Period. Values shown below are for default settings.

### Table 6.1Typical Timings

| Typical timings of IQS333 |     |    |  |  |

|---------------------------|-----|----|--|--|

| t <sub>sense</sub>        | 600 | μs |  |  |

| t <sub>process</sub>      | 1.4 | ms |  |  |

| t <sub>comms</sub>        | 6   | ms |  |  |

| Scan Period <sup>1</sup>  | 26  | ms |  |  |

<sup>&</sup>lt;sup>1</sup> All channels active, and all data read during communication window. Projected mode, all other settings default.

### 6.2.2 Low Power rate

A wide range of low current consumption charging modes is available on the **IQS333**.

In any Low Power (LP) mode, there will be an applicable low power time  $(t_{LP})$ . This is determined by <u>Register 0x0A</u>, byte 1. The value written into this register multiplied by 16ms will yield the LP time  $(t_{LP})$ .

With the detection of an undebounced proximity event the IC will zoom to BP mode, allowing a very fast reaction time for further possible touch events.

During any LP mode, only channel 0 is charged every  $t_{LP}$ . The LP charge timing is illustrated in **Figure 5.3**.

If a low power rate is selected and charging is not in the zoomed state (BP mode), the low power active bit (Register 0x01) will be set.

Please refer to **Section 5.10**.

# 6.3 Touch report Rate

During Boost Power (BP) mode, the touch report rate of the **IQS333** device depends on the charge transfer frequency, the number of channels enabled and the length of communications performed by the host MCU or master device.

Several factors may influence the touch report rate:

- Enabled channels: Disabling channels that are not used will not only increase the touch report rate, but will also reduce the device's current consumption.

- Turbo Mode: See Section 5.10.2

- **Target Values:** Lower target values requires shorter charge transfer times (t<sub>SENSE</sub>), thus reducing the SCAN PERIOD and increasing the touch report rate.

- Charge Transfer Speed: Increasing the charge transfer frequency will reduce the conversion time (t<sub>SENSE</sub>) and increase the touch report rate.

- **ACF:** Disabling the AC filter and wheel/slider position calculations will reduce the processing time (t<sub>PROCESS</sub>) and yield a faster report rate.

# 6.4 Long Term Average

The Long-term Average (LTA) filter can be seen as the baseline or reference value. The LTA is calculated to continuously adapt to any environmental drift. The LTA filter is calculated from the CS value for each channel. The LTA filter allows the device to adapt to environmental (slow moving) changes/drift. Actuation (Touch or Prox) decisions are made by comparing the CS value with the LTA reference value.

The 12bit LTA values are contained in **Register 0x05**. Low bytes first, from CH0 up to CH9 (18 bytes in total).

Please refer to **Section 5.8** for LTA Halt Times.

# 6.5 Determine Touch or Prox

An event is determined by comparing the CS value with the LTA. Since the CS reacts differently when comparing the self- with the mutual capacitance technology, the user should consider only the conditions for the technology used.

An event is recorded if:

- Self: CS < LTA **Threshold**

- Projected: CS > LTA + Threshold

**Threshold** can be either a Proximity or Touch threshold, depending on the current channel being processed.

Note that a proximity condition will be forced enabled if there is a touch condition on any channel.

Please refer to **Section 1.1** and **5.4** for proximity and touch threshold selections.

# 6.6 ATI

The Automatic Tuning Implementation (ATI) is a sophisticated technology implemented on the new ProxSense<sup>®</sup> series devices. It allows for optimal performance of the devices for a wide range of sense electrode capacitances, without modification or addition of external components.

The ATI allows the tuning of two parameters, an ATI Multiplier and an ATI Compensation, to adjust the Count values for an attached sense electrode.

ATI allows the designer to optimize a specific design by adjusting the sensitivity and stability of each channel through the adjustment of the ATI parameters.

The **IQS333** has a full ATI function. The full-ATI function is default enabled, but can be disabled by setting the ATI\_OFF bit, or changed to partial or alternative ATI by setting the ATI\_Partial and ATI\_ALT bits in **Register 0x08**, byte 0.

The ATI\_Busy bit in **<u>Register 0x01</u>**, byte 0 (Sysflags0) will be set while an ATI event is busy.

For more information regarding the ATI algorithm, please contact Azoteq at: <u>ProxSenseSupport@azoteq.com</u>

### 6.6.1 ATI Sensitivity

On the **IQS333** device, the user can specify the BASE value (**Section 5.12**) for each channel individually and the TARGET values (**Section 5.13**) for the proximity (CH0) and touch (CH1-CH9) channels.

Sensitivity is a function of base and target values as follows:

# $Sensitivity \propto \frac{TARGET}{BASE}$

As can be seen from this equation, the sensitivity can be increased by either increasing the Target value or decreasing the Base value. It should, however, be noted that a higher sensitivity will yield a higher noise susceptibility.

### 6.6.2 ATI Target

The target value is reached by adjusting the COMPENSATION bits for each channel (ATI target limited to 4096 counts).

The target value is written into the respective channel's TARGET registers. The value written into these registers multiplied by 8 will yield the new target value. (Please refer to **Section 5.13**)

### 6.6.3 ATI Base (Multiplier)

The base value is calculated with the compensation set to zero. The following parameters will influence the base value:

- C<sub>s</sub>\_SIZE<sup>1</sup>: Size of sampling capacitor.

- PROJ\_BIAS bits: Adjusts the biasing of some analogue parameters in the mutual capacitive operated IC. (Only applicable in mutual capacitance mode.)

- Charge Transfer Frequency

- MULTIPLIER bits.

The base value used for the ATI function can be implemented in 2 ways:

ATI\_PARTIAL = 0. ATI automatically adjusts MULTIPLIER bits to reach a selected base value<sup>2</sup>. Please refer to **Section 5.12** for available base values.

<sup>&</sup>lt;sup>1</sup> Changing CS\_SIZE if ATI\_OFF = 0 will change CS

$<sup>^2</sup>$  ATI function will use user selected CS\_SIZE and PROJ\_BIAS (if applicable) and will only adjust the MULTIPLIER bits to reach the base values.

2. ATI PARTIAL = 1. The designer can specify the multiplier settings. These settings will give a custom base value from where the compensation bits will be automatically implemented to reach the required target value. The base value is determined by two sets of multiplier bits. Sensitivity Multipliers which will also scale the compensation to normalise the sensitivity and Compensation Multipliers to adjust the gain.

### 6.6.4 Re-ATI

An automatic re-ATI event will occur if the counts are outside its re-ATI limits. The re-ATI limit or ATI boundary is calculated as the target value divided by 8. For example:

- Target = 512, Re-ATI will occur if CS is outside 512±64.

A re-ATI event can also be issued by the host MCU by setting the REDO\_ATI bit in **Register 0x08**, byte0 (ProxSettings0). The REDO\_ATI bit will clear automatically after the ATI event was started.

Note: Re-ATI will automatically clear all proximity, touch and halt status bits.

### 6.6.5 Reseed

Setting the Reseed bit in <u>Register 0x08</u>, byte 0), will shift all LTA filters to a value of

# 7 Communication

$LTA_{new} = CS + 8$  (CS – 8 for Self). The LTA will then track the CS value until they are even.

Performing a reseed action on the LTA filters, will effectively clear any proximity and/or touch conditions that may have been established prior to the reseed call.

#### 6.6.6 Alternative ATI

The Alternative ATI implementation ensures that all the multiplier values are identical for all the channels and adjusts only the compensation in order to achieve the desired count value. The multipliers are selected from the channel with the smallest multipliers according to the full ATI algorithm. Alternative ATI can be enabled in **Register 0x08**, byte 0.

### 6.6.7 ATI ERROR

The ATI error bit (read only) in <u>Register</u> <u>0x08</u>, byte 1 (Prox\_Settings1) indicates to the user that the ATI targets where not reached. Adjustments of the base values or ATI BANDs are required.

### 6.6.8 ATI Band

The user has the option to select the re-ATI band as 1/8 of the ATI target (default) or 1/4 of the ATI target counts by setting the ATI BAND bit in <u>Register 0x08</u>, byte 1 (Prox\_Settings1).

The **IQS333** device interfaces to a master controller via a 3-wire (SDA, SCL and RDY) serial interface bus that is  $I^2C^{TM}$  compatible, with a maximum communication speed of 400kbit/s.

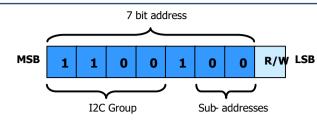

# 7.1 Control Byte

The Control byte indicates the 7-bit device address (64H default) and the Read/Write indicator bit. The structure of the control byte is shown in Figure 7.1.

The  $I^2C$  device has a 7 bit Slave Address (default 0x64H) in the control byte as shown in Figure 7.1. To confirm the address, the software compares the received address with the device address. Sub-address values can be set by OTP programming options.

# 7.2 I<sup>2</sup>C Read

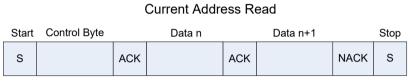

To read from the device a *current address read* can be performed. This assumes that the address-command is already setup as desired.

Figure 7.2 Current Address Read.

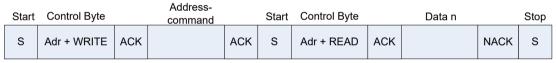

If the address-command must first be specified, then a *random read* must be performed. In this case a WRITE is initially performed to setup the address-command, and then a repeated start is used to initiate the READ section.

Figure 7.3 Random Read.

# 7.3 I<sup>2</sup>C Write

To write settings to the device a *Data Write* is performed. Here the Address-Command is always required, followed by the relevant data bytes to write to the device.

|       | DATA WRITE   |     |                     |     |        |     |          |     |      |

|-------|--------------|-----|---------------------|-----|--------|-----|----------|-----|------|

| Start | Control Byte |     | Address-<br>Command |     | Data n |     | Data n+1 |     | Stop |

| S     | Adr + WRITE  | АСК |                     | ACK |        | ACK |          | АСК | S    |

Figure 7.4 I<sup>2</sup>C Write.

# 7.4 End of Communication Session / Window

Similar to other Azoteq I<sup>2</sup>C devices, to end the I<sup>2</sup>C communication session, a STOP command is given. When sending numerous read and write commands in one communication cycle, a repeated start command must be used to stack them together (since a STOP will jump out of the communication window, which is not desired).

The STOP will then end the communication, and the **IQS333** will return to process a new set of data. Once this is obtained, the communication window will again become available (RDY set LOW).

# 7.5 I<sup>2</sup>C Sub-address

The **IQS333** has four available sub addresses, 64H (default) to 67H, which allows up to four devices on a single  $I^2C$  bus.

### 7.5.1 Internal sub-address selection

Selecting the sub-address via OTP bits allows the user 4 different options:

### Table 7.1I<sup>2</sup>C sub-address selection

| FG25 | FG26 | Device Address |

|------|------|----------------|

| 0    | 0    | 0x64           |

| 0    | 1    | 0x65           |

| 1    | 0    | 0x66           |

| 1    | 1    | 0x67           |

# 7.6 Event Mode

By default the device operates in full streaming mode. There is an option for an event-driven I<sup>2</sup>C communication mode (also called "Event Mode"), with the RDY pin ONLY indicating a communication window after a prescribed event has occurred.

These events include:

- Proximity events

- Touch events

- ATI events

- Noise events (Noise detect enabled)

If the wheels/sliders are enabled, the device will stream data continuously when a touch is present on one of the wheel/slider channels, even if Event Mode is enabled. This allows the wheel/slider coordinates to be read continuously.

Event Mode can be enabled by setting the Event\_Mode bit in <u>Register 0x08</u>, byte 2 (Prox\_Settings2).

Note: The device is also capable of functioning **without** a RDY line on a polling basis.

# 7.7 RDY Hand-Shake Routine

The master or host MCU has the capability to force a communication window at any time, by pulling the RDY line low. The communication window will open directly following the current conversion cycle.

# 7.8 I<sup>2</sup>C Specific Commands

### 7.8.1 Show Reset

The SHOW\_RESET bit can be read in **Register 0x01**, byte 1 (Sysflags0), to determine whether a reset has occurred on the device. This bit will be set '1' after a reset. A reset can be forced by writing the Soft\_Reset bit in **Register 0x08**, byte 2 (ProxSettings2).

The SHOW\_RESET bit will be cleared (set to '0') by writing a '1' into the ACK\_RESET bit in <u>Register 0x08</u>, byte 3 (ProxSettings3). A reset will typically take place if a timeout during communication occurs.

### 7.8.2 WDT disable

The WDT (watchdog timer) is used to reset the IC if a problem (for example a voltage spike) occurs during communication. The WDT will time-out (and thus reset the device) after  $t_{WDT}$  if no valid communication occurred during this time.

The WDT can be disabled by setting the WDT Off bit in <u>Register 0x08</u>, byte 2 (ProxSettings2).

### 7.8.3 Timeout Disable

If no communication is initiated from the master/host MCU within the first  $t_{COMMS}$  ( $t_{COMMS}$  = 20ms) of the RDY line indicating that data is available (i.e. RDY = low), the device will resume with the next cycle of charge transfers and the data from the previous conversions will be lost.

This time-out function can be disabled by setting the TIME\_OUT DISABLE bit in **Register 0x08**, byte 2 (ProxSettings2).

### 7.8.4 Soft Reset

The user has the option to do a soft reset on the **IQS333.** The soft reset will clear all the registers (the device will restart as with POR) except the PWM register will keep their state.

A soft reset is initiated by setting the bit in **Register 0x08**, byte 2 (Prox\_Settings2). The bit Soft Reset bit will automatically clear after the command is sent.

## 7.9 I<sup>2</sup>C I/O Characteristics

The **IQS333** requires the input voltages given in **Table 7.2**, for detecting high ("1") and low ("0") input conditions on the  $I^2C$  communication lines (SDA, SCL and RDY).

### Table 7.2IQS333 I²C Input voltage

|                     | Input Voltage (V) |

|---------------------|-------------------|

| Vin <sub>LOW</sub>  | 0.3*VDDHI         |

| Vin <sub>HIGH</sub> | 0.7*VDDHI         |

Table 7.3 provides the output voltage levels of the IQS333 device during  $I^2C$  communication.

### Table 7.3IQS333 I2C Output voltage

|                      | Output Voltage (V) |

|----------------------|--------------------|

| Vout <sub>LOW</sub>  | VSS +0.2 (max.)    |

| Vout <sub>HIGH</sub> | VDDHI – 0.2 (min.) |

# 7.10 PWM Controller

The **IQS333** incorporates a highly configurable controller to implement PWM user configurable LED lighting displays. The various PWM control modes can be easily configured with an  $I^2C$  interface by writing directly to the control bytes in the memory map. There are 8 identical PWM modules with 15.625kHz PWM carrier frequency which can be controlled independently to allow for a wide range of user configurable options

## 7.11 PWM Diming modes

The hardware PWM channels can be controlled through the memory map various diming modes. These include:

- Incrementing to 100%

- Incrementing to a set level

- Decrementing to 0%

- Decrementing to a set level

The speed of the dimming modes is also configurable.

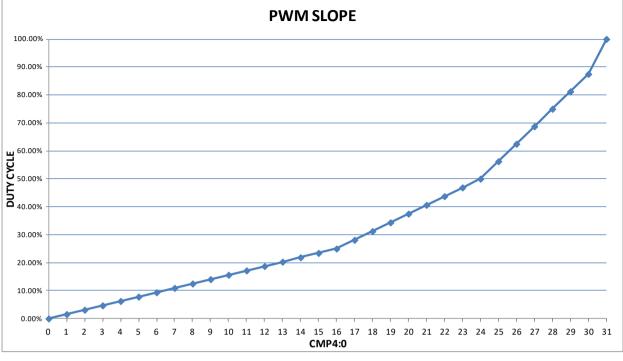

# 7.12 PWM Duty Cycle Mapping

Although there are only 5 PWM bits in the MM, the resolution of the PWM engine is effectively 6 bits to ensure a more linear increase in LED brightness. A 6 bit internal timer is compared to a PWM value comprised of the Duty Cycle bits CMP4:0 in <u>Register</u> <u>0x0C</u>, bytes 0 to 7.

### Table 7.4 PWM Duty Cycle Mapping

| CMP4:0 | PWM Timer<br>Count | PWM DUTY |

|--------|--------------------|----------|

| 0      | 0                  | 0.00%    |

| 1      | 1                  | 1.56%    |

| 2      | 2                  | 3.13%    |

| 3      | 3                  | 4.69%    |

| 4      | 4                  | 6.25%    |

| 5      | 5                  | 7.81%    |

| 6      | 6                  | 9.38%    |

| 7      | 7                  | 10.94%   |

| 8      | 8                  | 12.50%   |

| 9      | 9                  | 14.06%   |

| 10     | 10                 | 15.63%   |

| 11     | 11                 | 17.19%   |

| Copyright © Azoteq (Pty) Ltd 2017. |  |

|------------------------------------|--|

| All rights reserved.               |  |

| CMP4:0 | PWM Timer<br>Count | PWM DUTY |  |  |  |

|--------|--------------------|----------|--|--|--|

| 12     | 12                 | 18.75%   |  |  |  |

| 13     | 13                 | 20.31%   |  |  |  |

| 14     | 14                 | 21.88%   |  |  |  |

| 15     | 15                 | 23.44%   |  |  |  |

| 16     | 16                 | 25.00%   |  |  |  |

| 17     | 18                 | 28.13%   |  |  |  |

| 18     | 20                 | 31.25%   |  |  |  |

| 19     | 22                 | 34.38%   |  |  |  |

| 20     | 24                 | 37.50%   |  |  |  |

| 21     | 26                 | 40.63%   |  |  |  |

| 22     | 28                 | 43.75%   |  |  |  |

| 23     | 30                 | 46.88%   |  |  |  |

| 24     | 32                 | 50.00%   |  |  |  |

| 25     | 36                 | 56.25%   |  |  |  |

| 26     | 40                 | 62.50%   |  |  |  |

| 27     | 44                 | 68.75%   |  |  |  |

| 28     | 48                 | 75.00%   |  |  |  |

| 29     | 52                 | 81.25%   |  |  |  |

| 30     | 56                 | 87.50%   |  |  |  |

| 31     | 64                 | 100.00%  |  |  |  |

Figure 7.5 PWM Slope.

# 8 **RF Noise**

Please see application note: "AZD015: RF Immunity and detection in ProxSense devices" for details regarding RF noise and capacitive sensing.

# 8.1 RF Noise Immunity

The **IQS333** has advanced immunity to RF noise sources such as GSM cellular telephones, DECT, Bluetooth and WIFI devices. Design guidelines should however be followed to ensure the best noise immunity on a hardware level.

In general, the design of capacitive sensing applications may encompass a large range of configurations; however, following the guidelines in **Section 8.1.1** may improve a capacitive sensing design.

### 8.1.1 Notes for layout:

A ground plane should be placed under the IC, except under the CRX lines.

- Place the sensor IC as close as possible to the sense electrodes.

- All the tracks on the PCB must be kept as short as possible.

- The capacitor between VDDHI and GND as well as between VREG and GND must be placed as close as possible to the IC.

- A 100 pF capacitor can be placed in parallel with the 1uF capacitor between VDDHI and GND. Another 100 pF capacitor can be placed in parallel with the 1uF capacitor between VREG and GND.

- When the device is too sensitive for a specific application a parasitic capacitor (max 5pF) can be added between the CX line and ground.

- Proper sense electrode and button design principles must be followed.

- Unintentional coupling of sense electrodes to ground and other circuitry must be limited by

increasing the distance to these sources.

- In some instances a ground plane some distance from the device and sense electrode may provide significant shielding from undesirable interference.

- \* However, if after proper layout, interference from an RF noise source persists, please refer to application note: "AZD015: RF Immunity and detection in ProxSense devices".

IQ Switch<sup>®</sup> ProxSense<sup>®</sup> Series

# 9 Communication Command/Address Structure

# 9.1 Registers

### Table 9.1 IQS333 Registers

| Address | Description        | Access | Section |

|---------|--------------------|--------|---------|

| 0x00H   | Device Information | R      | 9.2.1   |

| 0x01H   | System Flags       | R/W    | 9.2.2   |

| 0x02H   | Wheel Coordinates  | R      | 0       |

| 0x03H   | Touch Bytes        | R      | 9.2.4   |

| 0x04H   | Counts             | R      | 9.2.5   |

| 0x05H   | LTA                | R      | 9.2.6   |

| 0x06H   | Multipliers        | R/W    | 9.2.7   |

| 0x07H   | Compensation       | R/W    | 9.2.8   |

| 0x08H   | ProxSettings       | R/W    | 9.2.9   |

| 0x09H   | Thresholds         | R/W    | 9.2.10  |

| 0x0AH   | Timings            | R/W    | 9.2.11  |

| 0x0BH   | Targets            | R/W    | 9.2.12  |

| 0x0CH   | PWM Duty           | R/W    | 9.2.13  |

| 0x0DH   | PWM LIM            | R/W    | 9.2.14  |

| 0x0EH   | Active Channels    | R/W    | 9.2.15  |

| 0x0FH   | Buzzer             | R/W    | 9.2.16  |

# 9.2 Registers Descriptions

### 9.2.1 Device Information 0x00H

Information regarding the device type and version is recorded here. Any other information specific to the device version can be stored here. Each Azoteq ROM has a unique Productand Version number.

|        |       |   | Product Number (PROD_NUM) |   |   |   |   |   |   |  |  |

|--------|-------|---|---------------------------|---|---|---|---|---|---|--|--|

| Access | Bit   | 7 | 6                         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| R      | Value |   | 54 (Decimal) <sup>1</sup> |   |   |   |   |   |   |  |  |

|        | _     |   | Version Number (VERSION_NUM) |  |  |  |  |  |  |  |  |

|--------|-------|---|------------------------------|--|--|--|--|--|--|--|--|

| Access | Bit   | 7 | 7 6 5 4 3 2 1 0              |  |  |  |  |  |  |  |  |

| R      | Value |   | 02 (Decimal)                 |  |  |  |  |  |  |  |  |

## 9.2.2 System Flags 0x01H

|        |      |               | System Flags (SYSFLAGS0) |              |        |              |             |                       |      |  |  |

|--------|------|---------------|--------------------------|--------------|--------|--------------|-------------|-----------------------|------|--|--|

| Access | Bit  | 7             | 6                        | 5            | 4      | 3            | 2           | 1                     | 0    |  |  |

| R/W    | Name | Show<br>reset | Filter<br>Halted         | Proj<br>Mode | ls Ch0 | LP<br>Active | ATI<br>Busy | Noise<br>detect<br>ed | Zoom |  |  |

Bit 5:

0 = Self Capacitive Sensing (Default)

1 = Projected Capacitive Sensing

### 9.2.3 Wheel Coordinates 0x02H

|        |      |               | Wheel 1 Low                       |  |  |  |  |  |  |  |  |

|--------|------|---------------|-----------------------------------|--|--|--|--|--|--|--|--|

| Access | Bit  | 7 6 5 4 3 2 1 |                                   |  |  |  |  |  |  |  |  |

| R      | Name |               | Wheel 1 Coordinate Low byte first |  |  |  |  |  |  |  |  |

|        |      |   | Wheel 1 High                                                                                                   |  |  |  |  |  |  |  |  |

|--------|------|---|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Access | Bit  | 7 | 7         6         5         4         3         2         1         0           Wheel 1 Coordinate High byte |  |  |  |  |  |  |  |  |

| R      | Name |   |                                                                                                                |  |  |  |  |  |  |  |  |

<sup>1</sup> Product and Version numbers are 32 14 for QFN20 devices – alpha customers only

|                                                                                          |      |  | Wheel 2 Low                       |  |  |  |  |  |   |  |  |

|------------------------------------------------------------------------------------------|------|--|-----------------------------------|--|--|--|--|--|---|--|--|

| Access         Bit         7         6         5         4         3         2         1 |      |  |                                   |  |  |  |  |  | 0 |  |  |

| R                                                                                        | Name |  | Wheel 2 Coordinate Low byte first |  |  |  |  |  |   |  |  |

|        |      |   | Wheel 2 High                 |  |  |  |  |  |  |  |  |

|--------|------|---|------------------------------|--|--|--|--|--|--|--|--|

| Access | Bit  | 7 | 7 6 5 4 3 2 1 0              |  |  |  |  |  |  |  |  |

| R      | Name |   | Wheel 2 Coordinate High byte |  |  |  |  |  |  |  |  |

## 9.2.4 Touch Bytes 0x03H

|        |      |     | Touch Byte 0 |     |     |     |     |     |                  |  |

|--------|------|-----|--------------|-----|-----|-----|-----|-----|------------------|--|

| Access | Bit  | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0                |  |

| R      | Name | CH7 | CH6          | CH5 | CH4 | СНЗ | CH2 | CH1 | CH0 <sup>1</sup> |  |

Bit 0 of the first byte (CH0) will indicate proximity events; the rest of the bits indicate touches as shown.

|        |      |               | Touch Byte 1 |  |  |  |  |     |     |  |

|--------|------|---------------|--------------|--|--|--|--|-----|-----|--|

| Access | Bit  | 7 6 5 4 3 2 1 |              |  |  |  |  |     |     |  |

| R      | Name |               |              |  |  |  |  | CH9 | CH8 |  |

### 9.2.5 Counts 0x04H

This register has 18 bytes to store the count values of CH0 up to CH9 the low byte will always read out first, followed by the high byte, before the moving to the next channel.

|        |      |   | CH0 Low                              |  |  |  |  |  |  |  |  |

|--------|------|---|--------------------------------------|--|--|--|--|--|--|--|--|

| Access | Bit  | 7 | 7 6 5 4 3 2 1 0                      |  |  |  |  |  |  |  |  |

| R      | Name |   | Channel 0 CS (Counts) Low byte first |  |  |  |  |  |  |  |  |

<sup>1</sup> CH0 indicates Proximity, not Touch.

|        |      |   |                                                   |   | CH n | High |   |   |   |  |  |  |  |  |

|--------|------|---|---------------------------------------------------|---|------|------|---|---|---|--|--|--|--|--|

| Access | Bit  | 7 | 6                                                 | 5 | 4    | 3    | 2 | 1 | 0 |  |  |  |  |  |

| R      | Name |   | Last active channel, Count value (High byte last) |   |      |      |   |   |   |  |  |  |  |  |

### 9.2.6 LTA 0x05H

This register has 18 bytes to store the LTA values of CH0 up to CH9 the low byte will always read out first, followed by the high byte, before the moving to the next channel.

|        |      |   |                 |  | CH0 LTA | Low byte | • |  |  |  |  |  |  |  |  |

|--------|------|---|-----------------|--|---------|----------|---|--|--|--|--|--|--|--|--|

| Access | Bit  | 7 | 7 6 5 4 3 2 1 0 |  |         |          |   |  |  |  |  |  |  |  |  |

| R      | Name |   |                 |  |         |          |   |  |  |  |  |  |  |  |  |

|        |      |   |                 | ( | CH n LTA | High byt | e |  |  |  |  |  |  |  |  |

|--------|------|---|-----------------|---|----------|----------|---|--|--|--|--|--|--|--|--|

| Access | Bit  | 7 | 7 6 5 4 3 2 1 0 |   |          |          |   |  |  |  |  |  |  |  |  |

| R      | Name |   |                 |   |          |          |   |  |  |  |  |  |  |  |  |

### 9.2.7 Multipliers 0x06H

|   |         |             |             |              |   | CH0 Mu             | Itipliers |           |              |     |

|---|---------|-------------|-------------|--------------|---|--------------------|-----------|-----------|--------------|-----|

|   | Access  | Bit         | 7           | 6            | 5 | 4                  | 3         | 2         | 1            | 0   |

|   | R/W     | Name        | <u>Base</u> | <u>Value</u> |   | sitivity<br>pliers | С         | ompensati | on Multiplie | ers |

| В | it 7:6: | 00 = 200 (d | lefault)    |              |   |                    |           |           |              |     |

|   |         | 01 = 75     |             |              |   |                    |           |           |              |     |

|   |         | 10 = 100    |             |              |   |                    |           |           |              |     |

|   |         | 11 = 150    |             |              |   |                    |           |           |              |     |

|        |      |      |                 |  | CH n Mı            | ultipliers |            |              |     |  |  |  |  |  |

|--------|------|------|-----------------|--|--------------------|------------|------------|--------------|-----|--|--|--|--|--|

| Access | Bit  | 7    | 7 6 5 4 3 2 1 0 |  |                    |            |            |              |     |  |  |  |  |  |

| R/W    | Name | Base | Value           |  | sitivity<br>pliers | С          | ompensatio | on Multiplie | ers |  |  |  |  |  |

### 9.2.8 Compensation 0x07H

|        |      |                             |               | СН | ) Compen | sation va | alue |  |  |  |  |  |  |  |  |

|--------|------|-----------------------------|---------------|----|----------|-----------|------|--|--|--|--|--|--|--|--|

| Access | Bit  | 7                           | 7 6 5 4 3 2 1 |    |          |           |      |  |  |  |  |  |  |  |  |

| R/W    | Name | Name Channel 0 Compensation |               |    |          |           |      |  |  |  |  |  |  |  |  |

| Byte 0 |      |                             |               |    |          |           |      |  |  |  |  |  |  |  |  |

|        |      |   |                 | CH     | n Comper    | nsation V | alue   |  |  |  |  |  |  |  |  |

|--------|------|---|-----------------|--------|-------------|-----------|--------|--|--|--|--|--|--|--|--|

| Access | Bit  | 7 | 7 6 5 4 3 2 1 0 |        |             |           |        |  |  |  |  |  |  |  |  |

| R/W    | Name |   |                 | Last a | ctive chann | el Comper | sation |  |  |  |  |  |  |  |  |

| Byte n |      |   |                 |        |             |           |        |  |  |  |  |  |  |  |  |

# 9.2.9 ProxSettings 0x08H

|          |         |                |                              | F              | ProxSettir                | ngs0          |                           |             |             |

|----------|---------|----------------|------------------------------|----------------|---------------------------|---------------|---------------------------|-------------|-------------|

| Access   | Bit     | 7              | 6                            | 5              | 4                         | 3             | 2                         | 1           | 0           |

| R/W      | Name    | <u>ATI OFF</u> | <u>Partial</u><br><u>ATI</u> | <u>ALT ATI</u> | <u>Redo</u><br><u>ATI</u> | <u>Reseed</u> | <u>C</u> s<br><u>Size</u> | <u>Proj</u> | <u>Bias</u> |

| Byte 0   | Default |                |                              |                | 0x06H                     |               |                           |             |             |

| Bit 1:0: | 00 =    | 2.5µA          |                              |                |                           |               |                           |             |             |

|          | 01 =    | 5μΑ            |                              |                |                           |               |                           |             |             |

|          | 10 =    | 10µA (defau    | ılt)                         |                |                           |               |                           |             |             |

|          | 11 =    | 20µA           |                              |                |                           |               |                           |             |             |

| Bit 2:   | 0 = 5   | Small          |                              |                |                           |               |                           |             |             |

|          | 1 = L   | arge           |                              |                |                           |               |                           |             |             |

|        |         |   |                      |                             | ProxSetting           | gs1 |                      |              |             |

|--------|---------|---|----------------------|-----------------------------|-----------------------|-----|----------------------|--------------|-------------|

| Access | Bit     | 7 | 6                    | 5                           | 4                     | 3   | 2                    | 1            | 0           |

| R/W    | Name    |   | ge Transfer<br>Speed | <u>Turbo</u><br><u>Mode</u> | <u>Halt</u><br>Charge | ~   | <u>CH0</u><br>on 1Tx | <u>Error</u> | <u>Band</u> |

| Byte 1 | Default |   |                      |                             | 0x00H                 |     |                      |              |             |

| (  | <b>り</b>   |    |                    |                  |       |      | Pre                  |                  |      | itch <sup>®</sup><br>e <sup>®</sup> Series | 5    |                   | Ć             |                   | ZC         | )t               | e          |

|----|------------|----|--------------------|------------------|-------|------|----------------------|------------------|------|--------------------------------------------|------|-------------------|---------------|-------------------|------------|------------------|------------|

| Bi | t 7:6:     | 0  | 0 = 1N             | ИНz              |       |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            | 0  | 1 = 50             | 0kHz             | Z     |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            | 1  | 0 = 25             | 0kHz             | Z     |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            | 1  | 1 = 2N             | /Hz              |       |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

| Bi | t 2:       | 0  | = All <sup>-</sup> | TX fo            | or Cł | H0   |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            | 1  | = Onl              | y Tx(            | )     |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

| Bi | t 0:       | 0  | = 1/4              |                  |       |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            | 1  | = 1/8              |                  |       |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            |    |                    |                  |       |      |                      | 1                |      | Pro                                        | xSe  | ttings2           |               | 1                 |            |                  |            |

| Ac | cess       | E  | Bit                | 7                | ,     | (    | 6                    | 5                |      | 4                                          |      | 3                 |               | 2                 |            | 1                | 0          |

| F  | <b>₹/₩</b> | Na | ame                | <u>So</u><br>Res |       |      | DT<br>ff             | <u>For</u><br>Ha |      | <u>ACF</u><br>Disable                      |      | <u>Timeout D</u>  | <u>isable</u> | <u>Event M</u>    | <u>ode</u> | H                | <u>alt</u> |

| By | /te 2      | De | fault              |                  |       |      |                      |                  |      |                                            | 0x0  | )0H               |               |                   |            |                  |            |

| Bi | t 1:0:     | 0  | 0 = F              | Halt             | peri  | od ( | Set i                | in Re            | aist | er 0x0A)                                   |      |                   |               |                   |            |                  |            |

|    |            |    |                    |                  |       | -    |                      |                  | -    | er 0x0A)                                   |      |                   |               |                   |            |                  |            |

|    |            |    | <br>0 = Ne         | -                | •     | ``   |                      |                  | 0    | ,                                          |      |                   |               |                   |            |                  |            |

|    |            | 1  | 1 = Alv            | ways             |       |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            |    |                    |                  |       |      |                      |                  |      | Pro                                        | xSe  | ttings3           |               |                   |            |                  |            |

|    | Access     |    | Bi                 | t                | 7     | 6    | 5                    | 4                |      | 3                                          |      | 2                 |               | 1                 |            | 0                |            |

|    | R/W        |    | Nan                | ne               |       | _    | <u>Wheo</u><br>solut |                  | M    | <u>/heel Filte/<br/>Disable</u>            | r    | Wheel2<br>Disable |               | Wheel1<br>Disable |            | <u>CK</u><br>set | -          |

|    | Byte 3     |    | Defa               | ult              |       | 1    |                      |                  |      |                                            | 0x0  | )0H               |               |                   |            |                  |            |

| Bi | t 6:4:     | 0  | 00 = 1             | 1-bit            |       |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            |    | 11 = 4             |                  |       |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            | •  |                    | <b>N</b> IC      |       |      |                      |                  |      |                                            |      |                   |               |                   |            |                  |            |

|    |            |    |                    |                  |       |      |                      |                  |      | Pro                                        | xSe  | ttings4           |               |                   |            |                  |            |

|    | Access     |    | Bi                 | it               | 7     |      | 6                    | 5                | ;    | 4                                          |      | 3                 | 2             | 1                 | C          | )                |            |

|    | R/W        |    | Nar                | ne               |       |      |                      | U                | р    | 1                                          | U    | p Enable          |               | Pass              |            |                  |            |

|    | Byte 4     |    | Defa               | ault             |       |      |                      |                  |      |                                            | 0x0  | )7H               |               |                   |            |                  |            |

|    | -,         |    | 2010               |                  |       |      |                      |                  |      |                                            | 0.00 |                   |               |                   |            |                  |            |

|        |         |   |                 |  | ProxSe      | ttings5 |  |  |  |  |  |  |  |  |

|--------|---------|---|-----------------|--|-------------|---------|--|--|--|--|--|--|--|--|

| Access | Bit     | 7 | 7 6 5 4 3 2 1 0 |  |             |         |  |  |  |  |  |  |  |  |

| R/W    | Name    |   |                 |  | <u>CTRX</u> | VSS     |  |  |  |  |  |  |  |  |

| Byte 5 | Default |   | 0x7FH           |  |             |         |  |  |  |  |  |  |  |  |

### 9.2.10 Thresholds 0x09

|        |         |   |                 |  | Proximity | Threshold | l |  |  |  |  |  |  |  |

|--------|---------|---|-----------------|--|-----------|-----------|---|--|--|--|--|--|--|--|

| Access | Bit     | 7 | 7 6 5 4 3 2 1 0 |  |           |           |   |  |  |  |  |  |  |  |

| R/W    | Name    |   |                 |  | Val       | lue       |   |  |  |  |  |  |  |  |

| Byte 0 | Default |   | 0x04H           |  |           |           |   |  |  |  |  |  |  |  |

|        |         |   |                 | ٦ | Fouch Thre | eshold CH | 1 |  |  |  |  |

|--------|---------|---|-----------------|---|------------|-----------|---|--|--|--|--|

| Access | Bit     | 7 | 7 6 5 4 3 2 1 0 |   |            |           |   |  |  |  |  |

| R/W    | Name    |   |                 |   | (Value/2   | 256)*LTA  |   |  |  |  |  |

| Byte 1 | Default |   | 0x10H           |   |            |           |   |  |  |  |  |

|        |         |   |                                                                         | ٦ | Fouch Thre | eshold CH | 9 |  |  |  |  |

|--------|---------|---|-------------------------------------------------------------------------|---|------------|-----------|---|--|--|--|--|

| Access | Bit     | 7 | 7         6         5         4         3         2         1         0 |   |            |           |   |  |  |  |  |

| R/W    | Name    |   | (Value/256)*LTA                                                         |   |            |           |   |  |  |  |  |

| Byte 9 | Default |   | 0x10H                                                                   |   |            |           |   |  |  |  |  |

# 9.2.11 Timings 0x0AH

|        |         |   |                 | I | Filter Halt | (t_HALT) | ) |  |  |  |  |

|--------|---------|---|-----------------|---|-------------|----------|---|--|--|--|--|

| Access | Bit     | 7 | 7 6 5 4 3 2 1 0 |   |             |          |   |  |  |  |  |

| R/W    | Name    |   |                 |   | Steps of    | f 250ms  |   |  |  |  |  |

| Byte 0 | Default |   | 0x50H           |   |             |          |   |  |  |  |  |

|        |         |   |                 |  | Power M | ode (LP) |  |  |  |  |  |

|--------|---------|---|-----------------|--|---------|----------|--|--|--|--|--|

| Access | Bit     | 7 | 7 6 5 4 3 2 1 0 |  |         |          |  |  |  |  |  |

| R/W    | Name    |   |                 |  | Steps c | of 16ms  |  |  |  |  |  |

| Byte 1 | Default |   |                 |  | OxC     | ЮН       |  |  |  |  |  |

|        |         |   |                 |       | Timeou | t Period |   |   |   |  |  |

|--------|---------|---|-----------------|-------|--------|----------|---|---|---|--|--|