# Si5332 Data Sheet

# 6/8/12-Output Any-Frequency Clock Generator

Based on Silicon Labs proprietary MultiSynth<sup>™</sup> flexible frequency synthesis technology, the Si5332 generates any combination of output frequencies with excellent jitter performance (230 fs rms). The device's highly flexible architecture enables a single device to generate a wide range of integer and non-integer related frequencies on up to 12 differential clock outputs with 0 ppm frequency synthesis error. The device offers multiple banks of outputs that can each be tied to independent voltages, enabling usage in mixed-supply applications. Further, the signal format of each clock output is user-configurable. Given its frequency, format, and supply voltage flexibility, the Si5332 is ideally suited to replace multiple clock ICs and oscillators with a single device.

The Si5332 is quickly and easily configured using ClockBuilder Pro<sup>™</sup> software. Clock-Builder Pro assigns a custom part number for each unique configuration. Devices ordered with custom part numbers are factory-programmed free of charge, making it easy to get a custom clock uniquely tailored for each application. Si5332 can also be programmed via an I2C serial interface.

### Applications:

- Servers, Storage, Search Acceleration

- Ethernet Switches, Routers

- Small Cells, Mobile Backhaul/Fronthaul

- Print Imaging

- Communications

- Broadcast Video

- Test and Measurement

- Industrial, Embedded Computing

#### KEY FEATURES

- Any-Frequency 6/8/12-output

programmable clock generators

- Offered in three different package sizes, supporting different combinations of output clocks and user configurable hardware input pins

- 32-pin QFN, up to 6 outputs

- 40-pin QFN, up to 8 outputs

- 48-pin QFN, up to 12 outputs

- MultiSynth technology enables anyfrequency synthesis on any output up to 250 MHz

- Highly configurable output path featuring a cross point mux

- Up to three independent fractional synthesis output paths

- · Up to five independent integer dividers

- Embedded 50 MHz crystal option

- Input frequency range:

- External crystal: 16 to 50 MHz

- Differential clock: 10 to 250 MHz

- · LVCMOS clock: 10 to 170 MHz

- Output frequency range:

- Differential: 5 to 312.5 MHz

- LVCMOS: 5 to 170 MHz

- User-configurable clock output signal format per output: LVDS, LVPECL, HCSL, LVCMOS

- Temperature range: -40 to +85 °C

- · Down and center spread spectrum

- · Pb-free, RoHS-6 compliant

- Si5332 Family Reference Manual

# **Table of Contents**

| 1. | Features List                                                                                                                                                                                                                                             | . 4                                                                                            |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 2. | Ordering Guide                                                                                                                                                                                                                                            | . 5                                                                                            |

| 3. | Functional Description.                                                                                                                                                                                                                                   | . 6                                                                                            |

|    | 3.1 Functional Block Diagrams                                                                                                                                                                                                                             | . 7                                                                                            |

|    | 3.2 Modes of Operation                                                                                                                                                                                                                                    |                                                                                                |

|    | 3.3 Frequency Configuration                                                                                                                                                                                                                               |                                                                                                |

|    | 3.4 Inputs                                                                                                                                                                                                                                                | .10<br>.10                                                                                     |

|    | 3.5 Outputs                                                                                                                                                                                                                                               | .11<br>.12<br>.16<br>.16<br>.16<br>.16<br>.16<br>.16<br>.16<br>.17<br>.17<br>.17<br>.18<br>.19 |

| ٨  |                                                                                                                                                                                                                                                           |                                                                                                |

|    | Register Map                                                                                                                                                                                                                                              |                                                                                                |

| 6. | Pin Descriptions                                                                                                                                                                                                                                          | .35<br>.40                                                                                     |

| 7. | Package Outline                                                                                                                                                                                                                                           | 48                                                                                             |

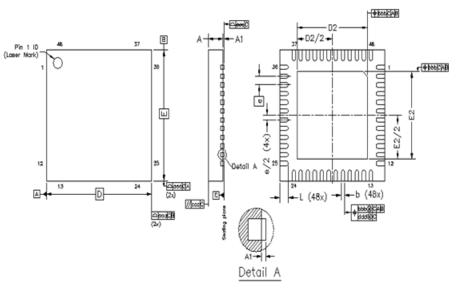

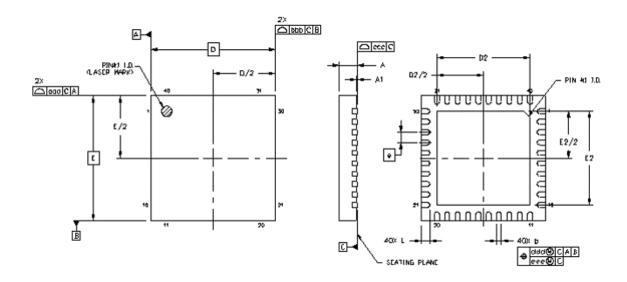

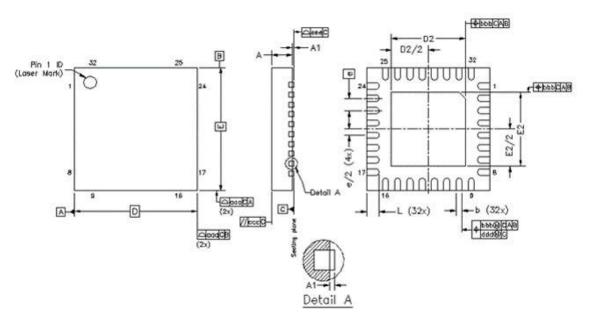

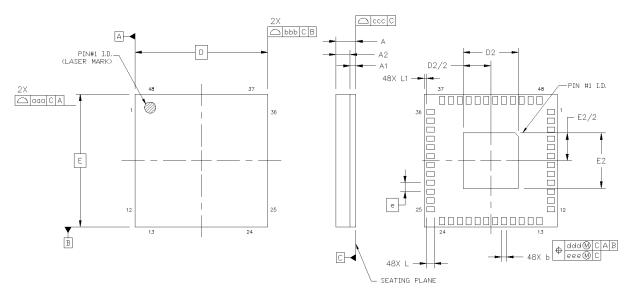

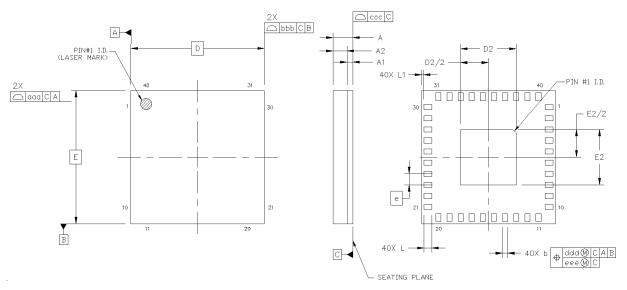

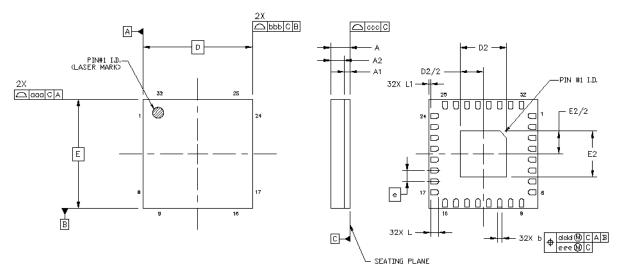

|    | 7.1 Si5332 6x6 mm 48-QFN Package Diagram, External Crystal Versions (Si5332A/B/C/D)7.2 Si5332 6x6 mm 40-QFN Package Diagram, External Crystal Versions (Si5332A/B/C/D)7.3 Si5332 5x5 mm 32-QFN Package Diagram, External Crystal Versions (Si5332A/B/C/D) | .49                                                                                            |

|    | 7.4 Si5332 6x6 mm 48-QFN Package Diagram, Embedded Crystal Versions (Si5332E/F/G/H)                                                                                                                                                                       | .51                                                                                            |

|     | 7.5  | Si5332   | 6x6 mr  | n 40-C | (FN  | Packa  | age | Dia | agr | am | , E | mb | edo | ded | Cr   | ryst | al ' | Ver | sio | ns | (Si | 53 | 32E | E/F | /G/ | Ή)  |   |   |   | .52  |

|-----|------|----------|---------|--------|------|--------|-----|-----|-----|----|-----|----|-----|-----|------|------|------|-----|-----|----|-----|----|-----|-----|-----|-----|---|---|---|------|

|     | 7.6  | Si5332   | 5x5 mr  | n 32-C | (FN  | Packa  | age | Dia | agr | am | , E | mb | edo | ded | l Cr | ryst | al ' | Ver | sio | ns | (Si | 53 | 32E | E/F | /G/ | ′H) |   |   |   | .53  |

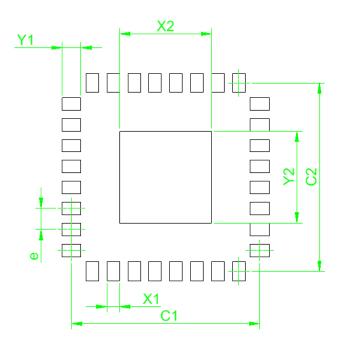

| 8.  | РСВ  | Land I   | Pattern |        | •    |        |     |     |     | •  | •   | •  |     |     | •    |      | •    | •   | •   | •  | •   | •  | •   | •   | •   |     |   |   |   | .54  |

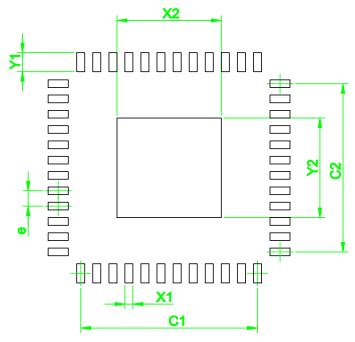

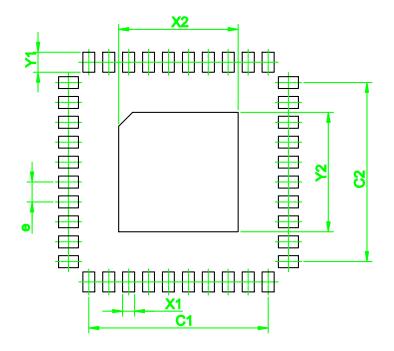

|     | 8.1  | Si5332   | 48-QFI  | V Lanc | l Pa | ttern. |     |     |     |    |     |    |     |     |      |      |      |     |     |    |     |    |     |     |     |     |   |   |   | .54  |

|     | 8.2  | Si5332   | 40-QFI  | V Lanc | l Pa | ttern. |     | •   |     |    |     |    |     |     |      | •    |      |     |     |    |     |    |     |     | •   |     |   |   |   | .55  |

|     | 8.3  | Si5332   | 32-QFI  | V Lanc | l Pa | ttern. |     |     |     |    |     |    |     |     |      |      |      |     |     |    |     |    |     | •   | •   |     |   |   |   | .56  |

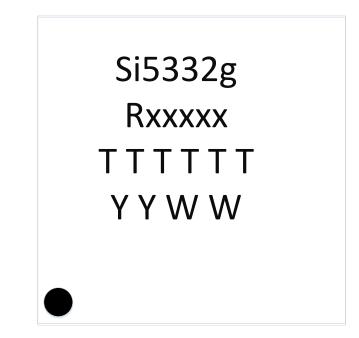

| 9.  | Тор  | Markin   | g       |        |      |        | •   |     | •   |    |     |    |     | •   |      |      | •    | •   | •   |    |     | •  |     |     | •   | •   | • | • | • | 57   |

| 10. | Do   | cument   | t Chang | ge Lis | t    |        |     |     | -   |    |     |    |     |     | -    | •    |      |     |     |    | •   |    |     | -   |     |     | • | • | • | . 58 |

|     | 10.1 | l Revisi | ion 0.7 |        |      |        |     |     |     |    |     |    |     |     |      |      |      |     |     |    |     |    |     |     |     |     |   |   |   | .58  |

# 1. Features List

- Any-Frequency 6/8/12-output programmable clock generators

- Offered in three different package sizes, supporting different combinations of output clocks and user configurable hardware input pins

- 32-pin QFN, up to 6 outputs

- 40-pin QFN, up to 8 outputs

- 48-pin QFN, up to 12 outputs

- MultiSynth<sup>™</sup> technology enables any-frequency synthesis on any output up to 250 MHz

- Embedded 50 MHz crystal option

- Highly configurable output path featuring a cross point mux

- Up to three independent fractional synthesis output paths

- Up to five independent integer dividers

- Ordering options for embedded 50 MHz reference crystal

- Input frequency range:

- External crystal: 16 to 50 MHz

- Differential clock: 10 to 250 MHz

- LVCMOS clock: 10 to 170 MHz

- Output frequency range:

- Differential: 5 to 312.5 MHz

- LVCMOS: 5 to 170 MHz

- Embedded crystal option on 8-output and 12-output devices.

- User-configurable clock output signal format per output: LVDS, LVPECL, HCSL, LVCMOS

- Low phase jitter: 230 fs rms

- PCIe Gen1/2/3/4, SRIS compliant

- 1.8 V, 2.5 V, 3.3 V core VDD

- · Adjustable output-output delay

- · Independent glitchless on-the-fly output frequency changes

- Very low power consumption

- Independent output supply pins for each bank of outputs:

- 1.8 V, 2.5 V, or 3.3 V differential

- 1.5 V, 1.8 V, 2.5 V, 3.3 V LVCMOS

- Programmable spread spectrum

- Down and center spread from –0.1% –2.5% in 0.01% steps at 30 to 33 KHz

- Integrated power supply filtering

- Serial interface: I<sup>2</sup>C

- ClockBuilder Pro software utility simplifies device configuration and assigns custom part numbers

- Temperature range: –40 to +85 °C

- Pb-free, RoHS-6 compliant

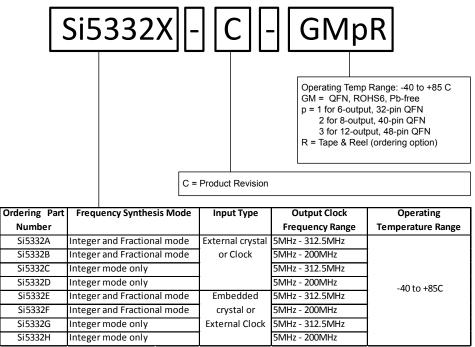

# 2. Ordering Guide

# Blank devices, in-system programmable

Note: Si5332E/F/G/H in development, contact Silicon Labs for further information.

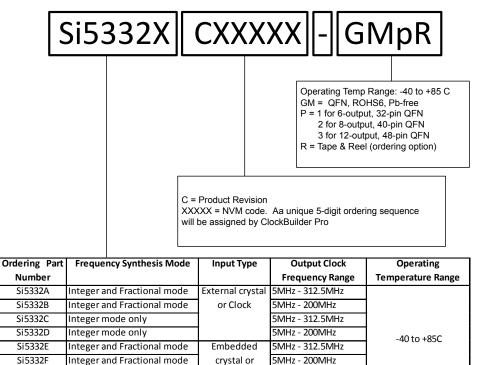

# Pre-programmed devices using a ClockBuilder Pro configuration file

Note: Si5332E/F/G/H in development, contact Silicon Labs for further information.

Integer mode only

Integer mode only

Figure 2.1. Orderable Part Number Guide

External Clock

5MHz - 312.5MHz

5MHz - 200MHz

Si5332G

Si5332H

# 3. Functional Description

The Si5332 is a high-performance, low-jitter clock generator capable of synthesizing up to twelve user-programmable clock frequencies up to 312.5 MHz. The device supports free run operation using an external or embedded crystal, or it can lock to an external clock signal. The output drivers support up to twelve differential clocks or twenty four LVCMOS clocks, or a combination of both. The output drivers are configurable to support common signal formats, such as LVPECL, LVDS, HCSL, and LVCMOS. VDDO pins are provided for versatility, which can be set to 3.3 V, 2.5 V, 1.8 V or 1.5 V (CMOS only) to power the multi-format output drivers. The core voltage supply (VDD) accepts 3.3 V, 2.5 V, or 1.8 V and is independent from the output supplies (VDDOxs). Using its two-stage synthesis architecture and patented high-resolution low-jitter MultiSynth technology, the Si5332 can generate an entire clock tree from a single device.

The Si5332 combines a wideband PLL with next generation MultiSynth technology to offer the industry's highest output count high performance programmable clock generator, while maintaining a jitter performance of 230 fs RMS. The PLL locks to either an external 16-50 MHz crystal or an embedded 50 MHz crystal for generating for generating free-running clocks or to an external clock (CLKIN\_2/ CLKIN\_2# or CLKIN\_3/CLKIN\_3#) for generating synchronous clocks. In free-run mode, the oscillator frequency is multiplied by the PLL and then divided down either by an integer divider or MultiSynth for fractional synthesis.

The Si5332 features user-defined universal hardware input pins which can be configured in the ClockBuilder Pro software utility. Universal hardware pins can be used for OE, spread spectrum enable, input clock selection, output frequency selection, or I2C address select. If additional hardware input pins are needed, a user can define a different clock output as universal hardware input pins instead using ClockBuilder Pro.

The device provides the option of storing a user-defined clock configuration in its non-volatile memory (NVM), which becomes the default clock configuration at power-up. To enable in-system programming, a power up mode is available through OTP which powers up the chip in an OTP defined default mode but with no outputs enabled. This allows a host processor to first write a user defined subset of the registers and then restart the power-up sequence to activate the newly programmed configuration without re-downloading the OTP.

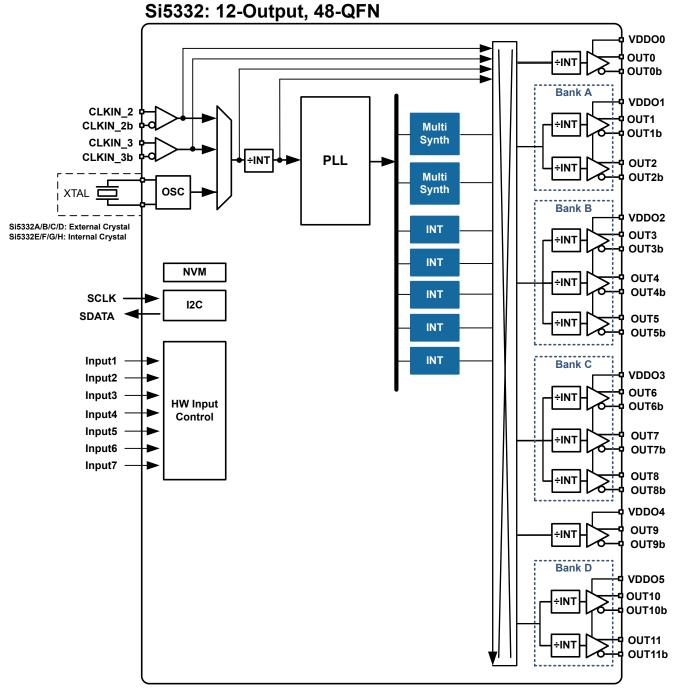

Figure 3.1. Block Diagram for 12-Output Si5332 in 48-QFN

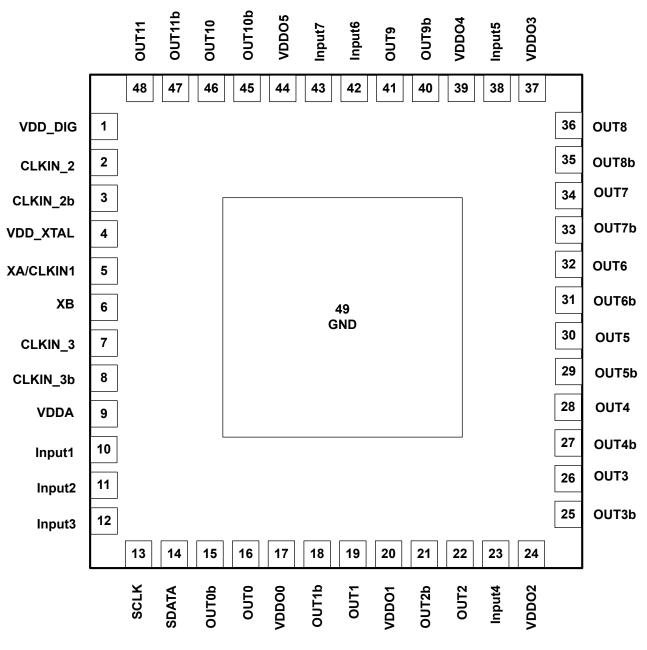

The Si5332 48-QFN features:

- · Up to twelve differential clock outputs, with six VDDO pins.

- · Seven user-configurable HW input pins, defined using ClockBuilder Pro.

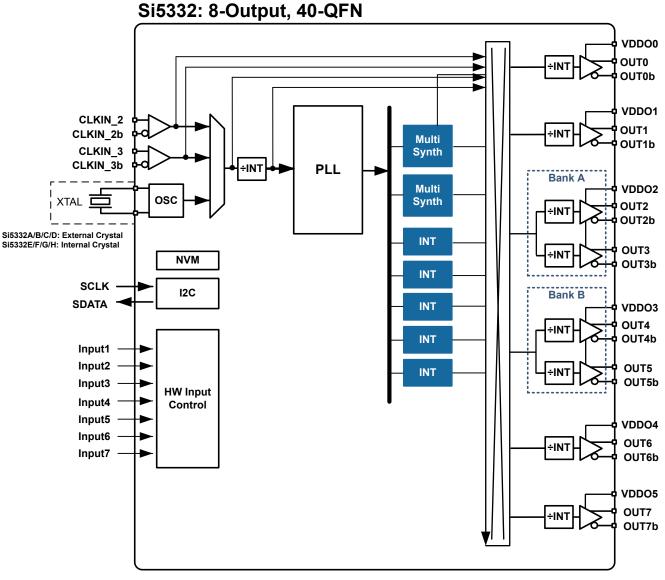

Figure 3.2. Block Diagram for 8-Output Si5332 in 40-QFN

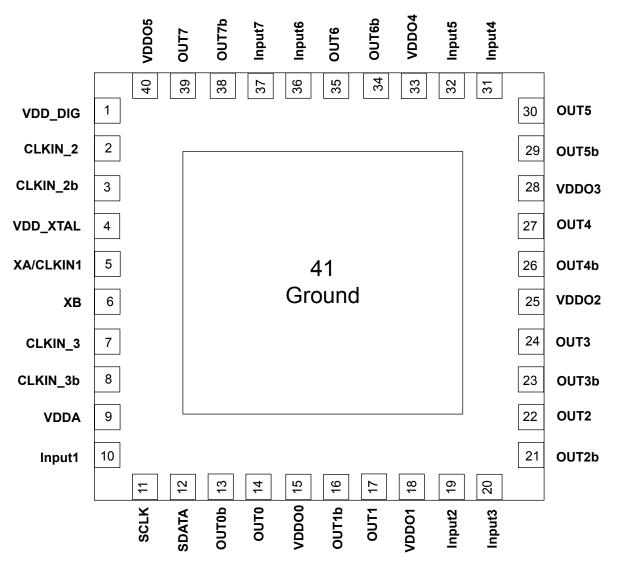

The Si5332 40-QFN features:

- · Up to eight differential clock outputs, with six VDDO pins.

- · Seven user-configurable HW input pins, defined using ClockBuilder Pro.

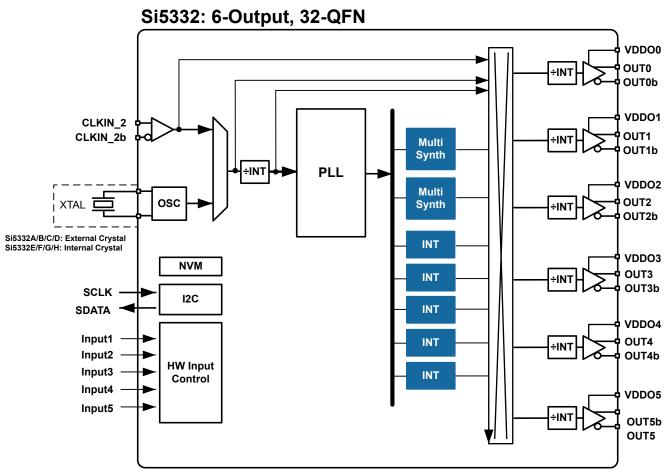

Figure 3.3. Block Diagram for 6-Output Si5332 in 32-QFN

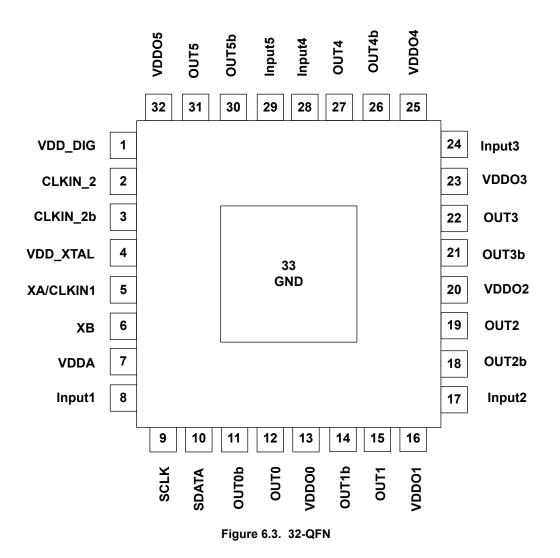

The Si5332 32-QFN features:

- · Up to six differential clock outputs with individual VDDO.

- · Five user-configurable HW input pins, defined using ClockBuilder Pro.

### 3.2 Modes of Operation

The Si5332 supports both free-run and synchronous modes of operation. The default mode selection is set in ClockBuilder Pro. Alternatively, a universal hardware input pin can be defined as CLKIN\_SEL to select between a crystal or clock input. There is also the option to select the input source via the serial interface by writing to the input select register.

#### 3.2.1 Initialization

Once power is applied, the device begins an initialization period where it downloads default register values and configuration data from NVM and performs other initialization tasks. Communicating with the device through the serial interface is possible once this initialization period is complete. The clock outputs will be squelched until the device initialization is done.

#### 3.3 Frequency Configuration

The phase-locked loop is fully integrated and does not require external loop filter components. Its function is to phase lock to the selected input and provide a common synchronous reference to the high-performance MultiSynth fractional or integer dividers.

A cross point mux connects any of the MultiSynth divided frequencies or INT divided frequencies to individual output drivers or banks of output drivers. Additional output integer dividers provide further frequency division by an even integer from 1 to 63. The frequency configuration of the device is programmed by setting the input dividers (P), the PLL feedback fractional divider (Mn/Md), the MultiSynth fractional dividers (Nn/Nd), and the output integer dividers (R). Silicon Labs' Clockbuilder Pro configuration utility determines the optimum divider values for any desired input and output frequency plan

#### 3.4 Inputs

The Si5332 requires an external 16–30 MHz crystal at its XIN/XOUT pins or the embedded 50 MHz crystal to operate in free-run mode, or an external input clock (CLKIN\_2/CLKIN\_2# or CLKIN\_3/CLKIN\_3#) for synchronous operation. An external crystal is not required in synchronous mode.

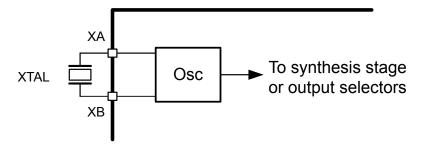

#### 3.4.1 External Reference Input (XA/XB)

An external crystal (XTAL) is used in combination with the internal oscillator (OSC) on Si5332A/B/C/D to produce a low jitter reference for the PLL when operating in the free-run mode. Frequency offsets due to  $C_L$  mismatch can be adjusted using the frequency adjustment feature which allows frequency adjustments of ±1000 ppm. The Si5332 Reference Manual provides additional information on PCB layout recommendations for the crystal to ensure optimum jitter performance. Refer to Table 5.4 External Crystal Input Specification on page 24 for crystal specifications.

For free-running operation, the internal oscillator can operate from a low-frequency fundamental mode crystal (XTAL) with a resonant frequency of 16 to 50 MHz. A crystal can easily be connected to pins XA and XB without external components, as shown in the figure below. A register bit will allow the device to use an internal loading capacitor (CL) with a typical value of 12 pF or bypass the internal CL and use external CL. Alternatively, an external CL can be used along with the internal CL.

Figure 3.4. External Reference Input (XA/XB)

The Si5332E/F/G/H options feature an embedded 50 MHz reference crystal that is used in the free run mode.

#### 3.4.2 Input Clocks

An input clock is available to synchronize the PLL when operating in synchronous mode. This input can be configured as LVPECL, LVDS or HCSL differential, or LVCMOS. The recommended input termination schemes are shown in the Si5332 Family Reference Manual. Differential signals must be AC coupled. The single-ended LVCMOS input is internally AC coupled, and only needs to meet a minimum voltage swing that may not exceed a maximum VIH or minimum VIL. Unused inputs can be disabled by register configuration.

#### 3.4.3 Input Selection

The active clock input is selected by register control, or by defining a universal hardware input pin as CLKIN\_SEL in ClockBuilder Pro. A register bit determines input selection as pin or register selectable. If a universal input pin is defined as CLKIN\_SEL, that pin is selected by default and is internally pulled high so that the free-run mode is automatically selected when left unconnected. If there is no clock signal on the selected input, the device will not generate output clocks.

In a typical application, the Si5332 reference input is configured immediately after power-up and initialization. If the device is switched to another input more than ±1000 ppm offset from the initial input, the device must be recalibrated manually to the new frequency, temporarily turning off the clock outputs. After the VCO is recalibrated, the device will resume producing clock outputs. If the selected inputs are within ±1000 ppm, any phase error difference will propagate through the device at a rate determined by the PLL bandwidth. Hitless switching and phase build-out are not supported by the Si5332.

#### 3.5 Outputs

The Si5332 supports up to 12 differential output drivers. Each output can be independently configured as a differential pair or as dual LVCMOS outputs. The 8-output and 12-output devices feature banks of outputs, with each bank sharing a common VDDO.

#### Table 3.1. Clock Outputs

| Package | Maximum Outputs            |

|---------|----------------------------|

| 32-QFN  | 6 Differential, 12 LVCMOS  |

| 40-QFN  | 8 Differential, 16 LVCMOS  |

| 48-QFN  | 12 Differential, 24 LVCMOS |

The output stage is different for each of the three versions of Si5332.

- The 6-output device features individual VDDO pins for each clock output. Each clock output can be sourced from MultiSynth0, Multi-Synth1, the input reference clock, or one of the five INT dividers through the cross point MUX.

- The 8-output device includes four clock outputs with dedicated VDDO pins, each of which can be sourced from MultiSynth0, Multi-Synth1, the input reference clock, or one of the five INT dividers through the cross point MUX. The remaining four clock outputs are divided into Bank A and Bank B. Each Bank of outputs can be sourced from MultiSynth0, MultiSynth1, the input reference clock, or one of the five INT dividers through the cross point MUX. The outputs in each of the two Banks share a common VDDO pin.

- The 12-output device includes two clock outputs with dedicated VDDO pins, each of which can be sourced from MultiSynth0, Multi-Synth1, the input reference clock, or one of the five INT dividers through the cross point MUX. The remaining ten clock outputs are divided into Bank A, Bank B, Bank C, and Bank D. Each Bank of outputs can be sourced from MultiSynth0, MultiSynth1, the input reference clock, or one of the five INT dividers through the cross point MUX. The outputs in each of the four Banks share a common VDDO pin.

Utilizing the reference clock enables a fan-out buffer function from an input clock source to any bank of outputs.

Individual output Integer output dividers (R) allow the generation of additional synchronous frequencies. These integer dividers are configurable as divide by 1 (default) through 63.

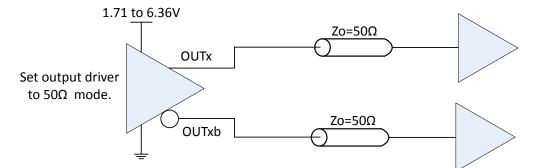

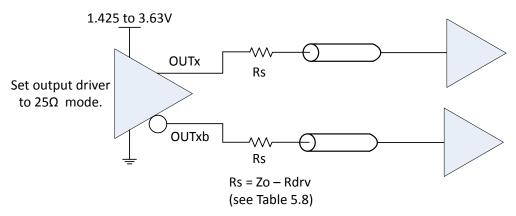

#### 3.5.1 Output Signal Format

The differential output swing and common mode voltage are both fully programmable and compatible with a wide variety of signal formats including HCSL, LVDS and LVPECL. In addition to supporting differential signals, any of the outputs can be configured as LVCMOS drivers, enabling the device to support both differential and single-ended clock outputs. Output formats can be defined in ClockBuilder Pro or via the serial interface.

#### 3.5.2 Differential Output Terminations

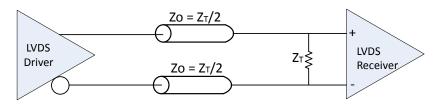

#### **LVDS Driver Termination**

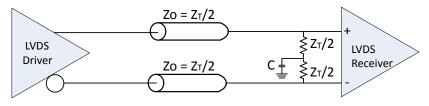

For a general LVDS interface, the recommended value for the termination impedance ( $Z_T$ ) is between 90  $\Omega$  and 132  $\Omega$ . The actual value should be selected to match the differential impedance (Z0) of the transmission line. A typical point-to-point LVDS design uses a 100  $\Omega$  parallel resistor at the receiver and a 100  $\Omega$  differential transmission-line environment. In order to avoid any transmission-line reflection issues, the components should be surface mounted and must be placed as close to the receiver as possible. The standard LVDS termination schematic as shown in Figure 3.5 Standard LVDS Termination on page 12 can be used with either type of output structure. Figure 3.6 Optional LVDS Termination on page 12, which can also be used with both output types, is an optional termination with center tap capacitance to help filter common mode noise. The capacitor value should be approximately 50 pF. If using a non-standard termination, please contact Silicon Labs to confirm if the output structure is current source or voltage source type. In addition, since these outputs are LVDS compatible, the input receiver's amplitude and common-mode input range should be verified for compatibility with the output.

Figure 3.5. Standard LVDS Termination

Figure 3.6. Optional LVDS Termination

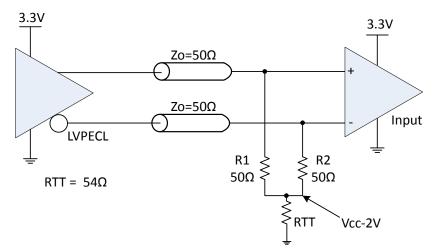

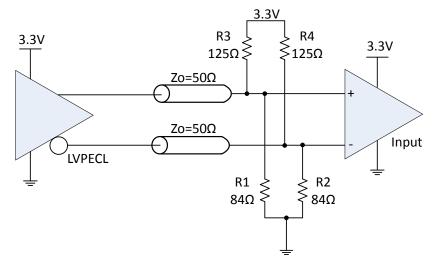

#### **Termination for 3.3 V LVPECL Outputs**

The clock layout topology shown below is a typical termination for LVPECL outputs. The two different layouts mentioned are recommended only as guidelines. The differential outputs generate ECL/LVPECL compatible outputs. Therefore, terminating resistors (DC current path to ground) or current sources must be used for functionality. These outputs are designed to drive 50  $\Omega$  transmission lines. Matched impedance techniques should be used to maximize operating frequency and minimize signal distortion. Figure 3.7 3.3 V LVPECL Output Termination, Option 1 on page 13 and Figure 3.8 3.3 V LVPECL Output Termination, Option 2 on page 13 show two different layouts. Other suitable clock layouts may exist, and it would be recommended that the board designers simulate to guarantee compatibility across all printed circuit and clock component process variations.

Figure 3.7. 3.3 V LVPECL Output Termination, Option 1

Figure 3.8. 3.3 V LVPECL Output Termination, Option 2

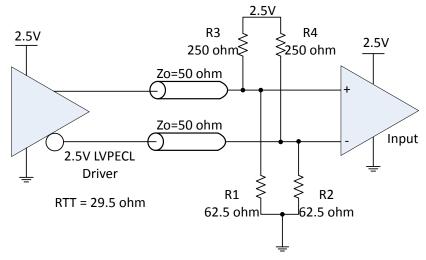

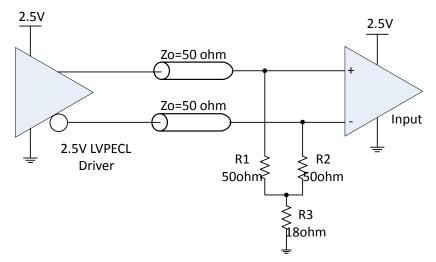

#### Termination for 2.5 V LVPECL Outputs

Figure 3.9 2.5 V LVPECL Termination Example, Option 1 on page 14 and Figure 3.10 2.5 V LVPECL Termination Example, Option 2 on page 14 show examples of termination for the 2.5 V LVPECL driver option. These terminations are equivalent to terminating 50  $\Omega$  to VDDO – 2 V. For VDDO = 2.5 V, the VDDO – 2 V is very close to ground level. The R3 in Figure 3.10 2.5 V LVPECL Termination Example, Option 2 on page 14 can be optionally eliminated using the termination shown in Figure 3.9 2.5 V LVPECL Termination Example, Option 1 on page 14.

Figure 3.9. 2.5 V LVPECL Termination Example, Option 1

Figure 3.10. 2.5 V LVPECL Termination Example, Option 2

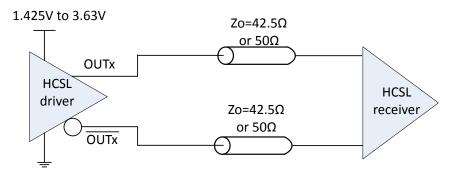

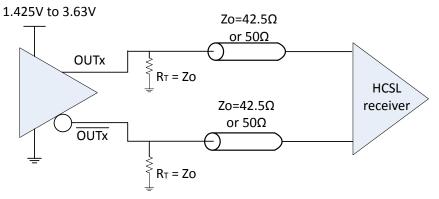

#### **Termination for HCSL Outputs**

The Si5332 HCSL driver option integrated termination resistors to simplify interfacing to an HCSL receiver. The HCSL driver supports both 100  $\Omega$  and 85  $\Omega$  transmission line options. This configuration option may be specified using ClockBuilder Pro or via the device I2C interface.

Figure 3.11. HCSL Internal Termination Mode

Figure 3.12. HCSL External Termination Mode

#### 3.5.3 LVCMOS Output Terminations

LVCMOS outputs are dc-coupled, as shown in the figure below.

Figure 3.13. LVCMOS Output Termination Example, Option 1

Figure 3.14. LVCMOS Output Termination Example, Option 2

#### 3.5.4 LVCMOS Output Signal Swing

The signal swing  $(V_{OL}/V_{OH})$  of the LVCMOS output drivers is set by the voltage on the VDDO pin for the respective bank.

#### 3.5.5 LVCMOS Output Polarity

When a driver is configured as an LVCMOS output it generates a clock signal on both pins (OUTx and OUTxb). By default, the clock on the OUTxb pin is generated in phase with the clock on the OUTx pin. The polarity of these clocks is configurable enabling complimentary clock generation and/or inverted polarity with respect to other output drivers.

#### 3.5.6 LVCMOS Output Configurable Tr/Tf

The Si5332 has four settings to choose from for LVCMOS outputs up to 66 MHz at 50  $\Omega$  internal impedance drive a 5", 50  $\Omega$  trace. This can be configured using the ClockBuilder Pro software utility, or through the I2C programming interface. Output frequencies greater than 66 MHz must use the fastest setting.

#### 3.5.7 Output Enable/Disable

The universal hardware input pins can be programmed with either active low or active high polarity, to operate as output enable (OEb), controlling one or more outputs. Pin assignment is done using ClockBuilder Pro. An output enable pin provides a convenient method of disabling or enabling the output drivers. When the output enable pin is held high all designated outputs will be disabled. When held low, the designated outputs will be enabled. Outputs in the enabled state can be individually disabled through register control.

#### 3.5.8 Differential Output Configurable Skew Settings

Skew on the differential outputs can be independently configured. The skew is adjustable in 35 ps steps across a range of 280 ps.

#### 3.5.9 Output Driver State When Disabled

The disabled state of an output driver is configurable as: disable low, disable high, or disable high-impedance.

#### 3.5.10 Synchronous Output Disable Feature

Output clocks are always enabled and disabled synchronously. The output will wait until a clock period has completed before the driver is disabled. This prevents unwanted runt pulses from occurring when disabling an output.

#### 3.6 Spread Spectrum

To help reduce electromagnetic interference (EMI), the Si5332 supports spread spectrum modulation. The output clock frequencies can be modulated to spread energy across a broader range of frequencies, lowering system EMI. The Si5332 implements spread spectrum using its patented MultiSynth technology to achieve previously unattainable precision in both modulation rate and spreading magnitude. Spread spectrum can be enabled through I2C, or by configuring one of the universal hardware input pins using ClockBuilder Pro.

The Si5332 features both center and down spread spectrum modulation capability, from 0.1% to 2.5%. Each MultiSynth is capable of generating an independent spread spectrum clock. The feature is enabled using a user-defined universal hardware input pin or via the device I2C interface. Spread spectrum can be applied to any output clock, with any clock frequency up to 250 MHz. Since the spread spectrum clock generation is performed in the MultiSynth fractional dividers, the spread spectrum waveform is highly consistent across process, voltage and temperature. The Si5332 features two independent MultiSynth dividers, enabling the device to provide two independent spread profiles simultaneously to the clock output banks.

Spread spectrum is commonly used for 100 MHz PCI Express clock outputs. To comply with the spread spectrum specifications for PCI Express, the spreading frequency should be set to a maximum of 33 kHz and –0.5% down spread. A universal hardware input pin can be configured to toggle spread spectrum on/off.

# 3.7 Universal Hardware Input Pins

Universal hardware input pins are user configurable control input pins that can have one or more of the functions listed below assigned to them using ClockBuilder Pro.

If more hardware input pins are needed, the differential input pins can be alternatively configured as two universal hardware input pins. Contact Silicon Labs for further details. Universal hardware input pins can be utilized for the following functions:

| Description        | Function                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------------------|

| Spread_EN0         | Spread spectrum enable on MultiSynth0 (N0).                                                             |

| Spread_EN1         | Spread spectrum enable on MultiSynth0 (N1).                                                             |

| FS_INTx            | Used to switch an integer output divider frequency from frequency A to frequency B.                     |

| FS_MSx             | Used to switch a MultiSynth output divider output from frequency and/or change spread spectrum profile. |

| OE                 | Output enable for one or more outputs.                                                                  |

| I2C address select | Sets the LSB of the I2C address to either 0 or 1.                                                       |

| CLKIN_SEL[1:0]     | Selects between crystal or clock inputs.                                                                |

# Table 3.2. Universal Hardware Input Pins

# MultiSynth Spread Enable Pins

Spread\_EN[1:0] pins are active pins that enable/disable spread spectrum on all outputs that correspond to MutliSynth0 or MultiSynth1, respectively. The change in frequency or spread spectrum will be instantaneous and may not be glitch free.

### Table 3.3. SPREAD\_EN Pin Selection Table

| Spread_ENx |                                         |

|------------|-----------------------------------------|

| 0          | Spread Spectrum disabled on MultiSynthx |

| 1          | Spread Spectrum enabled on MultiSynthx  |

### **Output Frequency Select Pins**

There are five integer dividers, one corresponding to each of the five output banks. Using ClockBuilder Pro, a universal hardware input pin can be assigned for each integer divider, providing capability to select between two different pre-programmed divide values. Divider values of every integer from 8 to 255 are available in ClockBuilder Pro for each integer divider.

### Table 3.4. F<sub>S INT</sub> Pin Selection Table

| F <sub>S_INTx</sub> | Output Frequency from INTx                  |

|---------------------|---------------------------------------------|

| 0                   | Frequency A, as defined in ClockBuilder Pro |

| 1                   | Frequency B, as defined in ClockBuilder Pro |

#### **Output Enable**

A universal hardware input pin can be defined to control output enable of a differential output, a bank of differential outputs, or as a global output enable pin controlling all outputs. Upon de-assertion of an OE pin, the corresponding output will be disabled within 2-6 clock cycles. Asserting an OE pin from disable to enable will take <20  $\mu$ s for the output to have a clean clock. OE pins have programmable 100 k $\Omega$  pull-up/pull-down or no pull resistors setting

The disable state is programmable as 0, 1, Hi-Z, or free running. See the Si5332 Family Reference Manual for details.

Output enabled/disabled for LVCMOS are done in pairs. Each differential buffer True and Compliment output can generate an LVCMOS clock and the OE pin associated with the True and Compliment output buffer will control the respective LVCMOS pair.

For example: If DIFF0 is configured to be SE1 and DIFF0# is configured to be SE2 and OE1 is the associated OE pin, de-asserting the OE1 pin will disable both SE1 and SE2 outputs. The disable and enable of the outputs to a known state is glitch free.

#### **I2C Address Pin**

This pin sets the LSB of the I2C address. For example, if the I2C address is A6h, setting this pin high will set the I2C address to A7h.

#### CLKIN\_SEL[0:1] Pins

These pins are used to set the input source clock between the input clock channels (Crystal, CLKIN\_2/CLKIN\_2# or CLKIN\_3/ CLKIN\_3#). Upon switching the input clock source, the output will not be glitch free. It is intended for the user to set this pin to a known state before the system is powered up or have the receiver address any unintended output signals when switching to a different input source clock. This pin has an internal 50 k $\Omega$  internal pull-up or pull-down at all times.

#### 3.8 Custom Factory Pre-programmed Parts

Custom pre-programmed parts can be ordered corresponding to a specific configuration file generated using the ClockBuilder Pro software utility. Silicon Labs writes the configuration file into the device prior to shipping. Use the ClockBuilder Pro custom part number wizard (http://www.silabs.com/clockbuilderpro) to quickly and easily generate a custom part number for your ClockBuilder Pro configuration file. A factory pre-programmed part will generate clocks at power-up.

In less than three minutes, you will be able to generate a custom part number with a detailed data sheet addendum matching your design's configuration. Once you receive the confirmation email with the data sheet addendum, simply place an order with your local Silicon Labs sales representative. Samples of your pre-programmed device will ship within two weeks.

#### 3.9 I2C Serial Interface

The Si5332 is fully compliant to rev6 of the I2C specification, including Standard, Fast, and Fast+ modes.

Configuration and operation of the Si5332 can be controlled by reading and writing registers using the I<sup>2</sup>C. Communication with a 1.8 V to 3.3 V host is supported. See the Si5332 Family Reference Manual for details.

#### 3.10 In-Circuit Programming

The Si5332 is fully configurable using the I<sup>2</sup>C serial interface. At power-up the device downloads its default register values from internal non-volatile memory (NVM). Refer to the *Si5332 Family Reference Manual* for a detailed procedure for writing registers to volatile memory.

# 4. Register Map

Refer to the Si5332 Family Reference Manual for a complete list of registers descriptions and settings.

# 5. Electrical Specifications

## Table 5.1. Recommended Operating Conditions

$(V_{DD} = V_{DDA} = 1.8 \text{ V to } 3.3 \text{ V +10\%/-5\%}, V_{DDO} = 1.8 \text{ V } \pm 5\%, 2.5 \text{ V } \pm 5\%, \text{ or } 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                    | Symbol                                                           | Test Condition | Min   | Тур | Мах  | Units |

|------------------------------|------------------------------------------------------------------|----------------|-------|-----|------|-------|

| Ambient Temperature          | T <sub>A</sub>                                                   |                | -40   | 25  | 85   | °C    |

| Junction Temperature         | TJ <sub>MAX</sub>                                                |                |       | _   | 125  | °C    |

| Core Supply Voltage          | V <sub>DDA</sub> , V <sub>DD_DIG</sub> ,<br>V <sub>DD_xtal</sub> |                | 1.71  | _   | 3.63 | V     |

| Output Driver Supply Voltage | V <sub>DDO</sub>                                                 |                | 1.425 | _   | 3.63 | V     |

Note:

1. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise noted.

#### Table 5.2. DC Characteristics

| (V <sub>DD</sub> = V <sub>DDA</sub> = 1.8 V to 3.3 V +10%/-5% | $V_{DDO} = 1.8 V + 5\% 2.5 V + 5\%$ | or $3.3 \text{ V} + 5\%$ T <sub>A</sub> = -40 to $85 ^{\circ}\text{C}$ |

|---------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------|

| VDD - VDDA - 1.0 V 10 3.3 V +10 /0/-3 /0                      | , vDDO - 1.0 v ±570, 2.5 v ±570     | $, 01 3.3 V \pm 3 / 0, 1 A = -40 (0 0 3 0)$                            |

| Parameter                 | Symbol            | Test Conditio                                | n          | Min | Тур | Мах   | Units |

|---------------------------|-------------------|----------------------------------------------|------------|-----|-----|-------|-------|

| Core Supply Current       | I <sub>DD</sub>   |                                              |            | _   | 45  | 70    | mA    |

| Output Buffer Supply Cur- | I <sub>DDOx</sub> | LVPECL Output <sup>4</sup> @ 15              | 6.25 MHz   | —   | 33  | 35 mA |       |

| rent                      |                   | HCSL Output <sup>4</sup> @ 10                | 0 MHz      | —   | 20  | 22    | mA    |

|                           |                   | LVDS Output <sup>4</sup> @ 156               | .25 MHz    | —   | 11  | 13    | mA    |

|                           |                   | 3.3 V VDDO<br>LVCMOS <sup>5</sup> output @ 1 |            | _   | 16  | 19    | mA    |

|                           |                   | 2.5 V VDDO<br>LVCMOS <sup>5</sup> output @ 1 | —          | 8   | 10  | mA    |       |

|                           |                   | 1.8 VDDO<br>LVCMOS <sup>5</sup> output @ 1   | 170 MHz    | —   | 6   | 7     | mA    |

| Total Power Dissipation   | Pd                | 48-pin                                       | Notes 1, 6 | _   | 540 | _     | mW    |

|                           |                   | 40-pin                                       | Note 2, 6  |     | 265 | _     | mW    |

|                           |                   | 32-pin                                       | Notes 3, 6 | —   | 230 | _     | mW    |

# Notes:

1. Si5332 48-pin test configuration: V<sub>DDD</sub> = V<sub>DDA</sub> = V<sub>DDI</sub> = 1.8 V, 3 × 2.5 V LVDS outputs enabled @156.25 MHz, 4x 1.8V HCSL outputs enabled @ 100 MHz, 3x 2.5 V LVPECL outputs enabled @ 125 MHz, 2x 3.3 V LVCMOS outputs enabled @ 25 MHz. Excludes power in termination resistors.

- 2. Si5332 40-pin test configuration: V<sub>DDD</sub> = V<sub>DDA</sub> = V<sub>DDI</sub> = 1.8 V, 4 × 2.5 V LVDS outputs enabled @ 156.25 MHz, 2 × 1.8 V HCSL outputs enabled @ 100 MHz, 2x 3.3 V LVCMOS outputs enabled @ 25 MHz. . Excludes power in termination resistors.

- 3. Si5332 32-pin test configuration: V<sub>DDD</sub> = V<sub>DDA</sub> = V<sub>DDI</sub> = 1.8 V, 2 × 2.5 V LVDS outputs enabled @ 156.25 MHz, 2 × 1.8 V HCSL outputs enabled @ 100 MHz. 2x 3.3 V LVCMOS outputs enabled @ 25 MHz. Excludes power in termination resistors.

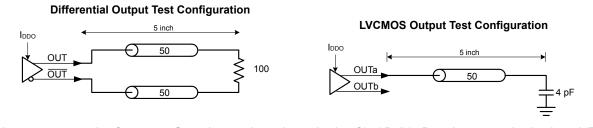

- 4. Differential outputs terminated into a 100  $\boldsymbol{\Omega}$  load.

- 5. LVCMOS outputs measured into a 5 inch 50  $\Omega$  PCB trace with 4 pF load.

6. Detailed power consumption for any configuration can be estimated using ClockBuilderPro when an evaluation board (EVB) is not available. All EVBs support detailed current measurements for any configuration.

# Table 5.3. Clock Input Specifications

# $(V_{DD} = V_{DDA} = 1.8 \text{ V to } 3.3 \text{ V +10\%/-5\%}, V_{DDO} = 1.8 \text{ V } \pm 5\%, 2.5 \text{ V } \pm 5\%, \text{ or } 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                 | Symbol                  | Test Condition                      | Min                   | Тур  | Max                   | Units               |

|---------------------------|-------------------------|-------------------------------------|-----------------------|------|-----------------------|---------------------|

| Input Clock (AC-coupled D | ifferential Input Clock | on CLKIN_2/CLKIN_2# or CL           | KIN_3/CLKIN           | _3#) |                       |                     |

| Frequency                 | F <sub>IN</sub>         | Differential                        | 10                    | _    | 250                   | MHz                 |

| Voltage Swing             | V <sub>PP</sub>         | Differential AC-coupled < 312.5 MHz | 0.5                   |      | 1.8                   | V <sub>PP_dif</sub> |

| Slew Rate                 | SR/SF                   | 20-80%                              | 0.75                  | _    | _                     | V/ns                |

| Duty Cycle                | DC                      |                                     | 40                    | _    | 60                    | %                   |

| Input Impedance           | R <sub>IN</sub>         |                                     | 10                    | _    | _                     | kΩ                  |

| Input Capacitance         | C <sub>IN</sub>         |                                     | 2                     | 3.5  | 6                     | pF                  |

| Input Clock (DC-coupled L | VCMOS Input Clock o     | n CLKIN_2 or CLKIN_3)               |                       |      |                       | I                   |

| Frequency                 | F <sub>IN</sub>         |                                     | 10                    |      | 170                   | MHz                 |

| Input High Voltage        | V <sub>IH</sub>         |                                     | 0.8 × V <sub>DD</sub> |      |                       | V                   |

| Input Low Voltage         | V <sub>IL</sub>         |                                     | _                     | _    | 0.2 × V <sub>DD</sub> | V                   |

| Slew Rate <sup>1,2</sup>  | SR/SF                   | 20-80%                              | 0.75                  |      |                       | V/ns                |

| Duty Cycle                | DC                      |                                     | 40                    | _    | 60                    | %                   |

| Input Capacitance         | C <sub>IN</sub>         |                                     | 2                     | 3.5  | 6                     | pF                  |

| Input Clock (DC-coupled L | VCMOS Input Clock o     | n CLKIN_1)                          | 1                     | I    |                       | 1                   |

| Frequency                 | F <sub>IN</sub>         |                                     | 10                    | _    | 170                   | MHz                 |

| Voltage Swing             |                         |                                     |                       | _    | 1                     | V                   |

| Input Low Voltage         | V <sub>IL</sub>         |                                     | _                     | _    | 0.2 x V <sub>DD</sub> | V                   |

| Slew Rate <sup>1, 2</sup> | SR/SF                   | 20-80%                              | 0.75                  |      | —                     | V/ns                |

| Duty Cycle                | DC                      |                                     | 40                    |      | 60                    | %                   |

| Input Capacitance         | C <sub>IN</sub>         |                                     | 2                     | 3.5  | 6                     | pF                  |

1. Imposed for jitter performance.

2. Rise and fall times can be estimated using the following simplified equation:  $tr/tf_{80-20} = ((0.8 - 0.2) * V_{IN_Vpp_se}) / SR$ .

## Table 5.4. External Crystal Input Specification

## $(V_{DD} = V_{DDA} = 1.8 \text{ V to } 3.3 \text{ V +10\%/-5\%}, V_{DDO} = 1.8 \text{ V } \pm 5\%, 2.5 \text{ V } \pm 5\%, \text{ or } 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                      | Symbol            | Test Condition                    | Min  | Тур   | Max  | Units |

|--------------------------------|-------------------|-----------------------------------|------|-------|------|-------|

| Crystal Frequency              | F <sub>xtal</sub> |                                   |      | 16-50 |      | MHz   |

| Load Capacitance               | CL                | 16 - 30 MHz                       | 6    | 12    | 18   | pF    |

|                                |                   | 31 - 50 MHz                       |      |       | 10   | pF    |

| Shunt Capacitance              | C <sub>O</sub>    | 16 - 30 MHz                       | _    | —     | 7    | pF    |

|                                |                   | 31 - 50 MHz                       | _    | _     | 2 50 | pF    |

| ESR                            | CL                | 16 - 30 MHz                       |      | _     | 50   | Ω     |

|                                |                   | 31 - 50 MHz                       |      | _     | 50   | Ω     |

| Max Crystal Drive Level        | dL                |                                   | 250  | _     | _    | μW    |

| Input Capacitance <sup>1</sup> | C <sub>IN</sub>   | Internal cap disabled             | _    | 2.5   |      | pF    |

|                                |                   | Internal cap enabled<br>(per pad) | 12   | _     | 24   | pF    |

| Input Voltage                  | V <sub>XIN</sub>  |                                   | -0.3 | _     | 1.3  | V     |

### Notes:

1. Internal capacitance on the xtal input pads is programmable or can be disabled. Please reference section 5.3.1 for more detailed information.

#### Table 5.5. Embedded Crystal Specifications

| Parameter             | Symbol | Test Condition                            | Min | Тур | Max | Units |

|-----------------------|--------|-------------------------------------------|-----|-----|-----|-------|

| Initial Accuracy      | fi     | Measured at +25 °C at<br>time of shipping | —   | ±20 | —   | ppm   |

| Total Stability       |        |                                           | -50 | _   | 50  | ppm   |

| Temperature Stability |        |                                           | -30 |     | 30  | ppm   |

# Table 5.6. Control Pins

$(V_{DD} = V_{DDA} = 1.8 \text{ V to } 3.3 \text{ V } +10\%/-5\%, V_{DDO} = 1.8 \text{ V } \pm5\%, 2.5 \text{ V } \pm5\%, \text{ or } 3.3 \text{ V } \pm5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                          | Symbol          | Test Condition | Min                       | Тур | Max                     | Units |

|------------------------------------|-----------------|----------------|---------------------------|-----|-------------------------|-------|

| Si5332 Control Input Pins (Inputx) |                 |                |                           |     |                         |       |

| Input Voltage                      | V <sub>IL</sub> |                | -0.1                      | _   | 0.3 × V <sub>DDOX</sub> | V     |

|                                    | V <sub>IH</sub> |                | $0.7 \times V_{DDOX}^{1}$ | —   | 1.1 × V <sub>DD</sub>   | V     |

| Input Capacitance                  | C <sub>IN</sub> |                | _                         | —   | 4                       | pF    |

| Pull-up/down Resistance            | R <sub>IN</sub> |                | _                         | 50  | _                       | kΩ    |

Note:

1. In the 48-QFN package, all universal input pins are powered by VDD\_DIG.

2. In the 40-QFN package, universal Input4, Input5, Input6, and Input7 on pins 21, 22, 29, 30 are powered by VDDOB. All other universal Inputx pins are powered by VDD\_DIG.

3. In the 32-pin package, universal Input2 and Input3 on pins 23, 24 are powered by VDDOB. All other universal Inputx pins are powered by VDD\_DIG.

4. If an output pair is instead defined as universal input pins in ClockBuilder Pro, those pins will be powered by the corresponding VDDOx of that corresponding bank.

# Table 5.7. Differential Clock Output Specifications

# $(V_{DD} = V_{DDA} = 1.8 \text{ V to } 3.3 \text{ V +10\%/-5\%}, V_{DDO} = 1.8 \text{ V } \pm 5\%, 2.5 \text{ V } \pm 5\%, \text{ or } 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter            | Symbol                         | Test Condition       |                | Min                    | Тур      | Мах                    | Units           |

|----------------------|--------------------------------|----------------------|----------------|------------------------|----------|------------------------|-----------------|

| Output Frequency     | fout                           | Integer synthe       | esis mode      | 5                      | _        | 312.5                  | MHz             |

|                      |                                | Fractional synth     | nesis mode     | 5                      | —        | 250                    | MHz             |

| Duty Cycle           | DC                             |                      |                | 48                     | _        | 52                     | %               |

| Output-Output Skew   | T <sub>SK</sub>                | Within the sa        | me bank        | —                      | —        | 30                     | ps              |

|                      |                                | Across b             | anks           | —                      | —        | 80                     | ps              |

| Output Voltage Swing | V <sub>SEPP</sub>              | LVPECL               |                | 0.6                    | 0.75     | 0.85                   | V <sub>PP</sub> |

|                      |                                | LVDS                 | 1.8/2.5/3.3 V  | 0.3                    | 0.375    | 0.45                   | V <sub>PP</sub> |

|                      |                                | HCSL                 |                | 0.7                    | 0.8      | 0.9                    | V <sub>PP</sub> |

| Common Mode Voltage  | V <sub>CM</sub>                | LVPECL               |                | _                      | VDDO-1.4 | _                      | V               |

|                      |                                | LVDS                 | 2.5/3.3 V      | 1.125                  | 1.2      | 1.275                  | V               |

|                      |                                | LVDS                 | 1.8 V          | 0.75                   | 0.8      | 0.85                   | V               |

|                      |                                | HCSL                 |                | 0.35                   | 0.4      | 0.45                   | V               |

| HCSL Edge Rate       | Edgr                           | Notes 12,            | Notes 12,14,18 |                        | _        | 4.5                    | V/ns            |

| HCSL Delta Tr        | D <sub>tr</sub>                | Notes 14,            | 17, 18         | —                      | —        | 125                    | ps              |

| HCSL Delta Tf        | D <sub>tf</sub>                | Notes 14,            | 17, 18         |                        | _        | 125                    | ps              |

| HCSL Vcross Abs      | V <sub>xa</sub>                | Notes 11, 13         | 8, 14, 17      | 250                    |          | 550                    | mV              |

| HCSL Vcross Rel      | V <sub>xr</sub>                | Notes 14, 16, 17, 24 |                | Calc                   | _        | Calc                   |                 |

| HCSL Delta Vcross    | D <sub>vcrs</sub>              | Notes 14, 17, 25     |                | _                      | _        | 140                    | mV              |

| HCSL Vovs            | V <sub>ovs</sub>               | Notes 14, 17, 22     |                | _                      | _        | V <sub>HIGH</sub> +300 | mV              |

| HCSL Vuds            | V <sub>uds</sub>               | Notes 14, 17, 23     |                | _                      | _        | V <sub>LOW</sub> -300  | mV              |

| HCSL Vrng            | V <sub>rng</sub>               | Notes 14, 17         |                | V <sub>HIGH</sub> -200 | _        | V <sub>LOW</sub> +200  | mV              |

| Rise and Fall Times  | t <sub>R</sub> /t <sub>F</sub> | LVDS                 | 3.3 V or 2.5 V | _                      | 200      | 350                    | ps              |

| (20% to 80%)         |                                |                      | 1.8 V          | _                      | 225      | 350                    | ps              |

| Rise and Fall Times  | t <sub>R</sub> /t <sub>F</sub> | LVPEC                | CL             | _                      |          | 300                    | ps              |

| (20% to 80%)         |                                | HCSI                 | _              | _                      | _        | 350                    | ps              |

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                 | Symbol                        | Test Condition                            | Min                | Тур           | Мах            | Units         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------|--------------------|---------------|----------------|---------------|

| Notes:                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                                           |                    |               |                |               |

| 1. For best jitter performar                                                                                                                                                                                                                                                                                                                                                                              | nce, keep the midpoir         | nt differential input slew rate fas       | ter than 0.3 V/n   | S.            |                |               |

| 2. Not in PLL bypass mod                                                                                                                                                                                                                                                                                                                                                                                  | e.                            |                                           |                    |               |                |               |

| 3. For best jitter performar                                                                                                                                                                                                                                                                                                                                                                              | nce, keep the midpoir         | nt input single ended slew rate f         | aster than 1 V/r   | IS.           |                |               |

| 4. On chip termination res                                                                                                                                                                                                                                                                                                                                                                                | istance can be progra         | ammed on (100ohm) or off (higl            | n impedance).      |               |                |               |

| 5. Not including R divider.                                                                                                                                                                                                                                                                                                                                                                               |                               |                                           |                    |               |                |               |

| 6. Input capacitance on cr<br>load capacitance.                                                                                                                                                                                                                                                                                                                                                           | ystal pins targets 23         | pf each plus 1 pf external trace          | capacitance to     | provide 12 p  | f series equiv | alent crystal |

| 7. Measured at crossing p                                                                                                                                                                                                                                                                                                                                                                                 | oint where the instan         | taneous voltage value of the ris          | ing edge of CL     | K equals the  | falling edge o | of CLK#.      |

| 8. Measure taken from differential waveform on a component test board. The edge (slew) rate is measured from -150mV to +150mV on the differential waveform. Scope is set to average because the scope sample clock is making most of the dynamic wiggles along the clock edge Only valid for Rising clock and Falling Clock#. Signal must be monotonic through the Vol to Voh region for Trise and Tfall. |                               |                                           |                    |               |                | c wiggles     |

| 9. This measurement refer                                                                                                                                                                                                                                                                                                                                                                                 | rs to the total variatio      | n from the lowest crossing poin           | t to the highest,  | regardless of | of which edge  | is crossing.  |

| 10. Test configuration is Rs                                                                                                                                                                                                                                                                                                                                                                              | =33.2 Ω, Rp=49.9, 2           | pF.                                       |                    |               |                |               |

| 11. Vcross(rel) Min and Ma<br>0.5 (0.700 – Vhavg).                                                                                                                                                                                                                                                                                                                                                        | x are derived using the       | ne following, Vcross(rel) Min = 0         | ).250 + 0.5 (Vha   | ivg - 0.700), | Vcross(rel) N  | lax = 0.550 - |

| 12. Measurement taken from                                                                                                                                                                                                                                                                                                                                                                                | m Single Ended wave           | eform.                                    |                    |               |                |               |

| 13. Measurement taken from                                                                                                                                                                                                                                                                                                                                                                                | m differential wavefor        | rm VLow Math function.                    |                    |               |                |               |

| 14. Overshoot is defined as                                                                                                                                                                                                                                                                                                                                                                               | the absolute value of         | of the maximum voltage.                   |                    |               |                |               |

| 15. Undershoot is defined a                                                                                                                                                                                                                                                                                                                                                                               | as the absolute value         | of the minimum voltage.                   |                    |               |                |               |

| 16. The crossing point mus                                                                                                                                                                                                                                                                                                                                                                                | t meet the absolute a         | nd relative crossing point speci          | fications simulta  | ineously.     |                |               |

| 17. ΔVcross is defined as the allowed variance in Vcro                                                                                                                                                                                                                                                                                                                                                    |                               | Il crossing voltages of Rising CL system. | OCK and Fallin     | g CLOCK#.     | This is the ma | aximum        |

| 18. Measured with oscilloso                                                                                                                                                                                                                                                                                                                                                                               | cope, averaging off, u        | sing min max statistics. Variation        | on is the delta be | etween min a  | and max.       |               |

| OUTx Vcm<br>OUTx Vcm                                                                                                                                                                                                                                                                                                                                                                                      |                               | se Vcm Vp                                 | p_diff = 2*Vpp_s   | e             |                |               |

| 19. LVDS swing levels for 5                                                                                                                                                                                                                                                                                                                                                                               | 50 $\Omega$ transmission line | es.                                       |                    |               |                |               |

## Table 5.8. LVCMOS Clock Output Specifications

$(V_{DD} = V_{DDA} = 1.8 \text{ V to } 3.3 \text{ V +10\%/-5\%}, V_{DDO} = 1.8 \text{ V } \pm 5\%, 2.5 \text{ V } \pm 5\%, \text{ or } 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                         | Symbol                         | Test Condition                         | Min      | Тур  | Max    | Units |

|-----------------------------------|--------------------------------|----------------------------------------|----------|------|--------|-------|

| Frequency                         | fout                           | 1.8-3.3 V CMOS                         | 5        |      | 170    | MHz   |

|                                   |                                | 1.5 V CMOS                             | 5        | _    | 133.33 | MHz   |

| Rise/Fall Time, 3.3 V<br>(20-80%) | t <sub>R</sub> /t <sub>F</sub> | 50 Ω impedance, 5"<br>trace, CL = 4 pf | —        | 0.5  | 0.8    | ns    |

| Rise/Fall Time, 2.5 V<br>(20-80%) | t <sub>R</sub> /t <sub>F</sub> | 50 Ω impedance, 5"<br>trace CL = 4 pf  | —        | 0.6  | 0.9    | ns    |

| Rise/Fall Time, 1.8 V<br>(20-80%) | t <sub>R</sub> /t <sub>F</sub> | 50 Ω impedance, 5"<br>trace CL = 4 pf  | —        | 0.75 | 1.1    | ns    |

| Rise/Fall Time, 1.5 V<br>(20-80%) | t <sub>R</sub> /t <sub>F</sub> | 50 Ω impedance, 5"<br>trace CL = 4 pf  | —        | 0.9  | 1.2    | ns    |

| CMOS Output Resistance            |                                | 3.3 V                                  | _        | 46   | _      | Ω     |

| (Single Strength)                 |                                | 2.5 V                                  | _        | 48   | -      | Ω     |

|                                   |                                | 1.8 V                                  | —        | 53   | -      | Ω     |

|                                   |                                | 1.5 V                                  | _        | 58   | _      | Ω     |

| CMOS Output Resistance            |                                | 3.3 V                                  | _        | 23   | -      | Ω     |

| (Double Strength)                 |                                | 2.5 V                                  | _        | 24   | -      | Ω     |

|                                   |                                | 1.8 V                                  | _        | 27   | -      | Ω     |

|                                   |                                | 1.5 V                                  | _        | 29   | _      | Ω     |

| CMOS Output Voltage               | V <sub>OH</sub>                | -4 mA load                             | VDDO-0.3 | _    | _      | V     |

|                                   | V <sub>OL</sub>                | 4 mA load                              | _        | _    | 0.3    | V     |

| Duty Cycle                        | DC                             | XO and PLL mode                        | 45       | _    | 55     | %     |

#### Table 5.9. Performance Characteristics

#### $(V_{DD} = V_{DDA} = 1.8 \text{ V to } 3.3 \text{ V } +10\%/-5\%, V_{DDO} = 1.8 \text{ V } \pm5\%, 2.5 \text{ V } \pm5\%, \text{ or } 3.3 \text{ V } \pm5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                 | Symbol              | Test Condition                                                                                                    | Min | Тур  | Max | Units |

|-------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Power Ramp                                | t <sub>VDD</sub>    | 0 V to V <sub>DDmin</sub>                                                                                         | 0.1 | _    | 10  | ms    |

| Initialization Time                       | tinitialization     | t <sub>initialization</sub> Time for I2C to become<br>operational after core<br>supply exceeds V <sub>DDmin</sub> |     | -    | 15  | ms    |

| Clock Stabilization from Power-up         | t <sub>STABLE</sub> | Time for clock outputs to appear after POR                                                                        | —   | 15   | 25  | ms    |

| Input to Output Propagation Delay         | t <sub>PROP</sub>   | Buffer mode<br>(PLL Bypass)                                                                                       | _   | 2.5  | 4   | ns    |

| Spread Spectrum PP Frequency<br>Deviation | SSDEV               | MultiSynth Output<br>< 250 MHz                                                                                    | 0.1 | -    | 2.5 | %     |

| 0.5% Spread Frequency Deviation           | SSDEV               | MultiSynth Output<br>< 250 MHz                                                                                    | 0.4 | 0.45 | 0.5 | %     |

| Spread Spectrum Modulation Rate           | SSDEV               | MultiSynth Output<br>< 250 MHz                                                                                    | 30  | 31.5 | 33  | kHz   |

#### Notes:

1. Outputs at same frequencies and using the same driver format.

2. The maximum step size is only limited by the register lengths; however, the MultiSynth output frequency must be kept between 5 MHz and 250MHz.

3. Update rate via I2C is also limited by the time it takes to perform a write operation.

4. Default value is ~31.5 kHz.

## Table 5.10. Jitter Performance Specifications

# $(V_{DD} = V_{DDA} = 1.8 \text{ V to } 3.3 \text{ V +10\%/-5\%}, V_{DDO} = 1.8 \text{ V } \pm 5\%, 2.5 \text{ V } \pm 5\%, \text{ or } 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                       | Symbol           | Test Condition                                                                                                      | Тур  | Max | Units    |  |

|-------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------|------|-----|----------|--|

| Jitter Generation,<br>Locked to External 25 MHz | $J_{GEN}$        | INT Mode<br>12 kHz – 20 MHz <sup>1,2</sup>                                                                          | 230  | 280 | fs RMS   |  |

| Clock                                           |                  | FRAC/DCO Mode<br>12 kHz – 20 MHz <sup>3,5</sup>                                                                     | 500  |     | fs RMS   |  |

| -                                               | J <sub>PER</sub> | Derived from integrated phase noise at a                                                                            | 3.3  |     | ps Pk-Pk |  |

| -                                               | J <sub>CC</sub>  | BER of 1e-12                                                                                                        | 3.1  |     | ps Pk    |  |

| -                                               | $J_PER$          | N = 10,000 cycles Integer or Fractional                                                                             | 12   |     | ps Pk-Pk |  |

| _                                               | Jcc              | Mode. <sup>2,3</sup> Measured in the time domain.<br>Performance is limited by the noise floor of<br>the equipment. | 11   |     | ps Pk    |  |

| Jitter Generation,<br>Locked to External 25 MHz | $J_{GEN}$        | INT Mode<br>12 kHz – 20 MHz <sup>1,2</sup>                                                                          | 230  | 280 | fs RMS   |  |

| Crystal                                         |                  | FRAC/DCO Mode<br>12 kHz – 20 MHz <sup>3,5</sup>                                                                     | 500  |     | fs RMS   |  |

|                                                 | J <sub>PER</sub> | Derived from integrated phase noise at a<br>BER of 1e-12                                                            | 3.5  |     | ps Pk-Pk |  |

|                                                 | J <sub>CC</sub>  | BER OF 12                                                                                                           | 3.1  |     | ps Pk    |  |

|                                                 | J <sub>PER</sub> | N = 10,000 cycles Integer or Fractional                                                                             | 12   |     | ps Pk-Pk |  |

| _                                               | Jcc              | Mode. <sup>2,3</sup> Measured in the time domain.<br>Performance is limited by the noise floor of<br>the equipment. | 11   |     | ps Pk    |  |

| Jitter Generation,<br>Locked to Embedded 50 MHz | $J_{GEN}$        | INT Mode<br>12 kHz – 20 MHz <sup>1,2</sup>                                                                          | 230  |     | fs RMS   |  |

| Crystal                                         |                  | FRAC/DCO Mode<br>12 kHz – 20 MHz <sup>3,5</sup>                                                                     | 500  |     | fs RMS   |  |

| -                                               | J <sub>PER</sub> | Derived from integrated phase noise at a                                                                            | 3.5  |     | ps Pk-Pk |  |

| -                                               | J <sub>CC</sub>  | BER of 1e-1                                                                                                         | 3.1  |     | ps Pk    |  |