UC1832 UC2832/3 UC3832/3

# **Precision Low Dropout Linear Controllers**

#### **FEATURES**

- Precision 1% Reference

- Over-Current Sense Threshold Accurate to 5%

- Programmable Duty-Ratio Over-Current Protection

- 4.5 V to 36 V Operation

- 100mA Output Drive, Source, or Sink

- Under-Voltage Lockout

Additional Features of the UC2832 series:

- Adjustable Current Limit to Current Sense Ratio

- Separate +VIN terminal

- Programmable Driver Current Limit

- Access to V<sub>REF</sub> and E/A(+)

- Logic-Level Disable Input

#### **DESCRIPTION**

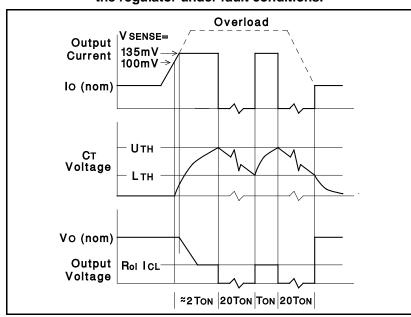

The UC2832 and UC3833 series of precision linear regulators include all the control functions required in the design of very low dropout linear regulators. Additionally, they feature an innovative duty-ratio current limiting technique which provides peak load capability while limiting the average power dissipation of the external pass transistor during fault conditions. When the load current reaches an accurately programmed threshold, a gated-astable timer is enabled, which switches the regulator's pass device off and on at an externally programmable duty-ratio. During the on-time of the pass element, the output current is limited to a value slightly higher than the trip threshold of the duty-ratio timer. The constant-current-limit is programmable on the UCx832 to allow higher peak current during the on-time of the pass device. With duty-ratio control, high initial load demands and short circuit protection may both be accommodated without extra heat sinking or foldback current limiting. Additionally, if the timer pin is grounded, the duty-ratio timer is disabled, and the IC operates in constant-voltage/constant-current regulating mode.

These IC's include a 2 Volt (±1%) reference, error amplifier, UVLO, and a high current driver that has both source and sink outputs, allowing the use of either NPN or PNP external pass transistors. Safe operation is assured by the inclusion of under-voltage lockout (UVLO) and thermal shutdown.

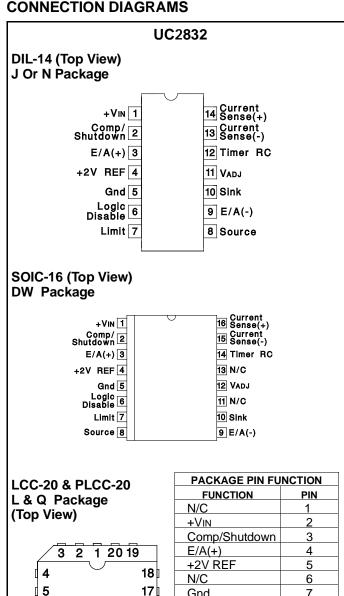

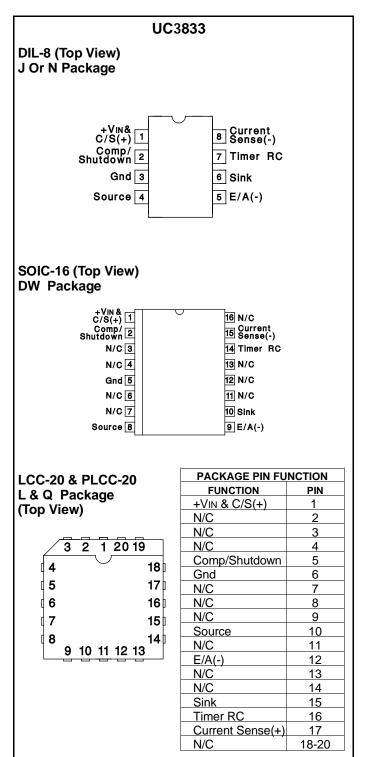

The UC3833 family includes the basic functions of this design in a low-cost, 8-pin mini-dip package, while the UC2832 series provides added versatility with the availability of 14 pins. Packaging options include plastic (N suffix), or ceramic (J suffix). Specified operating temperature ranges are: commercial (0°C to 70°C), order UC3832/3 (N or J); and industrial (–40°C to 85°C), order UC2832/3 (N or J). Surface mount packaging is also available.

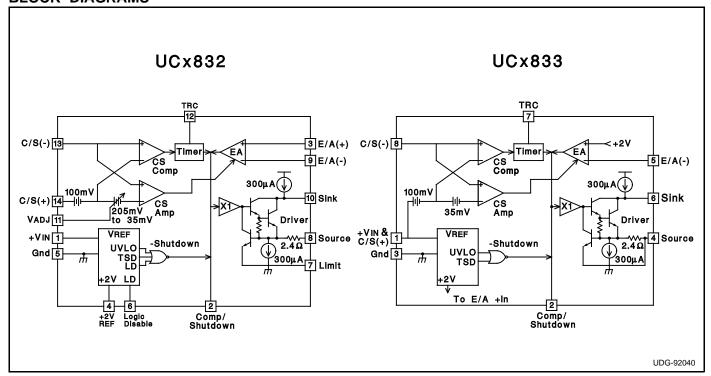

#### **BLOCK DIAGRAMS**

#### ABSOLUTE MAXIMUM RATINGS

| 0V  |

|-----|

| nΑ  |

| 0V  |

| 2V  |

| ∕ıN |

| °C  |

| °C  |

| °C  |

|     |

Note 1: Unless otherwise indicated, voltages are referenced to ground and currents are positive into, negative out of, the specified terminals.

Note 2: See Unitrode Integrated Circuits databook for information regarding thermal specifications and limitations of packages.

6

7

8

16

15

14

9 10 11 12 13

| 9 E/A(-)             |       |  |  |  |  |  |  |  |

|----------------------|-------|--|--|--|--|--|--|--|

|                      |       |  |  |  |  |  |  |  |

| PACKAGE PIN FUNCTION |       |  |  |  |  |  |  |  |

| FUNCTION PIN         |       |  |  |  |  |  |  |  |

| N/C                  | 1     |  |  |  |  |  |  |  |

| +VIN                 | 2     |  |  |  |  |  |  |  |

| Comp/Shutdown        | 3     |  |  |  |  |  |  |  |

| E/A(+)               | 4     |  |  |  |  |  |  |  |

| +2V ŘEF              | 5     |  |  |  |  |  |  |  |

| N/C                  | 6     |  |  |  |  |  |  |  |

| Gnd                  | 7     |  |  |  |  |  |  |  |

| Logic Disable        | 8     |  |  |  |  |  |  |  |

| Limit                | 9     |  |  |  |  |  |  |  |

| Source               | 10    |  |  |  |  |  |  |  |

| N/C                  | 11    |  |  |  |  |  |  |  |

| E/A(-)               | 12    |  |  |  |  |  |  |  |

| Sink                 | 13    |  |  |  |  |  |  |  |

| VADJ                 | 14    |  |  |  |  |  |  |  |

| N/C                  | 15-17 |  |  |  |  |  |  |  |

| Timer RC             | 18    |  |  |  |  |  |  |  |

| Current Sense(-)     | 19    |  |  |  |  |  |  |  |

| Current Sense(+)     | 20    |  |  |  |  |  |  |  |

$\begin{tabular}{lll} \textbf{ELECTRICAL} & \textbf{CHARACTERISTICS:} & Unless otherwise stated, specifications hold for $$TA = 0^{\circ}C$ to $70^{\circ}C$ for the UC3832/3, $$-40^{\circ}C$ to $85^{\circ}C$ for the UC2832/3, $$+VIN = 15V$, Driver sink = $$+VIN$, $$C/S(+)$ voltage = $$+VIN$. $$TA=TJ$. \end{tabular}$

|                                    |                                                    |      | _     |      | 1     |

|------------------------------------|----------------------------------------------------|------|-------|------|-------|

| PARAMETER                          | TEST CONDITIONS                                    | MIN  | TYP   | MAX  | UNITS |

| Input Supply                       |                                                    |      |       |      |       |

| Supply Current                     | +VIN = 6 V                                         |      | 6.5   | 10   | mA    |

|                                    | +VIN = 36 V                                        |      | 9.5   | 15   | mA    |

|                                    | Logic Disable = 2 V (UCx832 only)                  |      | 3.3   |      | mA    |

| Reference Section                  |                                                    |      | I     |      | 1     |

| Output Voltage (Note 3)            | TJ = 25°C, IDRIVER = 10 mA                         | 1.98 | 2.00  | 2.02 | V     |

|                                    | over temperature, IDRIVER = 10 mA                  | 1.96 | 2.00  | 2.04 | V     |

| Load Regulation (UCx832 only)      | Io = 0 to 10 m                                     | -10  | -5.0  |      | mV    |

| Line Regulation                    | +VIN = 4.5 V to 36 V, IDRIVER = 10 m               |      | 0.033 | 0.5  | mV/V  |

| Under-Voltage Lockout Threshold    |                                                    |      | 3.6   | 4.5  | V     |

| Logic Disable Input (UCx832 only)  |                                                    |      | 1     |      |       |

| Threshold Voltage                  |                                                    | 1.3  | 1.4   | 1.5  | V     |

| Input Bias Current                 | Logic Disable = 0 V                                | -5.0 | -1.0  |      | μΑ    |

| <b>Current Sense Section</b>       |                                                    |      |       |      |       |

| Comparator Offset                  |                                                    | 95   | 100   | 105  | mV    |

|                                    | Over Temperature                                   | 93   | 100   | 107  | mV    |

| Amplifier Offset (UCx833 only)     |                                                    | 110  | 135   | 170  | mV    |

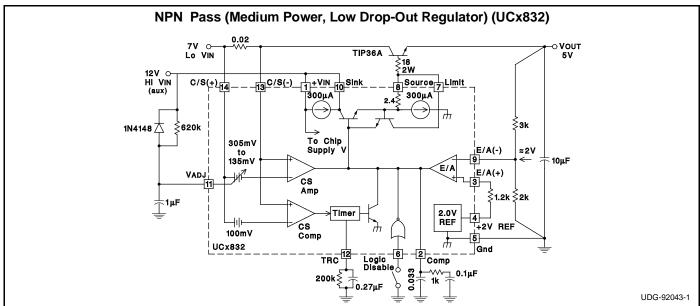

| Amplifier Offset (UCx832 only)     | VadJ = Open                                        | 110  | 135   | 170  | mV    |

|                                    | VADJ = 1 V                                         | 180  | 235   | 290  | mV    |

|                                    | VADJ = 0 V                                         | 250  | 305   | 360  | mV    |

| Input Bias Current                 | VCM = +VIN                                         | 65   | 100   | 135  | μΑ    |

| Input Offset Current (UCx832 only) | VCM = +VIN                                         | -10  |       | 10   | μΑ    |

| Amplifier CMRR (UCx832 only)       | VCM = 4.1 V to + VIN + 0.3                         |      | 80    |      | dB    |

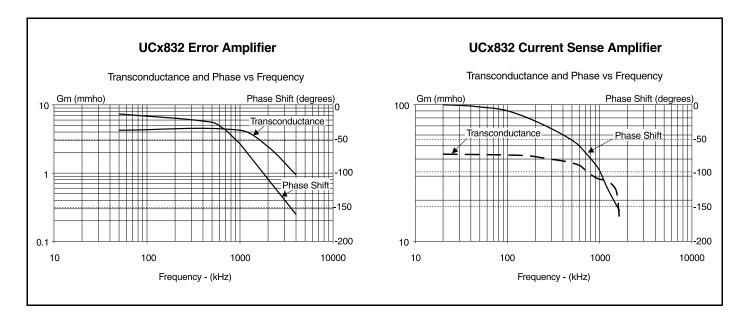

| Transconductance                   | ICOMP = $\pm 100 \mu\text{A}$                      |      | 65    |      | mS    |

| VADJ Input Current (UCx832 only)   | VADJ = 0V                                          | -10  | -1    |      | μΑ    |

| Timer                              |                                                    | -    |       |      | -     |

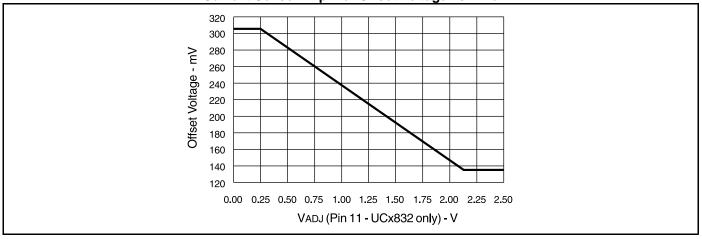

| Inactive Leakage Current           | C/S(+) = C/S(-) = +VIN; TRC pin = 2 V              |      | 0.25  | 1.0  | μΑ    |

| Active Pullup Current              | C/S(+) = +VIN, C/S(-) = +VIN - 0.4V; TRC pin = 0 V | -345 | -270  | -175 | μΑ    |

| Duty Ratio (note 4)                | ontime/period, RT = 200k, CT = 0.27μF              |      | 4.8   |      | %     |

| Period (notes 4,5)                 | ontime + offtime, RT = 200k, CT = 0.27μF           |      | 36    |      | ms    |

| Upper Trip Threshold (Vu)          |                                                    |      | 1.8   |      | V     |

| Lower Trip Threshold (VI)          |                                                    |      | 0.9   |      | V     |

| Trip Threshold Ratio               | Vu/VI                                              |      | 2.0   |      | V/V   |

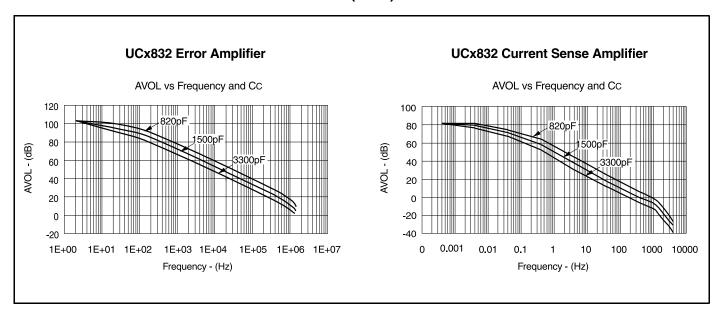

| Error Amplifier                    |                                                    |      |       |      | •     |

| Input Offset Voltage (UCx832 only) | VCM = VCOMP = 2 V                                  | -8.0 |       | 8.0  | mV    |

| Input Bias Current                 | VCM = VCOMP = 2 V                                  | -4.5 | -1.1  |      | μΑ    |

| Input Offset Current (UCx832 only) | Vcm = Vcomp = 2 V                                  | -1.5 |       | 1.5  | μA    |

| AVOL                               | VCOMP = 1 V to 13 V                                | 50   | 70    |      | dB    |

| CMRR (UCx832 only)                 | Vcm = 0V to +Vin - 3 V                             | 60   | 80    |      | dB    |

| PSRR (UCx832 only)                 | VcM = 2 V, +VIN = 4.5 V to 36                      |      | 90    |      | dB    |

| Transconductance                   | ICOMP = $\pm 10 \mu\text{A}$                       |      | 43    |      | mS    |

| VOH                                | ICOMP = 0, Volts below +VIN                        |      | .95   | 1.3  | V     |

| VOL                                | ICOMP = 0                                          |      | .45   | 0.7  | V     |

| IOH                                | VCOMP = 2 V                                        | -700 | -500  | -100 | μΑ    |

#### **ELECTRICAL** Unless otherwise stated, specifications hold for TA = 0°C to 70°C for the UC3832/3, -40°C to **CHARACTERISTICS (cont.)** 85°C for the UC2832/3, +VIN = 15 V, Driver sink = +VIN, C/S(+) voltage = +VIN. TA=TJ.

| PARAMETER                          | TEST CONDITIONS                                            | MIN   | TYP  | MAX  | UNITS |

|------------------------------------|------------------------------------------------------------|-------|------|------|-------|

| Error Amplifier (cont.)            |                                                            |       |      |      |       |

| IOL                                | VCOMP = 2 V, C/S(-) = +VIN                                 | 100   | 500  | 700  | μΑ    |

|                                    | VCOMP = 2 V, C/S(-) = +VIN - 0.4 V                         | 2     | 6    |      | mA    |

| Driver                             |                                                            |       |      |      |       |

| Maximum Current                    | Driver Limit & Source pins common; T <sub>J</sub> = 25°C   | 200   | 300  | 400  | mA    |

|                                    | Over Temperature                                           | 100   | 300  | 450  | mA    |

| Limiting Voltage (UCx832 only)     | Driver Limit to Source voltage at current limit,           |       |      |      |       |

|                                    | ISOURCE = -10 mA; TJ = 25°C (Note 6)                       |       | .72  |      | V     |

| Internal Current Sense Resistance  | T <sub>J</sub> = 25°C (Note 6)                             |       | 2.4  |      | Ω     |

| Pull-Up Current at Driver Sink     | Compensation/Shutdown = 0.4 V; Driver Sink = +VIN - 1V     | -800  | -300 | -100 | μΑ    |

|                                    | Compensation/Shutdown = 0.4 V, +VIN = 36 V; Driver         |       |      |      |       |

|                                    | Sink = 35 V                                                | -1000 | -300 | -75  | μΑ    |

| Pull-Down Current at Driver Source | Compensation/Shutdown = 0.4 V; Driver Source = 1 V         | 150   | 300  | 700  | μΑ    |

| Saturation Voltage Sink to Source  | Driver Source = 0 V; Driver Current = 100 mA               |       | 1.5  |      | V     |

| Maximum Source Voltage             | Driver Sink = +VIN, Driver Current = 100 mA                |       |      |      |       |

|                                    | Volts below + VIN                                          |       | 3.0  |      | V     |

| UVLO Sink Leakage                  | +VIN = C/S(+) = C/S(-) = 2.5 V, Driver Sink = 15 V, Driver |       |      |      |       |

|                                    | Source = 0 V, TA = 25°C                                    |       | 25   |      | μΑ    |

| Maximum Reverse Source Voltage     | Compensation/Shutdown = 0 V; ISOURCE = 100 μA,             |       |      |      |       |

|                                    | +VIN = 3 V                                                 |       | 1.6  |      | V     |

| Thermal Shutdown                   |                                                            |       | 160  |      | °C    |

Note 3: On the UCx833 this voltage is defined as the regulating level at the error amplifier inverting input, with the error amplifier driving VSOURCE to 2 V.

Note 4: These parameters are first-order supply-independent, however both may vary with supply for +VIN less than about 4 V. This supply variation will cause a slight change in the timer period and duty cycle, although a high off-time/on-time ratio will be maintained.

Note 5: With recommended RT value of 200k, Toff≈ RT CT \* In(Vu/VI) ±10%.

Note 6: The internal current limiting voltage has a temperature dependence of approximately -2.0 mV/°C, or -2800 ppm/°C. The internal  $2.4\,\Omega$  sense resistor has a temperature dependance of approximately +1500 ppm/°C.

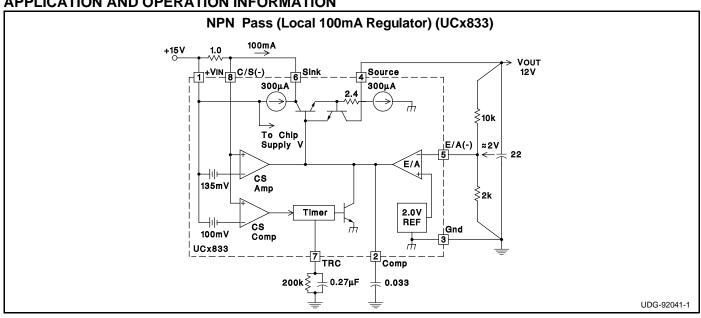

#### APPLICATION AND OPERATION INFORMATION

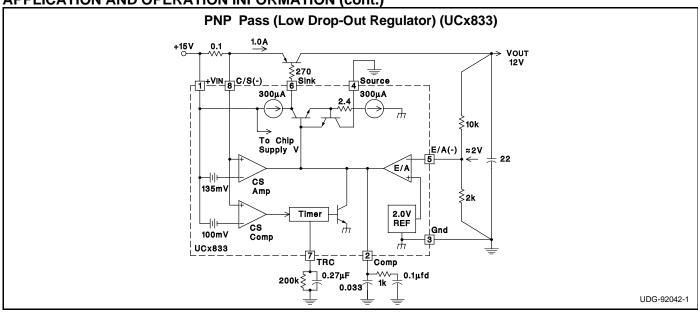

## **APPLICATION AND OPERATION INFORMATION (cont.)**

#### **Estimating Maximum Load Capacitance**

For any power supply, the rate at which the total output capacitance can be charged depends on the maximum output current available and on the nature of the load. For a constant-current current-limited power supply, the output will come up if the load asks for less than the maximum available short-circuit limit current.

To guarantee recovery of a duty-ratio current-limited power supply from a short-circuited load condition, there is a maximum total output capacitance which can be charged for a given unit ON time. The design value of ON time can be adjusted by changing the timing capacitor. Nominally,  $ToN = 0.693 \times 10k \times CT$ .

Typically, the IC regulates output current to a maximum of  $IMAX = K \times ITH$ , where ITH is the timer trip-point current,

and

$$K = \frac{Current \ Sense \ Amplifier \ Offset \ Voltage}{100 \ mA}$$

$\approx$ 1.35 for UCx833, and is variable from 1.35 to 3.05 with VADJ for the UCx832.

For a worst-case constant-current load of value just less than  $\ensuremath{\mathsf{ITH}}$ ,  $\ensuremath{\mathsf{CMAX}}$  can be estimated from:

$$C_{MAX} = ((K-1)I_{TH}) \left(\frac{T_{ON}}{V_{OUT}}\right)$$

where Vout is the nominal regulator output voltage.

For a resistive load of value RL, the value of CMAX can be estimated from:

$$C_{MAX} = \frac{T_{ON}}{R_L} \bullet \frac{1}{ln \left[ \left( 1 - \frac{V_{OUT}}{K \bullet I_{TH} \bullet R_L} \right)^{-1} \right]}.$$

# **APPLICATION AND OPERATION INFORMATION (cont.)**

## **Current Sense Amplifier Offset Voltage vs VADJ**

#### **UCx832/33 Timer Function**

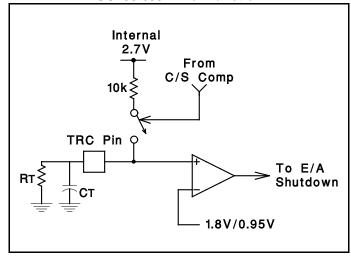

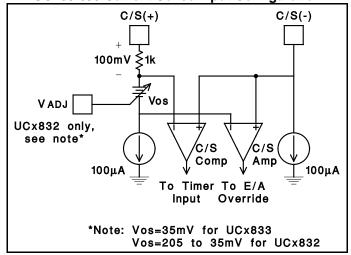

### UCx832/33 Current Sense Input Configuration

# Load current, timing capacitor voltage, and output voltage of the regulator under fault conditions.

# **APPLICATION AND OPERATION INFORMATION (cont.)**

17-Mar-2017

### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5)                 | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|-----------------------------------------|---------|

| 5962-9326501M2A  | ACTIVE | LCCC         | FK                 | 20   | 1              | TBD                        | POST-PLATE       | N / A for Pkg Type  | -55 to 125   | 5962-<br>9326501M2A<br>UC1832L/<br>883B | Samples |

| 5962-9326501MCA  | ACTIVE | CDIP         | J                  | 14   | 1              | TBD                        | A42              | N / A for Pkg Type  | -55 to 125   | 5962-9326501MC<br>A<br>UC1832J/883B     | Samples |

| 5962-9326501V2A  | ACTIVE | LCCC         | FK                 | 20   | 1              | TBD                        | POST-PLATE       | N / A for Pkg Type  |              | 5962-<br>9326501V2A<br>UC1832L<br>QMLV  | Samples |

| 5962-9326501VCA  | ACTIVE | CDIP         | J                  | 14   | 1              | TBD                        | A42              | N / A for Pkg Type  |              | 5962-9326501VC<br>A<br>UC1832JQMLV      | Samples |

| UC1832J          | ACTIVE | CDIP         | J                  | 14   | 1              | TBD                        | A42              | N / A for Pkg Type  | -55 to 125   | UC1832J                                 | Samples |

| UC1832J883B      | ACTIVE | CDIP         | J                  | 14   | 1              | TBD                        | A42              | N / A for Pkg Type  | -55 to 125   | 5962-9326501MC<br>A<br>UC1832J/883B     | Samples |

| UC1832L883B      | ACTIVE | LCCC         | FK                 | 20   | 1              | TBD                        | POST-PLATE       | N / A for Pkg Type  | -55 to 125   | 5962-<br>9326501M2A<br>UC1832L/<br>883B | Samples |

| UC2832DW         | ACTIVE | SOIC         | DW                 | 16   | 40             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -25 to 85    | UC2832DW                                | Samples |

| UC2833DW         | ACTIVE | SOIC         | DW                 | 16   | 40             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | UC2833DW                                | Samples |

| UC2833DWG4       | ACTIVE | SOIC         | DW                 | 16   | 40             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | UC2833DW                                | Samples |

| UC2833DWTR       | ACTIVE | SOIC         | DW                 | 16   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | UC2833DW                                | Samples |

| UC3832DW         | ACTIVE | SOIC         | DW                 | 16   | 40             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | 0 to 70      | UC3832DW                                | Samples |

| UC3832DWG4       | ACTIVE | SOIC         | DW                 | 16   | 40             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | 0 to 70      | UC3832DW                                | Samples |

## PACKAGE OPTION ADDENDUM

17-Mar-2017

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|----------------------|---------|

| UC3833DW         | ACTIVE | SOIC         | DW                 | 16   | 40             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | 0 to 70      | UC3833DW             | Samples |

| UC3833DWTR       | ACTIVE | SOIC         | DW                 | 16   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | 0 to 70      | UC3833DW             | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

17-Mar-2017

#### OTHER QUALIFIED VERSIONS OF UC1832, UC1832-SP, UC2832, UC3832:

• Catalog: UC3832, UC1832

● Enhanced Product: UC2832-EP

Military: UC1832

Space: UC1832-SP

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Enhanced Product Supports Defense, Aerospace and Medical Applications

- Military QML certified for Military and Defense Applications

- Space Radiation tolerant, ceramic packaging and qualified for use in Space-based application

# PACKAGE MATERIALS INFORMATION

www.ti.com 10-Aug-2016

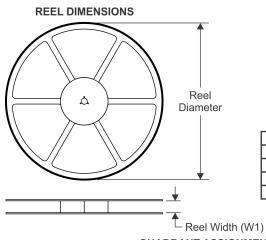

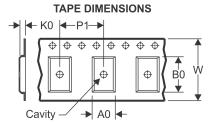

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

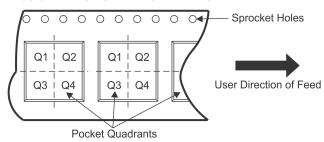

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

|   | Device     | _    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| I | UC2833DWTR | SOIC | DW                 | 16 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

| ĺ | UC3833DWTR | SOIC | DW                 | 16 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

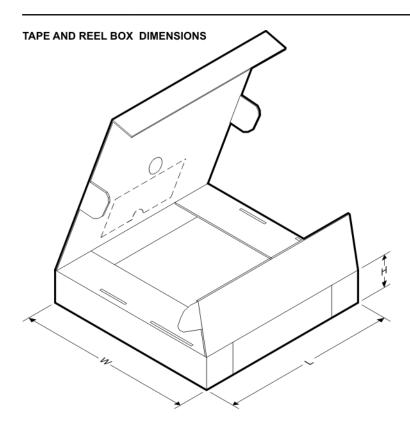

www.ti.com 10-Aug-2016

#### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC2833DWTR | SOIC         | DW              | 16   | 2000 | 367.0       | 367.0      | 38.0        |

| UC3833DWTR | SOIC         | DW              | 16   | 2000 | 367.0       | 367.0      | 38.0        |

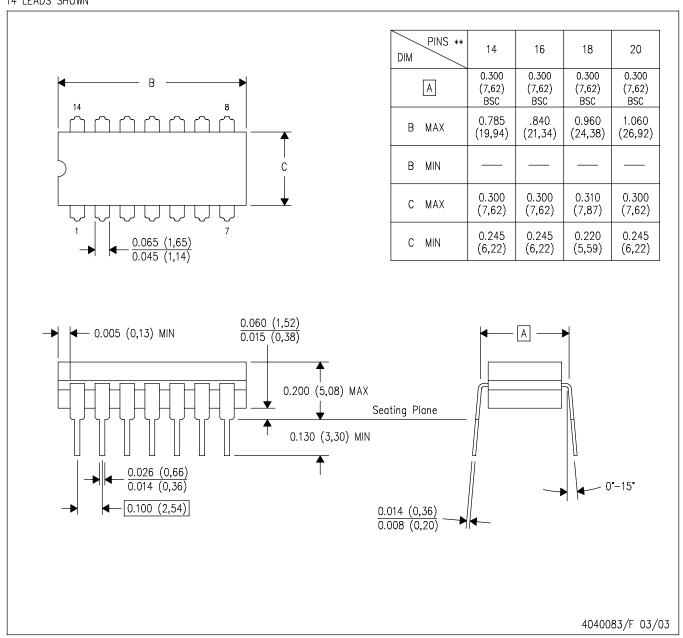

# 14 LEADS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, GDIP1-T18 and GDIP1-T20.

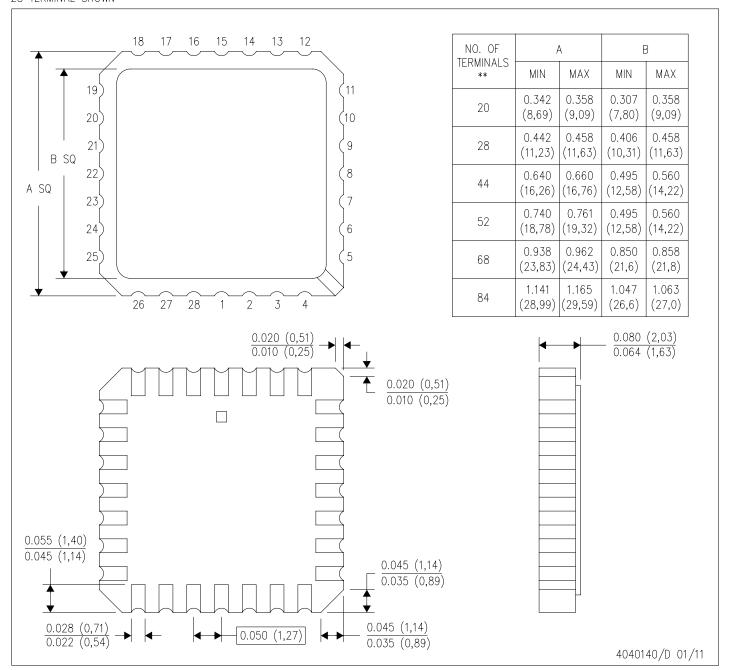

# FK (S-CQCC-N\*\*)

# LEADLESS CERAMIC CHIP CARRIER

28 TERMINAL SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a metal lid.

- D. Falls within JEDEC MS-004

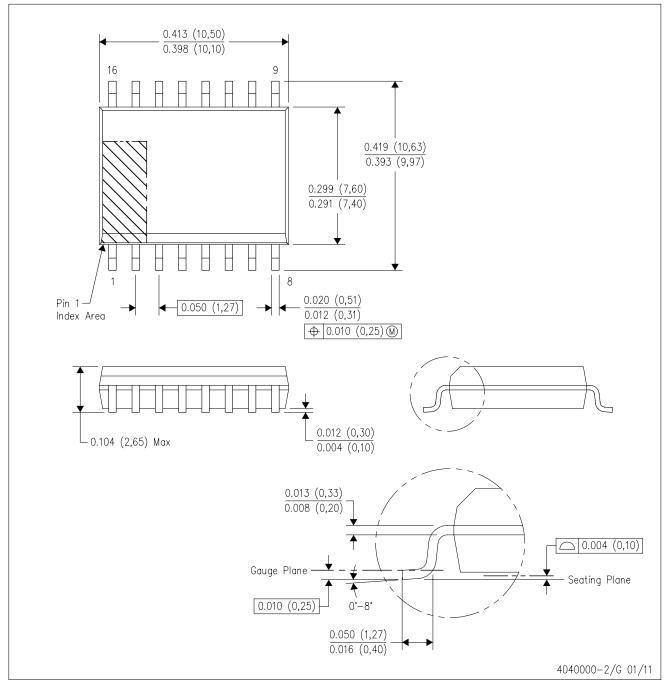

DW (R-PDSO-G16)

# PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters). Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AA.

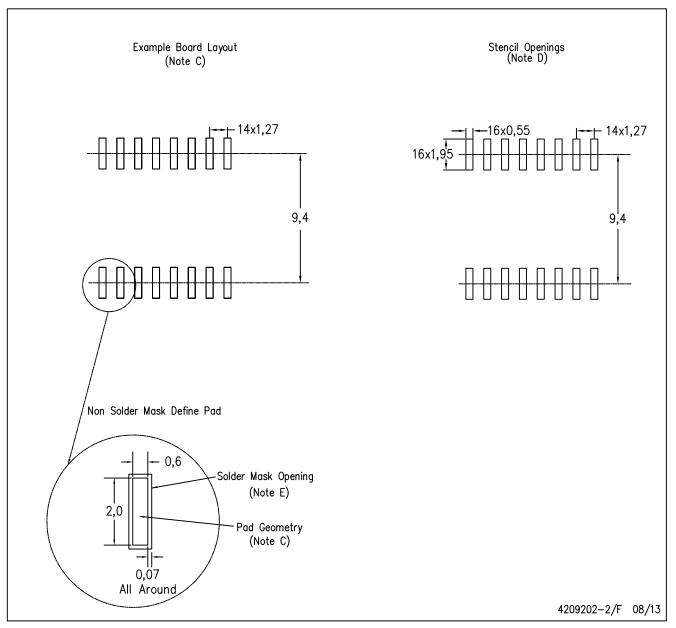

# DW (R-PDSO-G16)

# PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Refer to IPC7351 for alternate board design.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC—7525

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.