CPLD

1. 概要

デジタル回路は以前は専用のデジタルIC(74HCXXシリーズ等)で設計、構成していましたが、近年、FPGA,CPLDといったプログラマブルなICが登場しました。

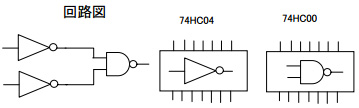

従来、デジタル回路といえば、右図のように専用のICを用いてこれの組み合わせで構成していました。

また、機能表現も回路図で表されていました。

このような場合、一旦、基板化すると設計変更する場合、大変な作業となり、機能が複雑化すればICの数も増えて基板面積が大きくなります。

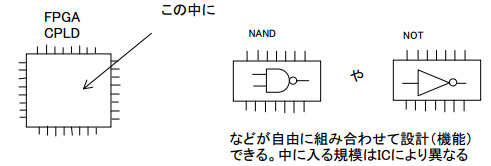

これに対して、CPLD,FPGAなどICの中の機能を自由に設計、変更できるものが登場してきました。

CPLD (Complex Programmable Logic Array)

FPGA (Field Programmable Gate Array)

どちらもプログラム書き換え可能なICです。明確な違いはあまり無く、一般的には

① FPGAのほうがCPLDより回路規模が大きい。

→ 大規模ロジックに使われる。

② FPGAはプログラム(機能)を内部のSRAMに保存するため、

起動(電源ON)のたびに外部のROMからダウンロードする。

CPLDは内部に不揮発性(電源をOFFしても消えないメモリ)

メモリを内蔵している。

ですが、FPGAと呼ばれる中でも不揮発性メモリを内蔵しているものもあります。

どちらも機能を自由に設計、変更できるプログラマブルなデバイスで単にPLD(Programmable Logic Device)とも言ったりします。

FPGAとCPLDはどちらもPLDです。

代表的なメーカーにアルテラとザイリンクスがあります。

2. CPLDの開発方法

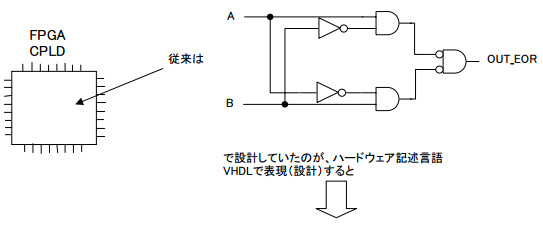

ICの中の設計は従来の回路図による設計方法もありますが、最近はCPUのソフトウェア設計と同じようにソフトウェアにて設計するのが主流です。

使うようです。以下にVHDLでの記述例を示します。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity EX_NOR is

Port ( A,B : in std_logic; OUT_EOR : out std_logic);

end EX_NOR;

architecture RTL of EX_NOR is begin

OUT_EOR <= ( A and not B ) nor ( not A and B )

end RTL;

機能(回路)が多くなれば、従来からの回路図で設計するより、ハードウェア記述言語で設計したほうが開発効率が良くなります。

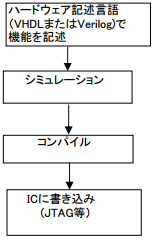

右図に開発の流れを示します。

ハードウェア記述言語に限らず、FPGA,CPLDでの開発の中で最大のメリットは「シミュレーション」が行えることです。

これは、事前に設計どおりか、チェック(シミュレーション)できることです。

事前にシュミレーションできることは完成度の高い

設計ができることになりますので開発時間の短縮

にもつながります。

開発に必要なツールはCPLD(FPGA)の各メーカーから提供されています。

なお、IC(CPLD)へのプログラム書き込みはJTAG等で書き込みます。

開発の流れ

3. 製品例

以下に製品例を示します。詳細は各メーカーのデータシートを参照願います。

No. |

型番 |

メーカー |

マクロ |

使用可能 |

パッケージ |

|

セル数 |

ゲート数 |

|||||

|

|

|

|

|||

1 |

ザイリンクス |

108 |

2400 |

PLCC 84pin |

||

2 |

ザイリンクス |

108 |

2400 |

PQFP 100pin |

||

3 |

ザイリンクス |

72 |

1600 |

PLCC 44pin |

||

4 |

ザイリンクス |

72 |

1600 |

PLCC 84pin |

||

5 |

ザイリンクス |

72 |

1600 |

PQFP 100pin |

||

6 |

ザイリンクス |

36 |

800 |

PLCC 44pin |

||

7 |

ザイリンクス |

36 |

800 |

VQFP 44pin |

マクロセルとは書き換え可能(プログラマブル)なレジスタでいくつかのゲートとDフリップフロップで構成されているものです。

外観例

XC95108 |

XC9572 |

PLCC 84pin |

PLCC 44pin |

|

|