★プッシュプルで用いた例

MOS-FETは比較的大きな電力を扱うことができる品種が多いです。

そこで、電力増幅用としての「プッシュプル増幅」で用いる例を紹介します。

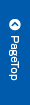

図21に、トランジスタおよびMOS-FETで構成した場合のプッシュプル増幅の原理図を示します。

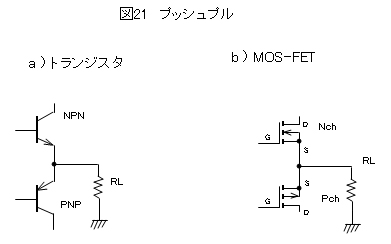

NPN→Nch、PNP→Pchに置き換えただけです。 なお、MOSFETの場合も「クロスオーバー歪」を減少させる目的で、なんらかのバイアス電圧が必要になり、この原理図を図22に示します。

プッシュプル増幅回路は、

トランジスタの場合は、エミッタフォロワ

MOS FETの場合は、ソースフォロワ ですから、

どちらの回路も電圧利得は1です。

またプッシュプル回路の入力インピーダンスZinは

トランジスタの場合は、 Zin ≒ hfe×RL

MOS-FETの場合は、 Zinは非常に大きい となり、

MOS FETの場合は、信号源(入力)で大きな電力を必要としません。

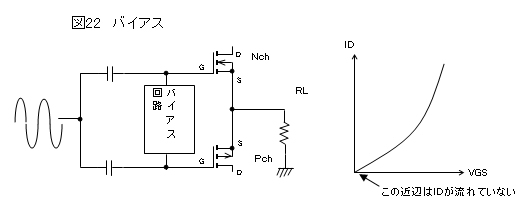

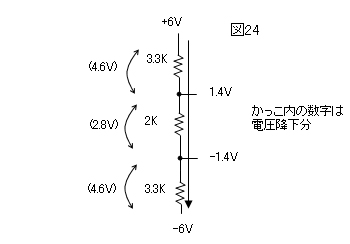

バイアス回路例を図23に示します。抵抗RA、RB、RCによる電圧分割です。

抵抗RBの両端の電圧降下VBは、

VB = (Vcc×2)×RB / (RA+RB+RC) です。

例えば、

+Vcc=+6V,-Vcc=-6V

RA=RC=3.3KΩ,RB=2KΩ とすれば、

VB=(6×2)×2 / (3.3+2+3.3)≒2.8V となります。

|