マルツTOP > APPLICATION LAB TOPページ > おすすめ技術記事アーカイブス > FPGAの基礎(第2部):Lattice Semiconductor FPGAの概要

FPGAの基礎(第2部):Lattice Semiconductor FPGAの概要

著者 Clive "Max" Maxfield 氏

Digi-Keyの北米担当編集者 提供

2019-12-18

マルツ掲載日:2020-03-16

編集者メモ:RISCやCISC、グラフィックスプロセッサとFPGAの組み合わせ、あるいはFPGA単独、あるいはファブリックの一部としてハードプロセッサコアを強化するFPGAによって、最適なソリューションが得られることがよくあります。一方で、多くの設計者はFPGAの機能やその進化の過程、使い方をよく知りません。第1部では、FPGAの概要とFPGAが必要な理由について概要を説明しています。この第2部では、FPGAベンダであるLattice Semiconductorが提供するFPGAデバイスファミリと設計ツールについて説明します。第3部、第4部、第5部では、Altera、Microchip、Xilinxが提供しているFPGAについて説明します。

第1部で説明したように、フィールドプログラマブルゲートアレイ(FPGA)は、スタンドアロンでも異種アーキテクチャでも重要なコンピューティング資産となる多くの特性を備えています。しかし、設計者はFPGAの機能や、これらのデバイスを設計に取り込む方法を十分に理解していません。

この状況を解決する1つの方法は、大手ベンダーが提供しているFPGAアーキテクチャとその関連ツールについて理解を深めることです。そこで最初に、Lattice Semiconductorの製品から見ていきます。

高度なFPGAオプションの概要

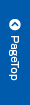

市場にはさまざまな種類のFPGAが出回り、それぞれに異なる機能が組み合わされています。FPGAの中心となるのが、プログラマブルファブリックです。これは、プログラマブルロジックブロックの配列として表されます(図1a)。

次のFPGAファブリックの拡張には、ブロックRAM(BRAM)と呼ばれるSRAMのブロック、位相ロックループ(PLL)、クロックマネージャなどが含まれています(図1b)。デジタル信号処理(DSP)ブロック(DSPスライス)と高速シリアライザ/デシリアライザ(SERDES)ブロックを追加することもできます(図1c)。

図1:プログラマブルファブリックとコンフィグレーション可能な汎用IO(GPIO)のみが含まれる最も簡易なFPGA(a)、基盤のファブリックをSRAMブロック、PLL、クロックマネージャで拡張する各種アーキテクチャ(b)、DSPブロックとSERDESインターフェース(c)、およびハードプロセッサコアと周辺機器(d)。(画像提供:マックス・マックスフィールド氏)

CAN、I2C、SPI、UART、USBなどのペリフェラルインターフェース機能はプログラマブルファブリックにソフトコアとして実装できますが、多くのFPGAではハードコアとしてシリコンに組み込まれています。同様に、マイクロプロセッサをプログラマブルファブリックにソフトコアとして、またはシリコンにハードコアとして実装できます(図1d)。各FPGAが提供する機能や容量は、対象となる市場やアプリケーションに応じて異なります。

Altera(Intelが買収)、Atmel(Microchip Technologyが買収)、Lattice Semiconductor、Microsemi(Microchip Technologyが買収)、Xilinxなど、多くのFPGAベンダーが存在します。

これらのベンダーは、すべて複数のFPGAファミリを提供しています。システムオンチップ(SoC)のFPGA(ハードプロセッサコアを含む)を提供しているベンダーや、宇宙などの高放射線環境を対象にした放射線耐性デバイスを提供しているベンダーもあります。

それぞれ異なるリソースを提供する多くのファミリが存在するため、作業に最適なデバイスをすぐに選択するのは難しい場合があります。ここでは、Lattice Semiconductorが提供しているデバイスファミリと設計ツールに焦点を当てます。

Lattice Semiconductor FPGAの概要

Lattice SemiconductorのFPGA製品は小規模から中規模まで多岐にわたり、急拡大している通信、コンピューティング、産業、自動車、コンシューマ市場で、エッジからクラウドまでネットワークにおける顧客の問題に対処する低電力デバイスに焦点を当てています。

Latticeでは、主に次の4つのFPGAファミリを提供しています。

・iCE(世界最小の超低電力FPGAと呼ばれている)

・CrossLinkとCrossLinkPlus(高速ビデオおよびセンサアプリケーション向け)

・MachXO(ブリッジング、拡張、プラットフォーム管理とセキュリティアプリケーション向け)

・ECP(コネクティビティと加速アプリケーションを対象とした汎用デバイス)

・CrossLinkとCrossLinkPlus(高速ビデオおよびセンサアプリケーション向け)

・MachXO(ブリッジング、拡張、プラットフォーム管理とセキュリティアプリケーション向け)

・ECP(コネクティビティと加速アプリケーションを対象とした汎用デバイス)

Latticeは、Lattice Diamond Software(CrossLink/CrossLinkPlus、MachXO、ECPデバイス向け)とLattice Radiant Software(iCE FPGAと将来のアーキテクチャ向け)に加え、LatticeMico(ソフトマイクロプロセッサベースの設計を作成するためのグラフィカルツール)とLattice sensAI StackとNeural Network Compiler(人工知能(AI)と機械学習(ML)設計用)などの設計や検証ツールスイートも多数提供しています。

従来型:ECP FPGA

LatticeのECPデバイスは、多くの設計者が「従来型」FPGAと見なしているデバイスです。これらのデバイスには、10mm×10mm、0.5mmピッチパッケージに最大85,000kの4入力ルックアップテーブル(LUT)を含めることができます。このデバイスでは、0.25W未満のシングルチャンネルのプロトコルに依存しないSERDES機能と0.5W未満のクワッドチャンネルSERDES機能により、静的/動的低電力消費を実現します。

SRAMブロック、デジタル信号処理(DSP)ブロック、位相ロックループ(PLL)、クロックマネージャに加え、ECP FPGAでは、LVCMOS 33/25/18/15/12、XGMII、LVTTL、LVDS、Bus-LVDS、7:1 LVDS、LVPECLおよびMIPI D-PHY入力/出力インターフェースに対するプログラム可能なI/Oサポートが強化されています。

ECP FPGAのコンフィグレーションセルはSRAMベースです。つまり、他のすべてのSRAMベースのFPGAと同様に、電力がシステムに供給されるときにコンフィグレーションを外部ソース(フラッシュメモリデバイス、マイクロプロセッサ、マイクロコントローラなど)からロードする必要があります。

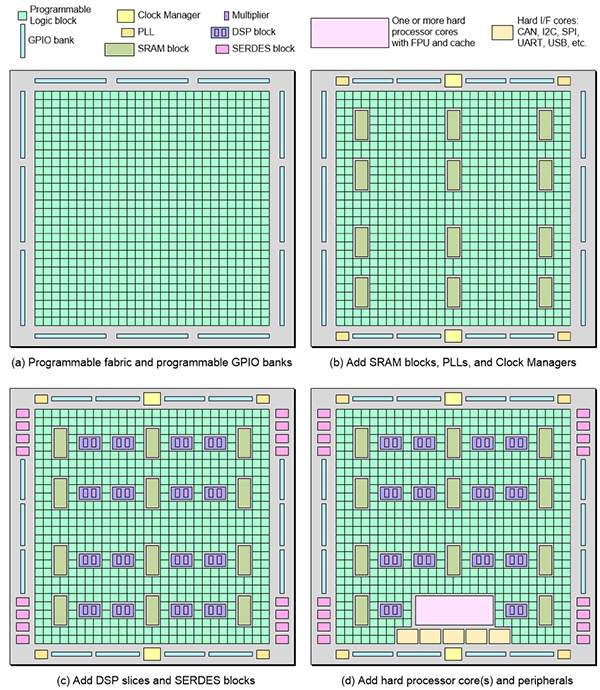

ECPデバイスの良い例が、 10mm×10mmパッケージのLFE5UM5G-25F-8BG381C ECP5 5G SERDES対応FPGAです。設計者がECP5 FPGAファミリの機能を効率よく調査、実験できるように、Latticeは対応するECP5-5G開発ボードとしてLFE5UM5G-85F-EVNも提供しています(図2)。

図2:ECP5評価ボードは、 多くのロジック、I/O、5G SERDES、拡張ヘッダを備えるプロトタイピングボードです。(画像提供:Lattice Semiconductor)

小型で強力:Lattice iCE FPGA

iCEデバイスは最小のFPGAで、1.4mm×1.4mmパッケージで18のI/Oを提供するファミリ最小の製品です。iCE FPGAは、最大5kの4入力LUT、最大128KビットのLatticeの組み込みsysMEM BRAM、1MビットのシングルポートRAM(SPRAM)、高速DSPブロック、およびカスタマイズ可能なI/Oを使用する柔軟な論理アーキテクチャを提供します。

iCE FPGAは小型で、ほとんどのアプリケーションに対してスリープ電流が75µA、アクティブ電流が1~10mAと低電力ですが、機能は強力です。たとえば、常時オンのインテリジェンスをエッジに導入するために必要なパターンマッチング用の人工ニューラルネットワーク(ANN)を実装することができます。

iCE FPGAのコンフィグレーションデータは、不揮発性メモリ(NVM)に保存されます。つまり、これらのデバイスはOne-Time Programmable(OTP)です。前に説明したように、iCE FPGAにはSRAMベースのコンフィグレーションセルも含まれています。

Lattice Radiantには、次のようなさまざまな機能が用意されています。

開発時に、外部からSRAMベースのコンフィグレーションセルを直接ロードして設計をテストできます。設計はコミットされると、NVMにロードできます。デバイスの電源がオンになると、NVMに保存されているコンフィグレーションが超並列方式でSRAMベースのコンフィグレーションセルに自動的にコピーされます。

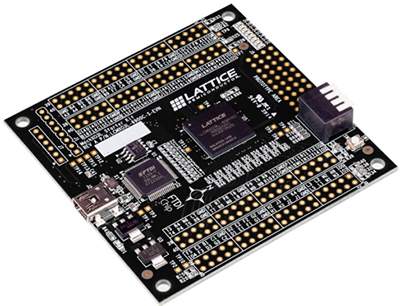

iCEデバイスの例として、ICE40UL1K-SWG16ITR1K iCE40 UltraLiteがあります。これは(この記事の投稿時点で)世界最小のフォームファクタであり、1.4mm×1.4mmパッケージで42µWの静的電力を提供します。代表的な開発ボードはHM01B0-UPD-EVN Himax HM01B0 UPduinoシールドやsensAIモジュール式デモンストレーションボードです(図3)。

図3:Himax HM01B0 UPduinoシールドは、感覚入力のようにビジョンとサウンドを使った人工知能(AI)を実装するための開発キットです。(画像提供:Lattice Semiconductor)

このキットは、iCE40 UltraPlus FPGAの性能とI/O機能を備えたArduinoフォームファクタの迅速なプロトタイピング開発ボードであるUPduino 2.0ボードをベースにしています。また、Himax HM01B0低消費電力画像センサモジュールと2つのI2Sマイクロフォンも付属しています。

特殊用途:CrossLink FPGAとCrossLinkPlus FPGA

CrossLinkとCrossLinkPlusファミリは、プログラマブルロジックと相当量のI/O機能に加え、産業および車載用アプリケーションで幅広く使用されている仕様の強化バージョンを含む特殊なFPGAです。

これらのファミリでは、Mobile Industry Processor Interface(MIPI)D-PHY高速データ通信物理層基準、Camera Serial Interface 2(CSI2)、Display Serial Interface 2(DSI2)コアなどが、すべて寸法6mm×6mm(CrossLink)と3.5mm×3.5mm(CrossLinkPlus)のパッケージに含まれています。

iCE FPGAと同様に、CrossLinkデバイスのコンフィグレーションデータはOTP NVMに保存され、開発中にテスト用として直接ロードできるSRAMベースのコンフィグレーションセルも含まれます。設計がコミットされると、電源投入時に設計はNVMにロードされて、超並列方式でSRAMベースのコンフィグレーションセルに自動的にコピーされます。

比較すると、CrossLinkPlusデバイスのコンフィグレーションセルはフラッシュベースであるため、これらのデバイスは必要に応じて再プログラムすることができます。また、10ms未満の瞬時オン機能もあります。

CrossLinkデバイスの例として、5,936の論理要素/セル、184,320の合計RAMビット、および37のI/Oを使用するLIF-MD6000-6JMG80Iがあります。組み込みビジョンの設計を始める場合、設計者はLF-EVDK1-EVN組み込みビジョン開発キットを使用してCrossLinkベースのMIPI入力とECP5 FPGA処理を結合し、組み込みビジョンの設計を試作できます。

図4:LatticeのLF-EVDK1-EVN組み込みビジョン開発キットは、組み込みシステムの設計者向けに、さまざまなイメージセンサやディスプレイとインターフェースする入出力ボードを組み合わせる機能を含むソフトウェアとハードウェアプロトタイピング環境を提供します。(画像提供:Lattice Semiconductor)

I/Oおよび電源管理機能:MachXO FPGA

数百のI/Oを持つMachXO FPGAは、GPIO拡張、インターフェースブリッジング、電源管理機能を必要とする幅広いアプリケーションに最適です。最新のファミリ製品はNISTに準拠した設計で、システムのハードウェアとファームウェアの安全を確保するセキュリティ機能が追加されています。

MachXO FPGAには、電源レールの状態に関係なくI/Oに電圧を供給できる「ホットソケット」などの機能を含む、堅牢なGPIOセットが含まれています。さらに、ほとんどのFPGA入力はデフォルトでプルアップ状態に設定されていますが、MachXO入力のデフォルトはプルダウンであるため、MachXO入力は機能アプリケーションを制御するのに適しています。

10ms未満の瞬時オン機能を備えるMachXO FPGAは、システムの電源投入や切断時に他のコンポーネントを管理し、シーケンシングする「最初にオン、最後にオフ」制御デバイスに最適なソリューションを提供します。

MachXOデバイスのコンフィグレーションデータは、フラッシュメモリに保存されます。MachXOデバイスには、SRAMベースのコンフィグレーションセルも含まれています。デバイスの電源がオンになると、フラッシュに保存されているコンフィグレーションデータが超並列方式でSRAMベースのコンフィグレーションセルに自動的にコピーされます。さらに、デバイスの稼働中に新しいコンフィグレーションをフラッシュにロードできるため、この新しいコンフィグレーションが最適なタイミングでSRAMセルにコピーされます。

MachXOデバイスの良い例は、9,400の論理要素/セル、442,368の合計RAMビット、206のI/Oを備えるLCMXO3LF-9400C-6BG256Cです。代表的な開発ボードは、LCMXO3LF-6900C-S-EVN MachXO3スターターキット(MachX03Lバージョン)です。

図5:MachXO3Lスターターキットは、基礎的なブレイクアウトボードで、MachXO3Lベース設計の簡単な評価および開発を可能にします。(画像提供:Lattice Semiconductor)

このキットボードでは、外部ブートやデュアルブート機能の評価にSPIフラッシュを使用できます。LCMXO3L-DSI-EVN MachXO3L DSIブレイクアウトボードはMIPI DSIやCSI2 I/Oの評価用に推奨され、LCMXO3L-SMA-EVN MachXO3L SMAブレイクアウトボードは、高速差動I/Oの評価用に推奨されます。

Lattice Semiconductor FPGAを使用した設計と開発

FPGAでの開発に使用される最も一般的な手法の1つが言語駆動設計(LDD)です。この手法では、VerilogやVHDLなどのハードウェア記述言語(HDL)を使用してレジスタ転送レベル(RTL)と呼ばれる抽象レベルで設計の意図を表します。

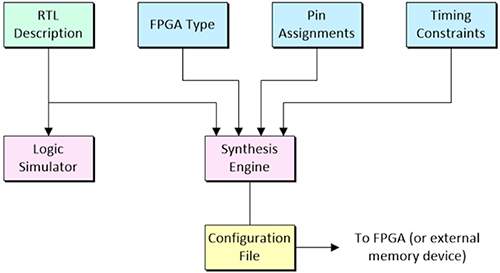

論理シミュレーションによる検証の後に、この表現は、ターゲットのFPGAタイプ、ピン割り当て、タイミング制約(入力から出力への最大遅延など)などの追加の情報とともに、合成エンジンに送られます。合成エンジンからの出力はコンフィグレーションファイルです。このファイルはFPGAに直接ロードされるか、SRAMベースのFPGAの場合は外部メモリデバイスにロードされます(図6)。

図6:論理シミュレーションによる検証の後、RTL設計の説明が、FPGAタイプ、ピン割り当て、タイミング制約などの追加の設計詳細とともに合成エンジンに送られます。合成エンジンからの出力はコンフィグレーションファイルで、FPGAに直接ロードされるか(NVMまたはフラッシュベースのデバイスの場合)、外部メモリデバイスにロードされます(SRAMベースのデバイスの場合)。(画像提供:マックス・マックスフィールド氏)。

Lattice Diamondはこのツールクラスに分類され、CrossLink、MachXO、ECPデバイス向けの完全なGUIベースのFPGA設計と検証環境を提供します。Lattice Diamondと同様に、Lattice Radiantも完全なGUIベースのFPGA設計と検証環境を提供しますが、Lattice RadiantはiCE FPGAと将来のアーキテクチャを対象にしています。

Lattice Radiantには、次のようなさまざまな機能が用意されています。

・業界標準IEEE 1735知的財産(IP)の暗号化と、最大の互換性を実現するSynopsys Design Constraints(SDC)

・統合型のツールセット環境で設計ナビゲーションとデバッグが容易

・新しいプロセスツールバーにより簡単な「ワンクリック」設計実装が可能

・完全な閉ループの物理設計から論理設計への実装によるクロスプロービング

・開発者とサードパーティのIPプロバイダが暗号化されたIPを配布するのに適したフォームにパッケージングすることができるIPパッケージング機能

・統合型のツールセット環境で設計ナビゲーションとデバッグが容易

・新しいプロセスツールバーにより簡単な「ワンクリック」設計実装が可能

・完全な閉ループの物理設計から論理設計への実装によるクロスプロービング

・開発者とサードパーティのIPプロバイダが暗号化されたIPを配布するのに適したフォームにパッケージングすることができるIPパッケージング機能

LatticeMicoシステム開発ツール

Latticeは、LatticeMico8とLatticeMico32の2つのソフトプロセッサコアを提供しており、どちらもFPGAのプログラマブルファブリックに実装することができます。

LatticeMico8は、プログラマブルロジックデバイスのMachXO2ファミリに対して最適化され、完全にテストされた8ビットマイクロコントローラです。また、LatticeMico8はFPGAの他のファミリのリファレンス設計として使用することもできます。

マイクロコントローラコアは、完全な18ビット幅の命令セットと32の汎用レジスタを結合し、幅広い機能セットを維持しながら、消費するデバイスリソースは最小限(最小構成では200未満のLUT)に抑えます。

LatticeMico32は、32ビットのハーバードRISCアーキテクチャマイクロプロセッサです。32ビット幅の命令セットと32の汎用レジスタを結合することで、LatticeMico32は、さまざまな市場に適したパフォーマンスと柔軟性を提供します。

RISCアーキテクチャを使用することで、コアは幅広いアプリケーションセットに必要なパフォーマンスを維持しながら、使用するデバイスリソースを最小限に抑えます。マイクロプロセッサシステムの開発を迅速化するために、いくつかの最適なWISHBONEコントローラに互換するペリフェラルコンポーネントをLatticeMico32に統合できます。

LatticeMicoシステム開発ツールのグラフィカルユーザーインターフェースを使用して、LatticeMicoプロセッサコアや周辺機器をドラッグ&ドロップし、それらをバスに接続して、コンポーネントごとにさまざまなパラメータ(プロセッサのアドレス空間内の場所など)を定義することができます。

システムが定義された後、このツールを使ってシミュレートや合成される対応のRTLを自動的に生成することができます。また、プロセッサコアで実行されるソフトウェアを生成できるツールもあります。

機械学習ツール:Lattice sensAI StackとNeural Network Compiler

機械学習(ML)と人工知能(AI)アプリケーションは、現在幅広い組み込みシステムと、産業用IoT(IIoT)など、あらゆるIoTに導入されています。

Lattice sensAI Stackには、モジュール式ハードウェアプラットフォーム、デモンストレーション例、リファレンス設計、ニューラルネットワークIPコア、開発用ソフトウェアツール、カスタム設計サービスを含む、FPGAベースのML/AIソリューションを評価、開発、導入するために必要なあらゆるものが含まれています。このスタックは、コンシューマや産業用IoTアプリケーションにおける柔軟な機械学習推論の開発者向けに、市場の投入への時間を短縮する設計になっています。

Latticeの畳み込みニューラルネットワーク(CNN)アクセラレータIPコアは、ディープニューラルネットワーク(DNN)用の計算エンジンです。このエンジンは畳み込みニューラルネットワーク用に最適化されているため、分類またはオブジェクトの検出やトラッキングなど、ビジョンベースのアプリケーションに使用できます。CNN IPコアは、必要な計算を実行できるため、追加のプロセッサは不要です。

一方、Lattice Neural Network Compilerを使用すると、設計者は一般的な開発フレームワーク(TensorFlow、Caffe、Kerasなど)で作成されたニューラルネットワークを取得して、それらをLattice CNNおよびコンパクトなCNNアクセラレータIPコアでの実装用にコンパイルできます。

まとめ

プロセッサとFPGAの組み合わせ、FPGA単独、またはファブリックの一部としてハードプロセッサコアを強化するFPGAによって最適な処理ソリューションが得られることがよくあります。

FPGAは1つのテクノロジとしてここ数年で急速に進化しており、柔軟性、処理速度、および電力における現在の多くの設計要件に対応し、インテリジェントインターフェースからマシンビジョンやAIまで幅広いアプリケーションに活用することができます。

ここで説明したように、Lattice SemiconductorのFPGAは小規模から中規模まで多岐にわたり、急拡大している通信、コンピューティング、産業、自動車、コンシューマ市場で、エッジからクラウドまでネットワークの問題に対処する低電力デバイスに焦点を当てています。

Latticeは、言語ベースの設計から、グラフィカルプロセッサベースの設計、機械学習や人工知能アプリケーションに特化した設計まで、複数の設計フローに対応する設計および検証ツールスイートもいくつか提供しています。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、Digi-Key Electronicsの意見、信念および視点またはDigi-Key Electronicsの公式な方針を必ずしも反映するものではありません。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、Digi-Key Electronicsの意見、信念および視点またはDigi-Key Electronicsの公式な方針を必ずしも反映するものではありません。

このページのコンテンツはDigi-Key社より提供されています。

英文でのオリジナルのコンテンツはDigi-Keyサイトでご確認いただけます。

Digi-Key社の全製品は 1個からマルツオンラインで購入できます

ODM、OEM、EMSで定期購入や量産をご検討のお客様へ【価格交渉OK】

毎月一定額をご購入予定のお客様や量産部品としてご検討されているお客様には、マルツ特別価格にてDigi-Key社製品を供給いたします。

条件に応じて、マルツオンライン表示価格よりもお安い価格をご提示できる場合がございます。

是非一度、マルツエレックにお見積もりをご用命ください。