IoTノードやウェアラブルデバイスが小型化する中で、設計者は、基板のスペース、電力、コストを最小限に抑えるため、それらのマイクロコントローラのオンボードメモリを最大限に活用する必要があります。しかし、メモリ拡張が避けられないこともあります。32ビットコントローラのバス構造をデフォルトで使用する代わりに、アドレスとデータの両方について、高速な333Mb/秒ダブルデータレート(DDR)インターフェースであるHyperBusを検討すべきです。

できるだけ拡張を避けようとしても、開発中にメモリ要件が拡大したために必要になることは少なくありません。あるいは、設計者が将来の拡張ニーズを予測して、単純に将来にわたって有効な設計にしようとすることもあります。

16ビットのデータバスおよびアドレスバスと、それに関連付けられた標準的な32ビットインターフェースの制御ピンと異なり、HyperBusを使用することで、同じバス上でマイクロコントローラで外部フラッシュとRAMをサポートできます。これは、HyperBusインターフェースポートを備えたあらゆるメモリデバイスで機能します。スペースに制約のある用途での、ピン数を抑えたメモリ拡張に効果的な使いやすいインターフェースです。

バスの動作はファームウェアに対して透過的ですが、HyperBusを初めて使用する開発者は、堅牢な設計を実現するために高速バス信号の動作について習熟しておくことが重要です。この記事ではまず、HyperBusの動作について説明します。さらに、このインターフェースを組み込んだマイクロコントローラについて説明し、その効果的な適用と設計テストの方法を紹介します。

HyperBusについて

前述のように、HyperBusはアドレスとデータの両方に高速8ビットDDRインターフェースを使用します。さらに、メモリデバイスごとに、差動クロック、読み出し/書き込みラッチ信号、チップセレクトを使用します。HyperBusは、同じバス上で外部フラッシュとRAMをサポートし、HyperBus互換のペリフェラルインターフェースを使用してあらゆるマイクロコントローラと連携動作します。

HyperBusは、バス上の1つのホストマスタが1つ以上のスレーブメモリデバイスとインターフェース接続する、マスタ/スレーブインターフェースとして設定されます。HyperBusフラッシュメモリデバイスはHyperFlash™と呼ばれ、HyperBus DRAMメモリデバイスはHyperRAM™と呼ばれます。

このバスは、指定されたCKおよびCK#信号による差動クロックを使用します。HyperBusはDDRインターフェースの一種であるため、データはクロックの立ち上がりエッジと立ち下がりエッジの両方で転送されます。クロックはマスタによってのみ駆動され、その周波数は、バス上で最も低速のHyperBusメモリの定格クロック周波数を超えることはありません。

双方向8ビットバスにはDQ[0-7]が指定されており、マスタデバイスとスレーブデバイスの間でアドレス、データ、コマンドを転送します。データの受け取りには、双方向の読み出し/書き込みデータストローブ(指定のRWDS)信号が使用されます。RWDSは、データを読み取るあらゆるデバイスによって制御されるため、マイクロコントローラホストがHyperRAMにデータを書き込む場合、そのHyperRAMがRWDS信号を制御します。DQ[0-7]で読み出されるデータは、クロックの両方のエッジに合わせてアライメントが行われます。

各スレーブデバイスは、アクティブローのチップセレクト、指定のCS0#、CS1#、CS2#などを使用して選択されます。任意の時点でアクティブになるチップセレクトは1つだけです。すべてのバストランザクションは、指定のチップセレクトがHIGHからLOWに推移することで開始されます。すべてのバストランザクションは、指定のチップセレクトがLOWからHIGHに推移することで終了します。開発者は、アクティブなチップセレクトが常に1つであることを確認する必要があります。そうしないと、複数のHyperBusスレーブデバイスが同時にRWDSを処理し、データの破損につながる可能性があります。

アクティブローのハードウェアリセット信号(指定のRESET#)は、マスタによって処理されます。LOWのとき、その信号に関連付けられた外部HyperBusメモリデバイスの状態がリセットされます。これには、メモリデバイスの内部設定レジスタのリセットも含まれます。ただし、HyperBusメモリデバイスの内部メモリの状態には影響しません。ほとんどのHyperBusマスタマイクロコントローラインターフェースでは、RESET#はHyperBusペリフェラルには含まれず、汎用I/Oピンとなります。HyperBusスレーブデバイスは、RESET#ピンで弱プルアップが設定されているため、フローティング状態のままになるとHIGH状態にプルアップされます。

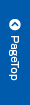

マイクロコントローラ上のHyperBus互換のペリフェラルはすべて、HyperBusの仕様に準拠している必要があります。HyperBus互換のマイクロコントローラの例として、STMicroelectronicsのSTM32L4R9 Arm® Cortex®-M4Fがあります(図1)。STM32L4R9には、2MB内蔵フラッシュメモリと640KB SRAMが搭載されています。HyperBusインターフェースとして設定できる2つのOctoSPIインターフェースを含め、多様なペリフェラルがあります。

図1:STMicroelectronicsのSTM32F4L9マイクロコントローラは、FPU内蔵Arm® Cortex®-M4コアをベースとし、図ではオレンジ色で示されている2つのHyperBus互換インターフェースを備えている。(画像提供:STMicroelectronics)

STM32L4R9は、マイクロコントローラのAHBバスアドレス空間にマップされたメモリとしてHyperBus外部アドレスにアクセスするため、コアは内部メモリと同様に外部メモリに対する読み出しと書き込みにアクセスします。外部メモリデバイスが設定された後は、HyperBusはコアに対して透過的に動作します。

HyperBusのメモリはすべて16ビット長のメモリであるため、STM32L4R9からのすべてのアクセスは16ビット長メモリ境界にアライメントされる必要があります。STM32L4R9マスタからのデータアクセスは、16ビットまたは32ビットのどちらでもかまいませんが、これも境界に合わせてアライメントされる必要があります。

HyperBusでの一般的な読み出しまたは書き込みのトランザクションは、対応する2つの8ビット長1/2クロックサイクルデータ転送(シングルエンド方式のクロックエッジまたは差動方式のクロッククロッシングごとに1つずつ)による、一連の16ビットの1クロックサイクルデータ転送で構成されます。読み出しと書き込みのトランザクションでは常に、完全な16ビット(ワード)データが転送されます。読み出しデータ(ワード)には、常に有効なバイトが2バイト含まれます。書き込みデータ(ワード)では、書き込みバーストで個別のバイトが書き込まれるのを防ぐために、1バイトまたは2バイトがマスクされることがあります。HyperBusプロトコルでは、バイト転送はサポートされておらず、ビットバンディングなどのビット操作もサポートされていません。

STM32L4R9のHyperBus互換ポートには、それぞれ専用に256MBのアドレス空間が割り当てられており、次のようにメモリにマッピングされています。

HyperBus1(OctoSPI1)0x90000000~0x9FFFFFFF

HyperBus2(OctoSPI2)0x70000000~0x7FFFFFFF

アクセス先のHyperFlashまたはHyperRAMメモリデバイスの内部アドレスは、上述の位置のベースメモリアドレスからのオフセットになります。たとえば、STM32F4L9がメモリ位置0x90000047から読み出す場合、HyperBus1上でアクセスされるメモリデバイスのメモリ位置0x0047に格納された値をリードバックします。

HyperBusの仕様を開発したのはCypress Semiconductorで、同社はHyperBusメモリの製品ラインを提供しています。CypressのS26KS512SDPBHI020 64MB×8 HyperFlashメモリは、OctoSPIポートの1つと簡単にインターフェース接続できます。最大32の16ビットワードで構成されるラップバーストアクセスをサポートしています。S26KS512 HyperFlashは、最大166.6MHzのクロックレートにより、フル333MB/秒の連続読み出しレートをサポートします。STM32L4R9では、OctoSPIの最大クロックが60MHzであり、あらゆる外部HyperBusメモリを最大120MB/秒で読み出すことができます。

STM32L4R9では、Cortex-M4システムバスを介してHyperFlashにアクセスする場合、このフラッシュメモリから直接コードを実行できます。OctoSPIをコードメモリ用に使用する場合、外部メモリから次のメモリアドレスを読み込む統合プリフェッチバッファを使用して、eXecute In Place(XIP)がサポートされます。

Cypress SemiconductorのS27KS0641DPBHI020 8MB×8 HyperRAMメモリは、STM32L4R9データメモリを拡張できるセルフリフレッシュDRAMです。最大64の16ビットワードで構成されるラップバーストアクセスをサポートしています。S27KS0641 HyperRAMも、最大333MB/秒の連続読み出しレートをサポートしており、STM32L4R9によって最大120MB/秒で読み出すことができます。

HyperBusメモリとのインターフェース接続

STM32L4R9には2個のHyperBus互換ポートがあり、それぞれ個別にHyperRAMとHyperFlashの外部メモリデバイスにインターフェース接続できます(図2)。RESET#信号はオプションであり、この図には示されていません。CypressのHyperFlashとHyperRAMの両方を使用することで、プリント基板のサイズや設計の複雑さに関する影響を最小限に抑えて、STM32L4R9の内部メモリを簡単に拡張できます。

図2:STM32L4R9には2個のHyperBus互換ポートがあり、それぞれ個別にHyperRAMとHyperFlashの外部メモリデバイスにインターフェース接続できる。(画像提供:STMicroelectronics)

レイアウトにとって最も重要な信号は、DQ[0-7]とRWDSです。性能を最大限に発揮するためには、プリント基板上のマイクロコントローラとメモリの間でこれらの信号の距離をできるだけ短くする必要があります。

差動クロック信号CKとCK#は、信号の長さに合わせて一定の距離を置いて隣接させる必要があります。可能であれば、EMIを最小限に抑えるためにCKとCK#をVSSガードトレースで保護します。インピーダンスミスマッチを最小限に抑えるには、プリント基板の最上位レイヤ上ですべての信号を引き出し、その下のレイヤに堅牢なVSSレイヤを使用します。

HyperBusを初めて使用する開発者には、プローブのテストポイントを追加することを推奨します。DQ[0-7]とRWDSについては、STM32L4R9マイクロコントローラとメモリデバイスの両方にテストポイントを設けます。STM32L4R9が書き込む際には、メモリデバイスに最も近いテストポイントに注目します。STM32L4R9が読み出す際には、STM32L4R9に最も近いテストポイントに注目します。CK、CK#、CSについては、メモリデバイスの近くにテストポイントを設けます。

DDRインターフェースに関係するクロック周波数が高いため、STM32L4R9とメモリデバイスに対する電圧供給をできるだけクリーンにすることが重要です。電源にノイズが多いと信号タイミングが影響を受けてバス転送エラーが発生する可能性があるため、デカップリングコンデンサの使用を推奨します。HyperBusメモリデバイスには、I/Oピン用に別個の電源とグラウンドがあり、最上位レイヤまたは最下位レイヤで1µFと0.1µFのコンデンサをI/O電源VCCQを追加する必要があります。

HyperBusに対するファームウェアのアクセス

HyperBusメモリデバイスには、デバイスのオプションやタイミングを設定するのに使用されるオンチップレジスタがあります。HyperBusでは、これらをコンフィギュレーションレジスタ(CR)と呼びます。すべてのHyperRAMデバイスには内部CRが搭載されており、特定の動作特性を設定できます。HyperRAM S27KS0641の場合、低電力モード、ラップバースト長、ラップバーストタイプ、R/Wタイミングパラメータ、外部8ビットデータバス上の出力駆動電流をファームウェアで設定できます。

HyperFlashにはCRは搭載されていませんが、ステータスレジスタがあります。S26KS512 HyperFlashには、3つのステータスレジスタが搭載されています。書き込み操作の検証向けに内部エラー訂正コード(ECC)をサポートしており、書き込みエラーを示すECCステータスレジスタがあります。もう1つのレジスタには、あらゆるECCエラーのアドレスが格納されます。3つ目のレジスタは、ECCの訂正および訂正不能なエラーをカウントします。これらのレジスタはすべて読み取り専用です。

HyperBusのトランザクションでは、2種類のメモリ操作がサポートされます。1つ目は、外部メモリの読み出しまたは書き込みです。2つ目は、CRの読み出しまたは書き込み、またはステータスレジスタの読み出しです。

STM32L4L9 OctoSPIをHyperBusポートとして設定すると、コアは、メモリにマッピングされた他のあらゆる位置と同様にメモリにアクセスできます。メモリにマッピングされたHyperBus空間で読み出しまたは書き込みの操作が行われるたびに、マイクロコントローラと外部メモリの間でトランザクションが開始されます。個々のHyperBusトランザクションは、マイクロコントローラが外部メモリデバイスに対するコマンド/アドレス命令を使用して3つの16ビットワードを送信することから開始されます。

このコマンド/アドレスシーケンスは、外部メモリデバイスに対し、操作が読み取りと書き込みのどちらであるか、メモリ空間またはコンフィギュレーションレジスタがアドレス指定されているかどうか、トランザクションがラップバーストまたはリニアバーストのトランザクションであるかどうかを指示し、ターゲットアドレスの行と列を伝えます。これはすべて、動作可能なファームウェアが搭載されたマイクロコントローラに対して透過的である一方で、コマンド/アドレスシーケンスはデバッグの際に重要になります。

HyperBusの使用を開始する

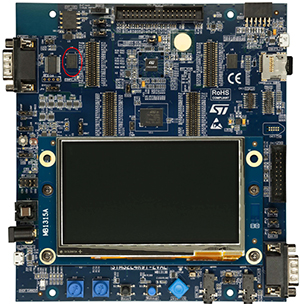

HyperBusプロトコルについて理解したら、特にこのインターフェースを初めて使用する場合には、評価用の基板を使用して試験的なプログラミングを行うことを推奨します。STM32L4R9マイクロコントローラに対応したSTMicroelectronicsのSTM32L4R9I-EVAL評価用基板は、手始めとして最適です(図3)。赤い丸で囲んでいるのがHyperRAMメモリデバイスで、デバイスのテストポイントは右側のヘッダコネクタに配置されています。

図3:STMicroelectronicsのSTM32L4R9I-EVALは、STM32L4R9マイクロコントローラの評価に使用する。赤い丸で囲んだのがHyperRAMメモリデバイスで、デバイスのテストポイントは右側のヘッダコネクタに配置されている。(画像提供:STMicroelectronics)

STM32L4R9I-EVALは、カメラインターフェース、2個のMEMSマイクロフォン、1個のジョイスティック、4.3インチ480 x 272ピクセルのカラーTFT LCDディスプレイなど、幅広い機能を備えています。この評価用基板は、OctoSPIインターフェースをサポートしており、ISSIのプリント基板にはんだ付けされたIS66WVH8M8BLL 64Mb HyperRAMデバイスが搭載されています。

結論

HyperBusプロトコルは、スペースに制約のある用途での、ピン数を抑えたメモリ拡張に適した使いやすいインターフェースです。バスの動作はファームウェアに対して透過的ですが、HyperBusを初めて使用する開発者は、堅牢な設計を実現するために高速バス信号の動作について習熟しておくことが重要です。