タイマIC 555

555というIC

「555」は従来からあるタイマICで手軽に「発振回路」、「タイマ」などに用いられます。電子工作においても、しばしば登場しますので、あらためて「555」について紹介します。

555は「NE555」がオリジナルですが、現在では各メーカーからCMOS版も含めてセカンドソース品が販売されています。

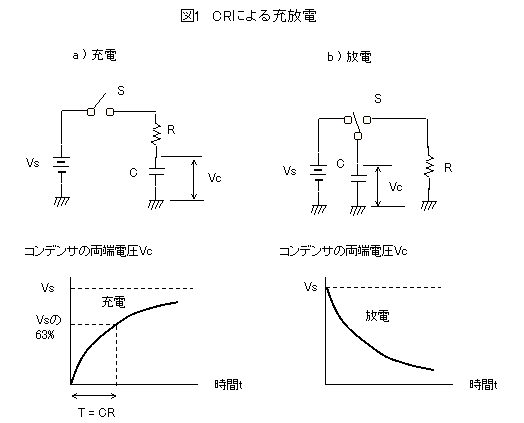

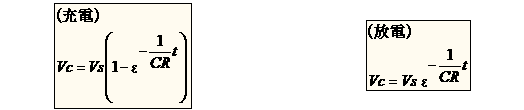

CとRによるタイマの原理

コンデンサCに抵抗Rを通して充放電させると図1のような特性になります。この時のコンデンサCの端子電圧Vcの充放電に要する時間はCとRの組み合わせで決まります。

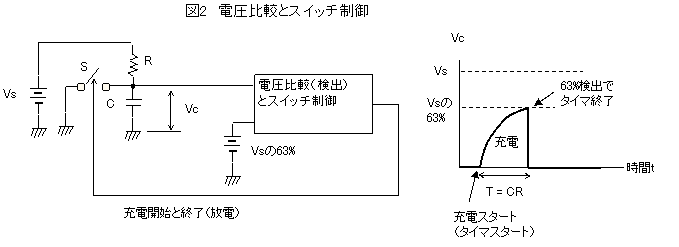

このような放電特性を利用したCRタイマの原理を図2に示します。

図2におけるスイッチSはVcの初期化と充電開始を行い、Sが閉じた状態でVcはゼロです。この状態からSを開けば充電を開始(タイマスタート)し、Vcの値をVsの63%電圧と比較します。

Vcの値が63%に達した時点でスイッチSを閉じてタイマ終了とすれば、タイマ時間TはCRの掛け算で表わされます。

以上の動作はVcの値を63%としましたが、この値は任意でも良く、例えばVcの値をVsの2/3とすれば、

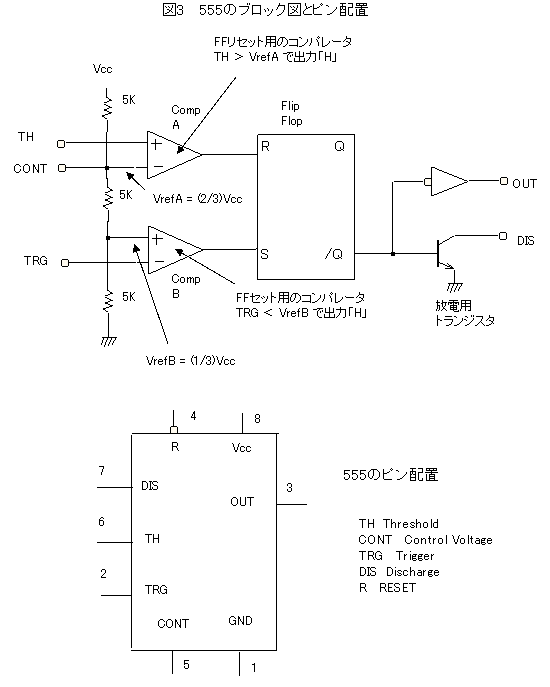

555のブロック図

図3にブロック図とピン配置を示します。

CompAとCompBはコンパレータ(比較器)でそれぞれの端子(プラスとマイナス)の電圧比較を行い、その結果により出力が「H」または「L」になります。

基準となる電圧(Vref)は抵抗3本による電圧分割で、3本の抵抗値は同じ値です。したがって、CompAはVccの2/3、CompBはVccの1/3です。

Flip Flop(以下、FFと略す)はコンパレータ出力を入力とした「RS-Flip Flop」で、出力「/Q」でトランジスタを介して充放電を制御します。

TH > VrefA で出力「H」

CompBはプラス端子が基準電圧入力なので、

TRG < VrefB で出力「H」

RS-FFの論理は表1のように推定されます。

| S | R | Q | /Q |

| H | L | H | L |

| L | H | L | H |

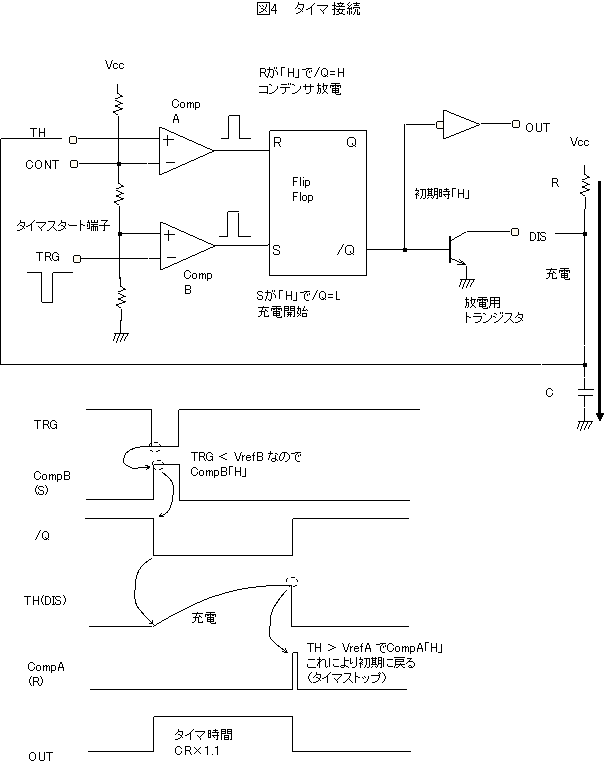

555のタイマ接続

図4にタイマ時の接続を示します。

電源ON後の初期状態では/Qは「H」で、これによりトランジスタがONになりDISおよびTHは「L」です。

TRG端子を「L」にすると TRG < VrefB の条件になりますので、CompB出力は「H」になり、これによりFF出力の/Qが「L」となり、トランジスタもOFFしますので充電が開始されます。

充電によりコンデンサの端子電圧(DIS,TH)が上昇していくと TH > VrefA の条件で今度はCompA出力が「H」となって、/Qは「H」に戻り、タイマストップとなります。

このようにしてタイマ出力OUTが変化し、その時間は前述のように T = CR×1.1 です。

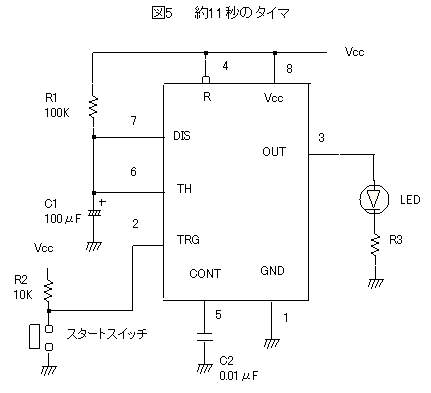

この時の回路を図5に示します。

電源ON後はリセット状態で、スタートスイッチを押すことによりタイマが起動し、約11秒間LEDが点灯します。

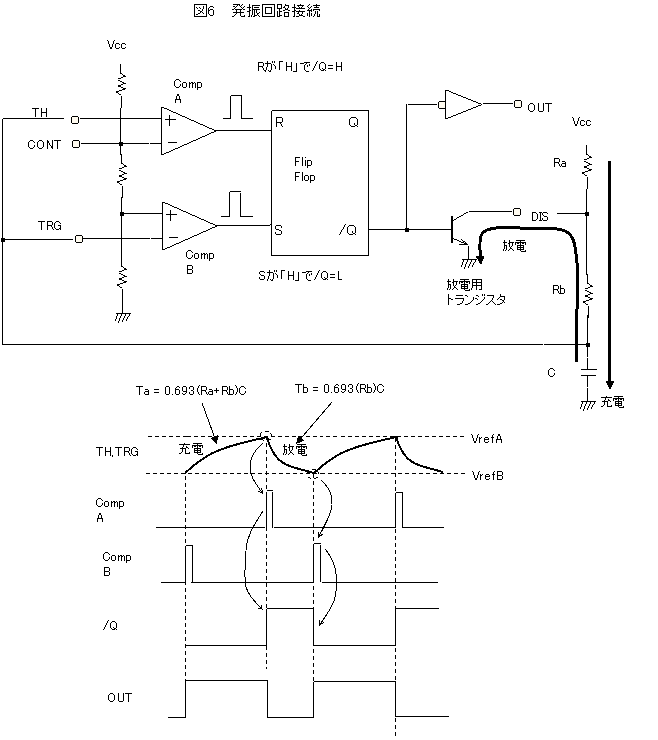

発振回路の接続

発振回路の場合は図6のようにコンデンサCの端子電圧をTHおよびTRGに接続します。

この場合、CompAとCompBは基準となる電圧(VrefA,VrefB)が異なりますから、それぞれのコンパレータ出力は図6のタイミングになります。

つまり、CompAは放電開始、CompBは充電開始を制御しています。これにより充放電を繰り返しますので、これが発振です。

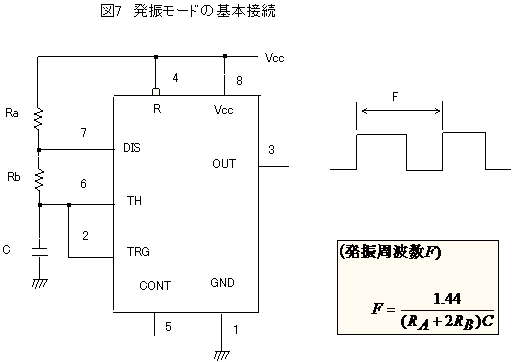

発振モードの基本接続と、この時の発振周波数を図7に示します。

タイマと発振の応用例

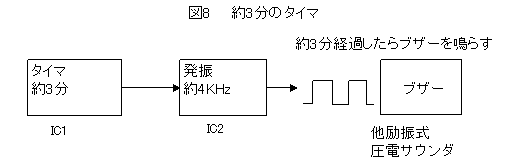

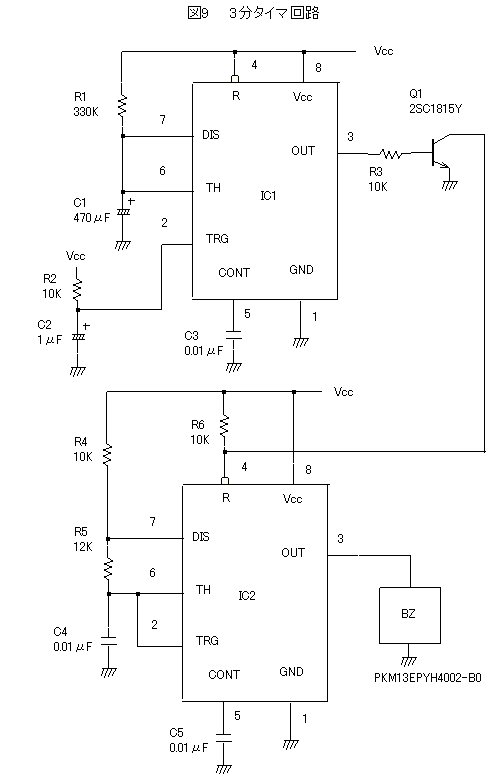

タイマおよび発振を応用した「3分タイマ」を紹介します。図8にブロック図、図9に回路を示します。

IC1が3分タイマ部で図の定数でタイマ時間は約170秒です。抵抗およびコンデンサには誤差がありますから、正確な180秒(3分)にしたい場合はR1を固定抵抗と半固定ボリュームで調整します。

電源ONで「3分タイマ」を起動し、タイマ中のIC1出力は「L」です。この出力をトランジスタを介してIC2のリセット端子に接続します。これにより、タイマ中、IC2はリセット状態で、タイマ終了後にリセットが解除されて、ブザーを鳴らします。

ここでは用いたブザーが「他励振式圧電サウンダですので、必要な周波数(約4KHz)で駆動させます。

555はタイマが1個入りですが、2個入りを用いれば図9のような回路を組む場合、便利です。以上のように基本動作である「タイマモード」および「発振モード」について説明しました。

この他の応用もありますので、詳細は555のデータシートを参照願います。

| 型番 | メーカー | パッケージ | 主な仕様、特徴 |

|---|---|---|---|

| LMC555CN-N | NS | DIP8 | CMOS |

| NE555P(L) | TI | DIP8 | 動作電圧4.5V~16V |

| NE556N | TI | DIP14 | 2回路 |

| UPD5556C | ルネサス | DIP14 | 2回路、CMOS、動作電圧3V~16V |

| SE555P | TI | DIP8 | 動作温度範囲-55℃~125℃ |

555を作ってみる

内部の波形を確認する

前述(図3)のブロック図のように555の内部構成は以下のようになっています。

- コンパレータ 2個

- RS-FF

- インバータ

- トランジスタ

- 抵抗分割による基準電圧

タイマおよび発振回路の動作原理は前述のようになりますが、各ブロックの波形確認を目的として、市販のオペアンプ(コンパレータ)、ロジックIC等を利用して製作しましたので紹介します。

回路その1

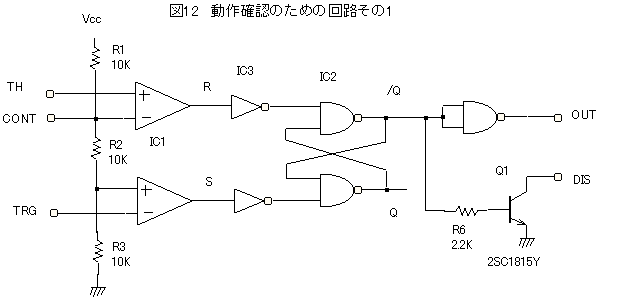

図12に「回路その1」を示します。

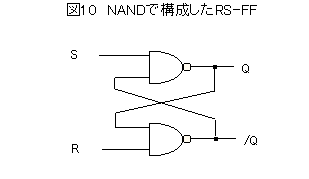

コンパレータはオリジナルの555では「正論理出力」と思われます。図10のRS-FFはNAND-ICの74HC00で構成し、この場合の真理値表を表3に示します。

| S | R | Q | /Q |

| L | L | 不定 | |

| L | H | H | L |

| H | L | L | H |

| H | H | 記憶 | |

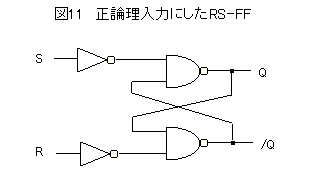

このままですとRS-FFの入力が負論理ですので、これを正論理入力にして論理合わせしたものを図11に示します。

| S | R | Q | /Q |

| H | H | 不定 | |

| H | L | H | L |

| L | H | L | H |

| L | L | 記憶 | |

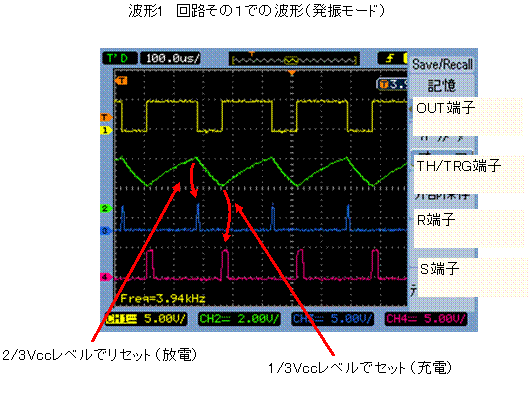

ICが「オペアンプ」、「NOT-IC」、「NAND-IC」の3個が必要ですが、ブレッドボードにて製作し、確認した波形を波形1に示します

「発振モード」での各部の波形で、各基準電圧のポイントでRS-FFをセット/リセットしている様子が分かります。

なお、用いたオペアンプは「LMC6482」です。

回路その2

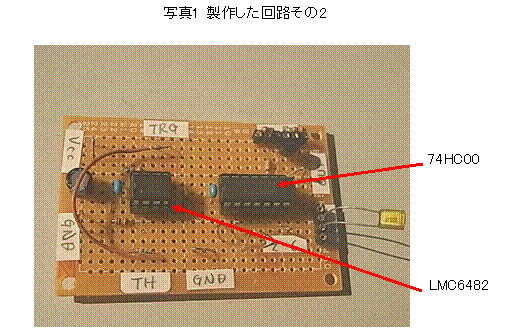

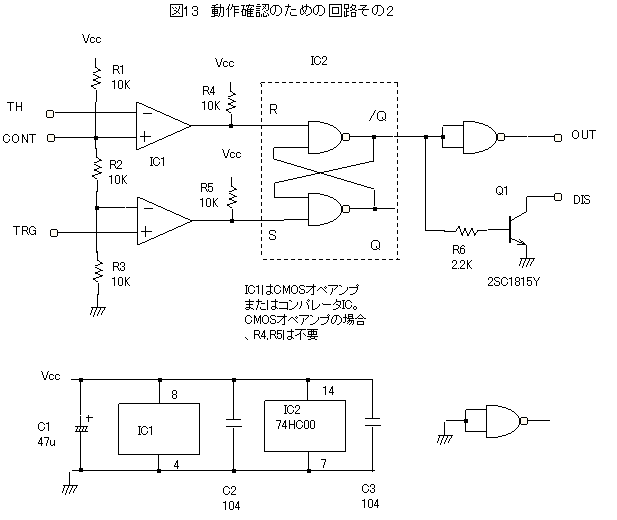

回路その1ではブレッドボードにて確認しましたが、ユニバーサル基板にて製作した回路を図13に示します。回路その1では用いるICが3個でしたので、これを2個で実現したものが回路その2です。コンパレータの論理をRS-FFの負論理入力に対応したもので、NOT-ICを削除しています。(コンパレータの接続に注意)

| 部品番号 | 部品名 | 型番 | メーカー | 数量 |

|---|---|---|---|---|

| C1 | ケミコン 47uF | 1 | ||

| C2,C3 | セキセラ 0.1uF | 2 | ||

| IC1 | オペアンプ | LMC6482AINNOPB | NS | 1 |

| IC2 | NAND IC | SN74HC00AN | TI | 1 |

| Q1 | トランジスタ | 2SC1815Y | 東芝 | 1 |

| R1~R3 | カーボン抵抗 | 10K | 3 | |

| R4,R5 | カーボン抵抗 | 10K | 2 | |

| R6 | カーボン抵抗 | 2.2K | 1 | |

| XIC1 | ICソケット 板ばね8P | 21208NE | Linkman | 1 |

| XIC2 | ICソケット 板ばね14P | 212014NE | Linkman | 1 |

| ユニバーサル基板 | ICB88 | サンハヤト | 1 |

動作確認

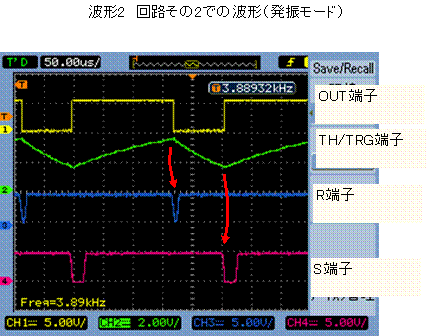

「回路その2」の波形および外観を以下に示します。

波形2のようにR端子およびS端子での波形遅れが若干あります。この遅れは用いるオペアンプ(またはコンパレータ)の特性に左右され、波形2で用いたものはオペアンプのLMC6482です。ちなみにコンパレータIC(例えばLM393等)に替えると波形遅れが少なくなり、最高発振周波数も高くなります。

ただし、コンパレータの場合、「同相入力」の制限があり、LMC6482のような「レール・ツーレール」のほうが電源電圧を変えても使い勝手が良いと思います。