| |

●即答

最良の答えは(d)です.

電源面とグラウンド面の層間隔の小さいプリント基板にデカップリング・キャパシタを実装する際,重要になるのは接続インダクタンスです.これを最小化する必要があります.

(a)に関して,電源ピンとビアを共有したり,能動素子の端子に近づけすぎたりすると,接続インダクタンスは増す可能性があります.

(b)に関して,素子とデカップリング・キャパシタ間の距離は,接続インダクタンスにほとんど影響がありません.

「キャパシタと能動素子間の電荷移動に必要な時間を考慮するなら,デカップリングの対象素子のすぐ近くにキャパシタを実装する必要がある」と主張したい人もいるでしょう.しかし,適度なサイズのプリント基板において,一般的な表面実装型のデカップリング・キャパシタを実装する場合は,この議論は事実に合致しません.

たとえば,電源面とグラウンド面の層間隔が0.3mm,サイズが10cm×10cmのFR-4基板の層内容量(interplane capacitance)は,遷移開始から700psの間に1.3nCの電荷(1Vの電圧変動を仮定)を供給します.適切に接続された状態で,接続インダクタンス が1nH(素子から0cm)のキャパシタは,同時に250pC未満の電荷を供給します.最初は,層内容量が電荷の大部分を供給します.最終的には,SMT(Surface Mount Technology)キャパシタが層内容量よりも多くの電荷を供給しますが,能動素子に非常に近いキャパシタが,他の離れたキャパシタより多くの電荷を供給するわけではないのです.

もちろん,背後にある物理学を理解しないまま,デカップリングのルールに単純に従うのは危険です.層の間隔が小さい基板でも,デカップリング・キャパシタの位置が重要になる場合があります(ただし,近いほど良いとは限らない).

電源面とグラウンド面の層間隔が小さくない場合は,「素子の近く」に実装したデカップリング・キャパシタに頼るのがベストです.この場合,キャパシタの配置は非常に重要です.詳細は,LearnEMCウェブサイトの[EMC Resources]-[EMC Tutorial Articles]-[Circuit Board Decoupling Information]を参照してください.

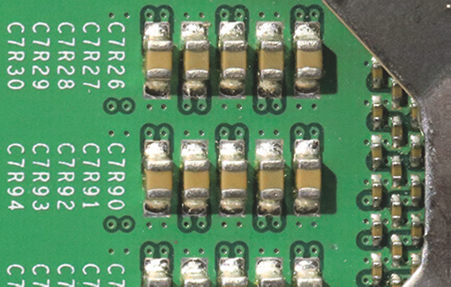

図1 プリント基板上に固めて置かれたデカップリングキャパシタ

|

|