|

|

|

|

|

|

|

【パーツセット付きVOD教材】

[講義683分/568頁] 実習キットで一緒に作る

オープンソースCPU RISC-V入門

~マイコンの基礎から,RISC-V CPUコアとそのシステムの論理設計,

開発環境の構築と使い方,デバッグ,FPGA実装まで~ |

|

|

|

|

|

|

|

|

|

|

| |

|

|

| |

|

|

|

|

|

| |

第0章 セミナ受講前の準備

第1章 マイコンの基礎

第2章 RISC-Vの登場

・RISC-Vのインパクト/RISC-V CPUコアを自作する意味ほか

第3章 メモリとバス

・メモリ・アクセス(SoC/FPGA用SRAM)

・マイコンのバス(mmRISC-0版)

・mmBUSの論理設計とシミュレーション(mmRISC-0版):システム構成/Questaによる論理シミュレーションほか

・ARM標準バスAHB-Lite(mmRISC-1版)

・ARM標準バスAXI4

第4章 RISC-Vアーキテクチャ

・RISC-Vの概要

・RISC-V命令セット・アーキテクチャ

・RISC-Vの例外処理と割り込み

・RISC-VのCSR

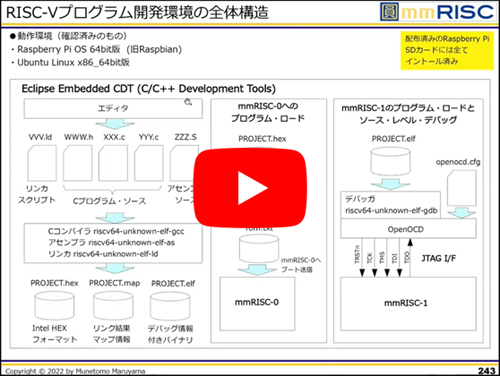

第5章 RISC-Vプログラム開発環境

・C/C++開発環境:RISC-V用Toolchain/Eclipse IDE

・ソース・レベル・デバッグ(mmRISC-1)

・サンプル・プログラム

・RTOSの基礎:FreeRTOSとその概念と使い方

第6章 簡易版RISC-V「mmRISC-0」の設計

・パイプライン型CPUの設計

・周辺機能: GPIO/UART/SPI/I2C/SDRAM/TIME

・FPGAシステム

・論理シミュレーション

・RISC-Vコンプライアンス・テスト

・FPGA実装/動作確認

第7章 実用版RISC-V「mmRISC-1」の設計

・mmRISC-1 CPUコアの論理構造

・周辺機能

・論理シミュレーション

・RISC-Vコンプライアンス・テスト

・FPGA実装

・FPGA動作確認:OpenOCDとGDBの接続/Eclipseによるデバッグ操作

第8章 セミナの終わりに |

|

|

|

|

|

|

|

|

|

|