|

「アプリケーションラボ」は、Digi-Key社のご協力をいただいて、Digi-Key社が公開している新製品や技術情報を日本語でご紹介するWebページです。基礎技術から最新技術まで有益な情報を公開していますので、是非ご活用ください。

今回は、現代の電子機器には不可欠となっている基準周波数を発生させるPLL回路について解説した記事をご紹介します。

■位相ロックループ周波数シンセサイザの基礎

高速シリアル通信バスなどのデータレートが上昇するのに伴って、より高い周波数と、より優れた安定性を持つシステムクロックが必要とされています。水晶発振器は高精度で安定した周波数を発生できますが、高い周波数を得にくい上に周波数が固定されているため、必要となる周波数を発生させたり、周波数を可変したい場合には一般にPLL回路が用いられます。

PLL(phase locked loop)は位相同期回路とも言い、入力信号の位相と出力信号の位相を一致させることで安定した周波数信号を出力させる回路です。PLL回路のしくみは、出力を入力に戻し(ネガティブフィードバック:負帰還)、入力と出力の位相が同期しているかどうかを位相比較器で検出します。同期していない場合はVCO(電圧制御発振器)により、検出した信号を使って周波数を変化させることで出力周波数を一定に保ちます。

出力信号の周波数を変えたい場合、フィードバックさせる出力を分周器でN分の1に分周すると、基準周波数のN倍の周波数が出力されます。整数値で分周する整数N分周方式では周波数を細かく設定することはできませんが、分数値で分周するフラクショナルN方式にするとより細かく出力周波数を変化させることができます。フラクショナルN方式は、基準周波数をM分周して入力し、帰還周波数をN分周することにより、出力周波数をN/M倍にできます。

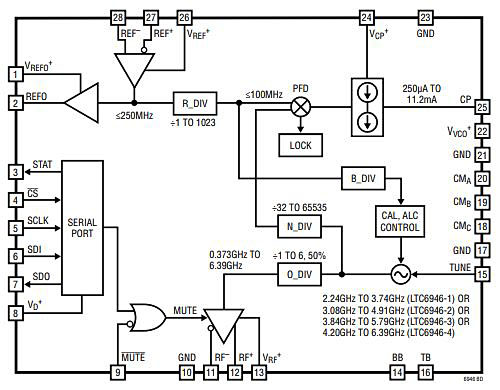

< LTC6946の内部ブロック図 >

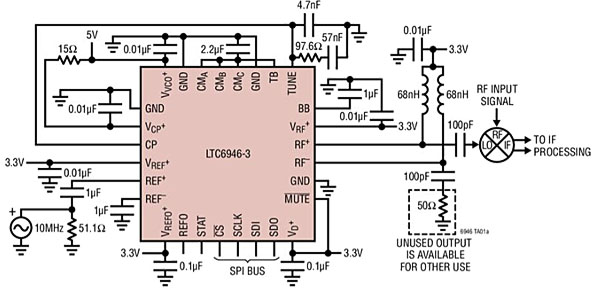

< LTC6946による5.7GHz受信機回路図 >

【アプリケーションラボ】では、整数N型PLLと分数N型PLLのしくみについて詳しく解説し、アナログ・デバイセズ社のPLL ICを紹介しています。LTC6946は、0.37GHz~5.7GHzの周波数を出力できる整数N型PLL ICで、1~1023のN値を設定することができます。チャージポンプ電流は、250μAから11.2mAまでの範囲で調節可能です。また、ADF5610は0.57MHz~14.6GHzの周波数を出力できる分数N型PLL ICですが、整数N型でも動作します。24ビットのシグマデルタ変調器を採用することで、非常に低いスプリアスレベルを実現しています。

ここで解説されているデバイスは、マルツオンラインのウェブサイトで購入できますので、是非参考にしてください。

整数分周方式PLLシンセサイザ

【LTC6946】 ¥1,603.41(税込¥1,763.75) |

|

マイクロ波広帯域PLLシンセサイザ

【ADF5610】 ¥13,071.12(税込¥14,378.23) |

|

下記の2本の解説記事も同時に公開しました。合わせて参考にしてください。

■ダウンコンバージョン効率を最大化するために同期整流式降圧DC/DCコンバータを使用する理由と方法

ダウンコンバージョンとは、高電圧を低電圧に降圧することです。大電力を扱う機器でも電子機器による制御が不可欠になり、電子機器用に低い電圧が必要になります。ここでは、高効率でDC/DC変換するために電子機器に要求される性能と非同期整流式と同期整流式のDC/DCコンバータの違いなどを解説します。

■ソフトウェアによるデバウンスが不適切な場合のスイッチやリレーへのハードウェアデバウンスの実装方法

スイッチを使用すると、きれいにON/OFFが切り替わらずにON/OFFが繰り返される状態(バウンス)が発生します。ここでは、バウンスを防ぐデバウンスに対するソフトウェア的なアプローチとハードウェア的なアプローチについて解説します。

|