特集コーナー

-

接着剤の種類や特長、選び方のポイントを詳しくご紹介します

-

SDカードやUSBメモリなど様々なタイプの製品と特長についてご紹介します

-

工場や研究室、日常生活など液体の漏れやハネには「吸着マット」がおすすめです!

-

最新規格に対応した高速モデルからコストパフォーマンスに優れたものなど様々なタイプのLANケーブルを取り揃えています

-

ブルーシートの種類や選び方、防災での活用法を詳しくご紹介いたします

-

重要な書類や個人情報を安全に処理する「シュレッダー」特集

-

乾電池・充電池の種類やラインナップをご紹介 さらには便利なワンポイント情報も!

-

外出先でも安心!ライフスタイルにぴったりのモバイルバッテリーを見つけてください

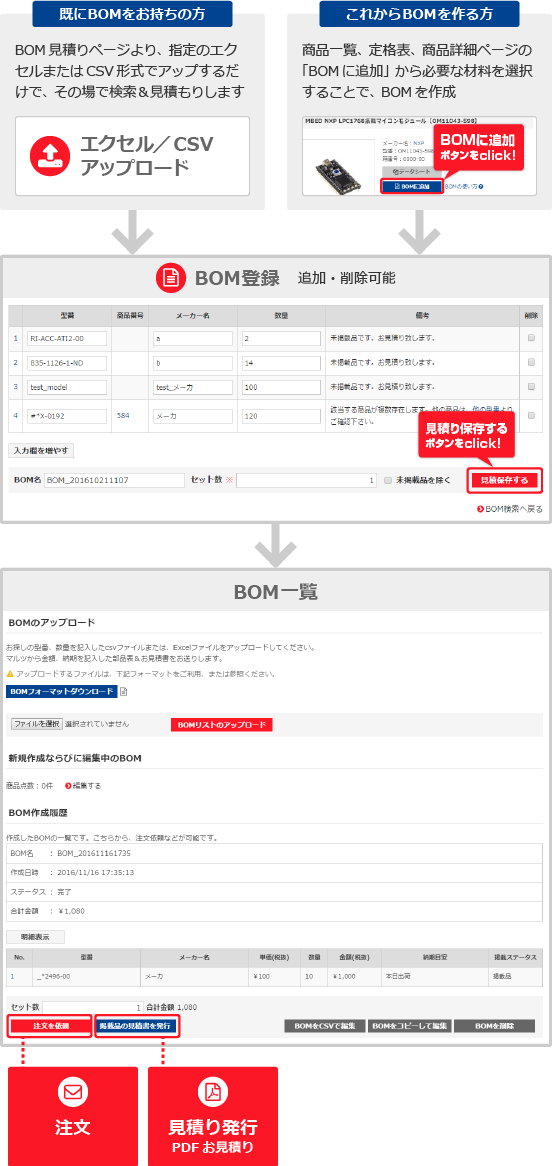

BOM機能を使うと材料の一括検索や見積もり、発注などができます

BOM機能を使うと材料の一括検索や見積もり、発注などができます

【標準梱包形態】

標準の梱包は、Digi-Keyがメーカーから受け取る最小の梱包サイズです。 Digi-Keyの付加価値サービスにより、最小注文数は、メーカーの標準パッケージより少なくなっている場合があります。 梱包形態(リール、チューブ、トレイなど)は、製品を少量梱包に分割する際に変更される場合がありますので、ご了承ください。

【梱包形態】

テープ&リール

テープ&リールは、メーカーから受け取った未修正の連続テープのリールです。 リーダおよびトレーラとしてそれぞれ知られている最初と最後の空のテープの長さは、自動組立装置の使用を可能にします。 テープは、米電子工業会(EIA)規格に従いプラスチックリールに巻き取られます。 リールサイズ、ピッチ、数量、方向およびその他詳細情報は通常、部品のデータシートの終わりの部分に記載されています。 リールは、メーカーによって決定されたESD(静電気放電)およびMSL(湿度感度レベル)保護要件に従って梱包されます。

カットテープ

カットテープは、ご注文部品の数量を正確に含むリール(上記)から切断された長さのテープです。 カットテープにはリーダーやトレーラーが含まれていないため、多くの自動組立機械には適していません。 テープは、メーカーによって決定されたESD(静電気放電)およびMSL(湿度感度レベル)保護要件に従って梱包されます。

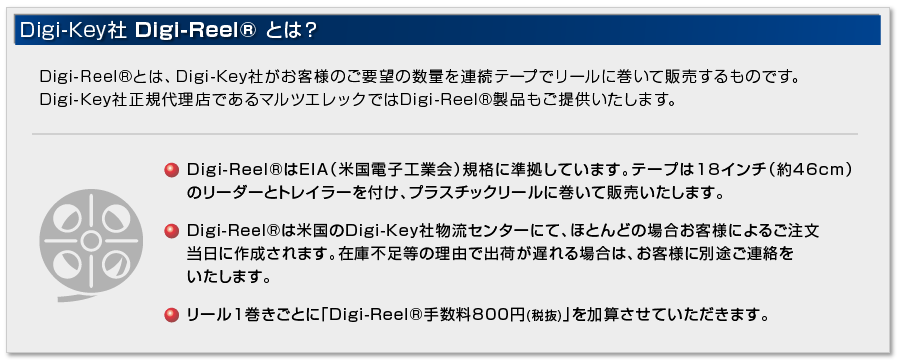

Digi-Reel®

Digi-Reel®はお客様のご要望の数量を連続テープでリールに巻いて販売するものです。Digi-ReelはEIA(米国電子工業会)規格に準拠し、テープには18インチ(約46cm)のリーダーとトレイラーを付けてプラスティックリールに巻いて販売いたします。Digi-Reelはお客様からご注文を頂いてから作成されますが、対応している製品のほとんどは当該製品の在庫から作成され即日出荷されます。在庫不足等の理由で出荷が遅れる場合は、お客様に別途ご連絡を致します。

リール1巻きについて「リーリング手数料」が加算され価格に含まれています。